2017-2018-1 20155215 《信息安全系統設計基礎》第11周學習總結

2017-2018-1 20155215 《信息安全系統設計基礎》第11周學習總結

教材學習內容總結

目標內容:

- 理解虛擬存儲器的概念和作用

- 理解地址翻譯的概念

- 理解存儲器映射

- 掌握動態存儲器分配的方法

- 理解垃圾收集的概念

- 了解C語言中與存儲器有關的錯誤

第十一章:

虛擬存儲器

- 虛擬存儲器是硬件異常、硬件地址翻譯、主存、磁盤文件和內核軟件的完美交互。

將主存看作是一個存儲在磁盤上的地址空間的高速緩存,在主存中只保護活動的區域,並根據需要在磁盤和主存之間來回傳送數據;

保護了每個進程的地址空間不被其它進程破壞。

- 虛擬存儲器是中心的

虛擬存儲器是強大的

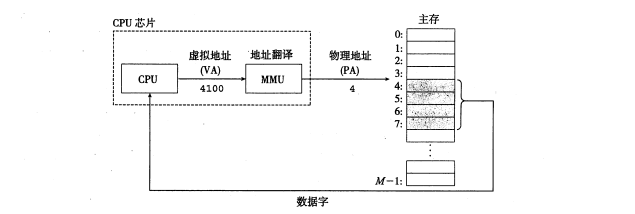

物理和虛擬尋址

- 物理地址PA

- 計算機系統的主存被組織成一個由M個連續的字節大小的單元組成的數組,每字節都有一個唯一的物理地址PA。根據物理地址尋址的是物理尋址。

- 地址翻譯

使用虛擬尋址時,CPU通過生成一個虛擬地址VA來訪問主存,這個虛擬地址在被送到存儲器之前先轉換成適當的物理地址,相關硬件為存儲器管理單元MMU。

DRAM緩存的組織結構

不命中處罰很大

是全相聯的——任何虛擬頁都可以放在任何的物理頁中。

替換算法精密

總是使用寫回而不是直寫。

頁表

頁表:是一個數據結構,存放在物理存儲器中,將虛擬頁映射到物理頁,就是一個頁表條目的數組。

頁表就是一個頁表條目PTE的數組。

PTE:由一個有效位和一個n位地址字段組成的,表明了該虛擬頁是否被緩存在DRAM中。 頁表的組成:有效位+n位地址字段

如果設置了有效位

地址字段表示DRAM中相應的物理頁的起始位置,這個物理頁中緩存了該虛擬頁。

如果沒有設置有效位:

空地址:表示該虛擬頁未被分配

不是空地址:這個地址指向該虛擬頁在磁盤上的起始位置。

缺頁

- DRA緩存不命中稱為缺頁。在不命中發生時,換入頁面的策略稱為按需頁面調度。

顛簸:工作集大小超出了物理存儲器的大小。

- 簡化鏈接:獨立的地址空間允許每個進程的存儲器映像使用相同的基本格式,而不管代碼和數據實際存放在物理存儲器的何處。

- 簡化加載:虛擬存儲器使得容易想存儲器中加載可執行文件和共享文件對象。

- 簡化共享:獨立地址空間為操作系統提供了一個管理用戶進程和操作系統自身之間共享的一致機制。

簡化存儲器分配:虛擬存儲器為向用戶進程提供一個簡單的分配額外存儲器的機制。

- PTE的三個許可位:

- SUP:表示進程是否必須運行在內核模式下才能訪問該頁

- READ:讀權限

WRITE:寫權限

動態存儲器分配

碎片

- 內部碎片:發生在一個已分配塊比有效載荷大的時候易於量化。

外部碎片:發生在當空閑存儲器合計起來足夠滿足一個分配請求,但是沒有一個單獨的空間塊足以處理這個請求時發生

難以量化,不可預測。垃圾收集

教材學習中的問題和解決過程

- 問題1:為什麽每個進程的內核頁表需要單獨分配存儲空間?

問題1解決方案:操作系統開啟分頁後,每個進程有自己獨立的頁目錄與頁表,cpu操作內存會自動將當前線性地址轉換為物理地址(MMU負責),然後再放在地址總線上。所以每個進程即使訪問相同的線性地址會最終對應到不同的物理地址,因為他們的pde與pte不同。

問題2:內部碎片和外部碎片的區別是什麽?

問題2解決方案:要搞清楚內部碎片與外部碎片的區別首先要明白分頁與分段

為了有效的利用內存,使內存產生更少的碎片,要對內存分頁,內存以頁為單位來使用,最後一頁往往裝不滿,於是形成了內部碎片。為了共享要分段,在段的換入換出時形成外部碎片,比如5K的段換出後,有一個4k的段進來放到原來5k的地方,於是形成1k的外部碎片。

代碼調試中的問題和解決過程

- 問題1:暫無

代碼托管

(statistics.sh腳本的運行結果截圖)

上周考試錯題總結

- 有關高速緩存的說法正確的是()

A .

高速緩存的容量可以用C=SEB 來計算

B .

高速緩存容量為2048,高速緩存結構為( 32 ,8,8,32)

C .

直接映射高速緩存要:組選擇、行匹配、字抽取

D .

當程序訪問大小為2的冪的數組時,直接映射高帶緩存中常發生沖突不命中

正確答案: A C D 你的答案: A B

- The following table gives the parameters for a number of different caches. For

each cache, determine the number of cache sets (S), tag bits (t), set index bits (s),

and block offset bits (b)

Image 4.png

A .

第三行S為1

B .

第一行t為24

C .

第二行b為5

D .

第三行s的值為0

正確答案: A C D 你的答案: A D

- 下面代碼中()局部性最差

1 #define N 1000

2 3

typedef struct {

4 int vel[3];

5 int acc[3];

6 } point;

7 8

point p[N];

A .

1 void clear1(point p, int n)

2 {

3 int i, j;

4 5

for (i = 0; i < n; i++) {

6 for (j = 0; j < 3; j++)

7 p[i].vel[j] = 0;

8 for (j = 0; j < 3; j++)

9 p[i].acc[j] = 0;

10 }

11 }

B .

1 void clear2(point p, int n)

2 {

3 int i, j;

4 5

for (i = 0; i < n; i++) {

6 for (j = 0; j < 3; j++) {

7 p[i].vel[j] = 0;

8 p[i].acc[j] = 0;

9 }

10 }

11 }

C .

1 void clear3(point *p, int n)

2 {

3 int i, j;

4 5

for (j = 0; j < 3; j++) {

6 for (i = 0; i < n; i++)

7 p[i].vel[j] = 0;

8 for (i = 0; i < n; i++)

9 p[i].acc[j] = 0;

10 }

11 }

D .

不確定

正確答案: C 你的答案: B

程序中()語句具有良好的局部性

A .

順序

B .

分支

C .

循環

D .

以上都是

正確答案: C 你的答案: A有關局部性原理,說法正確的是()

A .

程序訪問一個向量,步長越小或短,空間局部性越好

B .

局部性有兩種形式:空間局部性,時間局部性

C .

程序訪問一個向量,步長越大空間局部性越好。

D .

硬件、OS,應用程序都會用到局部性原理

正確答案: A B D 你的答案: A B下面說法正確的是()

A .

CPU通過內存映射I/O向I/O設備發命令

B .

DMA傳送不需要CPU的幹涉

C .

SSD是一種基於閃存或Flash的存儲技術

D .

邏輯磁盤塊的邏輯塊號可以翻譯成一個(盤面,磁道,扇區 )三元組。下面()是I/O總線

A .

USB

B .

PCI

C .

網卡

D .

圖形卡

正確答案: B 你的答案: A有關磁盤操作,說法正確的是()

A .

對磁盤扇區的訪問時間包括三個部分中,傳送時間最小。

B .

磁盤以字節為單位讀寫數據

C .

磁盤以扇區為單位讀寫數據

D .

讀寫頭總處於同一柱面

正確答案: A C 你的答案: C D計算下面磁盤的容量():4個盤片,100000個柱面,每條磁道400個扇區,每個扇區512個字節

A .

81.92GB

B .

40.96GB

C .

163.84

D .

327.68GB

正確答案: C 你的答案: A根據攜帶信號不同,總線可分為()

A .

系統總線

B .

數據總線

C .

內存總線

D .

地址總線

E .

控制總線

正確答案: B D E 你的答案: A C

- 有關RAM的說法,正確的是()

A .

SRAM和DRAM掉電後均無法保存裏面的內容。

B .

DRAM將一個bit存在一個雙穩態的存儲單元中

C .

一般來說,SRAM比DRAM快

D .

SRAM常用來作高速緩存

E .

DRAM將每一個bit存儲為對一個電容充電

F .

SRAM需要不斷刷新

G .

DRAM被組織為二維數組而不是線性數組

正確答案: A D E G 你的答案: C D E G

結對及互評

點評模板:

- 博客中值得學習的或問題:

- 5232同學補充很多課程學習的內容

本周結對學習情況

- [20155232](http://www.cnblogs.com/lsqsjsj/p/7769029.html)其他(感悟、思考等,可選)

學習進度條

| 代碼行數(新增/累積) | 博客量(新增/累積) | 學習時間(新增/累積) | 重要成長 | |

|---|---|---|---|---|

| 目標 | 5000行 | 30篇 | 400小時 |

| 第四周 | 300/1300 | 2/9 | 30/90 | |

嘗試一下記錄「計劃學習時間」和「實際學習時間」,到期末看看能不能改進自己的計劃能力。這個工作學習中很重要,也很有用。

耗時估計的公式

:Y=X+X/N ,Y=X-X/N,訓練次數多了,X、Y就接近了。

參考:軟件工程軟件的估計為什麽這麽難,軟件工程 估計方法

計劃學習時間:XX小時

實際學習時間:XX小時

改進情況:

(有空多看看現代軟件工程 課件

軟件工程師能力自我評價表)

參考資料

- 《深入理解計算機系統V3》學習指導

- 2017-2018-1 《信息安全系統設計基礎》教學進程

- 別出心裁的Linux系統調用學習法

2017-2018-1 20155215 《信息安全系統設計基礎》第11周學習總結