PCB板產生EMI的原理、如何去抑制和控制

隨著IC 器件整合度的提高、裝置的逐步小型化和器件的速度愈來愈高,電子產品中的EMI問題也更加嚴重。從系統裝置EMC /EMI設計的觀點來看,在裝置的PCB設計階段處理好EMC/EMI問題,是使系統裝置達到電磁相容標準最有效、成本最低的手段。本文介紹數位電路PCB設計中的EMI控制技術。

1 EMI的產生及抑制原理

EMI的產生是由於電磁干擾源通過耦合路徑將能量傳遞給敏感系統造成的。它包括經由導線或公共地線的傳導、通過空間輻射或通過近場耦合三種基本形式。EMI的危害表現為降低傳輸訊號質量,對電路或裝置造成干擾甚至破壞,使裝置不能滿足電磁相容標準所規定的技術指標要求。

為抑制EMI,數位電路的

●根據相關EMC/EMI技術規範,將指標分解到單板電路,分級控制。

●從EMI的三要素即干擾源、能量耦合途徑和敏感系統這三個方面來控制,使電路有平坦的頻響,保證電路正常、穩定工作。

●從裝置前端設計入手,關注EMC/EMI設計,降低設計成本。

2 數位電路PCB的 EMI控制技術

在處理各種形式的EMI時,必須具體問題具體分析。在數位電路的PCB設計中,可以從下列幾個方面進行EMI控制。

2.1 器件選型

在進行EMI設計時,首先要考慮選用器件的速率。任何電路,如果把上升時間為5ns的器件換成上升時間為2.5ns的器件,EMI會提高約4倍。EMI的輻射強度與頻率的平方成正比,最高EMI頻率(fknee)也稱為EMI發射頻寬,它是訊號上升時間而不是訊號頻率的函式:fknee =0.35/Tr (其中Tr為器件的訊號上升時間)

這種輻射型EMI的頻率範圍為30MHz到幾個GHz,在這個頻段上,波長很短,電路板上即使非常短的佈線也可能成為發射天線。當EMI較高時,電路容易喪失正常的功能。因此,在器件選型上,在保證電路效能要求的前提下,應儘量使用低速晶片,採用合適的驅動/接收電路。另外,由於器件的引線管腳都具有寄生電感和寄生電容,因此在高速設計中,器件封裝形式對訊號的影響也是不可忽視的,因為它也是產生EMI輻射的重要因素。一般地,貼片器件的寄生引數小於插裝器件,BGA 封裝的寄生引數小於QFP 封裝。

2.2 聯結器的選擇與訊號端子定義

聯結器是高速訊號傳輸的關鍵環節,也是易產生EMI的薄弱環節。在聯結器的端子設計上可多安排地針,減小訊號與地的間距,減小聯結器中產生輻射的有效訊號環路面積,提供低阻抗 迴流通路。必要時,要考慮將一些關鍵訊號用地針隔離。

2.3 疊層設計

在成本許可的前提下,增加地線層數量,將訊號層緊鄰地平面層可以減少EMI輻射。對於高速PCB,電源層和地線層緊鄰耦合,可降低電源阻抗,從而降低EMI。

2.4 佈局

根據訊號電流流向,進行合理的佈局,可減小訊號間的干擾。合理佈局是控制EMI的關鍵。佈局的基本原則是:

●模擬訊號易受數字訊號的干擾,類比電路應與數位電路隔開;

●時鐘線是主要的干擾和輻射源,要遠離敏感電路,並使時鐘走線最短;

●大電流、大功耗電路儘量避免佈置在板中心區域,同時應考慮散熱和輻射的影響;

●聯結器儘量安排在板的一邊,並遠離高頻電路;

●輸入/輸出電路靠近相應聯結器,去耦電容靠近相應電源管腳;

●充分考慮佈局對電源分割的可行性,多電源器件要跨在電源分割區域邊界布放,以有效降低平面分割對EMI的影響;

●迴流平面(路徑)不分割。

2.5 佈線

●阻抗控制:高速訊號線會呈現傳輸線的特性,需要進行阻抗控制,以避免訊號的反射、過沖和振鈴,降低EMI輻射。

●將訊號進行分類,按照不同訊號(模擬訊號、時鐘訊號、I/O訊號、匯流排、電源等)的EMI輻射強度及敏感程度,使干擾源與敏感系統儘可能分離,減小耦合。

●嚴格控制時鐘訊號(特別是高速時鐘訊號)的走線長度、過孔數、跨分割區、端接、佈線層、迴流路徑等。

●訊號環路,即訊號流出至訊號流入形成的迴路,是PCB設計中EMI控制的關鍵,在佈線時必須加以控制。要了解每一關鍵訊號的流向,對於關鍵訊號要靠近迴流路徑佈線,確保其環路面積最小。

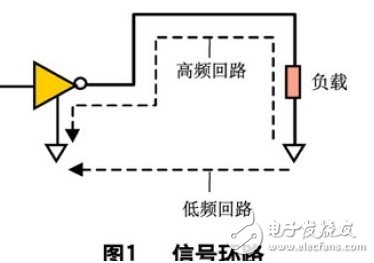

對低頻訊號,要使電流流經電阻最小的路徑;對高頻訊號,要使高頻電流流經電感最小的路徑,而非電阻最小的路徑(見圖1)。對於差模輻射,EMI輻射強度(E)正比於電流、電流環路的面積以及頻率的平方。(其中I是電流、A是環路面積、f是頻率、r是到環路中心的距離,k為常數。)

因此當最小電感迴流路徑恰好在訊號導線下面時,可以減小電流環路面積,從而減少EMI輻射能量。

●關鍵訊號不得跨越分割區域。

●高速差分訊號走線儘可能採用緊耦合方式。

●確保帶狀線、微帶線及其參考平面符合要求。

●去耦電容的引出線應短而寬。

●所有訊號走線應儘量遠離板邊緣。

●對於多點連線網路,選擇合適的拓撲結構,以減小信 號反射,降低EMI輻射。

2.6 電源平面的分割處理

●電源層的分割

在一個主電源平面上有一個或多個子電源時,要保證各電源區域的連貫性及足夠的銅箔寬度。分割線不必太寬,一般為20~50mil線寬即可,以減少縫隙輻射。

●地線層的分割

地平面層應保持完整性,避免分割。若必須分割,要區分數字地、模擬地和噪聲地,並在出口處通過一個公共接地點與外部地相連。

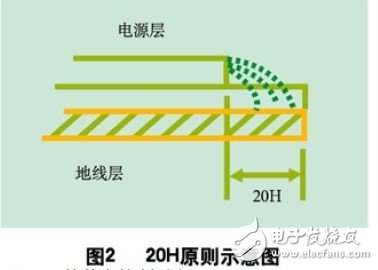

為了減小電源的邊緣輻射,電源/地平面應遵循20H設計原則,即地平面尺寸比電源平面尺寸大20H(見圖2),這樣邊緣場輻射強度可下降70% 。

3 EMI的其它控制手段

3.1 電源系統設計

●設計低阻抗電源系統,確保在低於fknee頻率範圍內的電源分配系統的阻抗低於目標阻抗。

●使用濾波器,控制傳導干擾。

●電源去耦。在EMI設計中,提供合理的去耦電容,能使晶片可靠工作,並降低電源中的高頻噪聲,減少EMI。由於導線電感及其它寄生引數的影響,電源及其供電導線響應速度慢,從而會使高速電路中驅動器所需要的瞬時電流不足。合理地設計旁路或去耦電容以及電源層的分佈電容,能在電源響應之前,利用電容的儲能作用迅速為器件提供電流。正確的電容去耦可以提供一個低阻抗電源路徑,這是降低共模 EMI的關鍵。

3.2 接地

接地設計是減少整板EMI的關鍵。

●確定採用單點接地、多點接地或者混合接地方式。

●數字地、模擬地、噪聲地要分開,並確定一個合適的公共接地點。

●雙面板設計若無地線層,則合理設計地線網格很重要,應保證地線寬度》電源線寬度》訊號線寬度。也可採用大面積鋪地的方式,但要注意在同一層上的大面積地的連貫性要好。

●對於多層板設計,應確保有地平面層,減小共地阻抗。

3.3 串接阻尼電阻

在電路時序要求允許的前提下,抑制干擾源的基本技術是在關鍵訊號輸出端串入小阻值的電阻,通常採用22~33Ω的電阻。這些輸出端串聯小電阻能減慢上升/下降時間並能使過沖及下衝訊號變得較平滑,從而減小輸出波形的高頻諧波幅度,達到有效地抑制EMI的目的。

3.4 遮蔽

●關鍵器件可以使用EMI遮蔽材料或遮蔽網。

●對關鍵訊號的遮蔽,可以設計成帶狀線或在關鍵訊號的兩側以地線相隔離。

3.5 擴頻

擴充套件頻譜(擴頻)的方法是一種新的降低EMI的有效方法。擴充套件頻譜是將訊號進行調製,把訊號能量擴充套件到一個比較寬的頻率範圍上。實際上,該方法是對時鐘訊號的一種受控的調製,這種方法不會明顯增加時鐘訊號的抖動。實際應用證明擴充套件頻譜技術是有效的,可以將輻射降低7到20dB。

3.6 EMI分析與測試

●模擬分析

完成PCB佈線後,可以利用EM I模擬軟體及專家系統進行模擬分析,模擬EMC/EMI環境,以評估產品是否滿足相關電磁相容標準要求。

●掃描測試

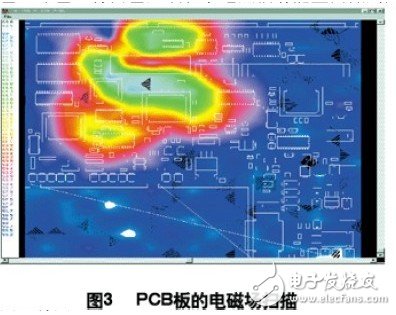

利用電磁輻射掃描器,對裝聯並上電後的機盤掃描,得到PCB中電磁場分佈圖(如圖3,圖中紅色、綠色、青白色區域表示電磁輻射能量由低到高),根據測試結果改進PCB設計。

4 小結

隨著新的高速晶片的不斷開發與應用,訊號頻率也越來越高,而承載它們的PCB板可能會越來越小。PCB設計將面臨更加嚴峻的EMI挑戰,唯有不斷探索、不斷創新,才能使PCB板的EMC /EMI設計取得成功。