FPGA源同步輸出時序約束(二)

轉自:https://blog.csdn.net/huan09900990/article/details/77050894

版權宣告:本文為博主原創文章,未經博主允許不得轉載。 https://blog.csdn.net/huan09900990/article/details/77050894

FPGA源同步輸出約束(一)主要是介紹了輸出時鐘的幾種產生方式以及對應的約束指令,本節主要介紹源同步輸出延遲的幾種約束方法:(1)system-centric 以系統為中心進行約束 (2)FPGA-centric 以fpga為中心進行約束。以及輸出最大最小延遲值的計算推導,最後用約束指令描述出來。下文是以從spec上得到fpga和外部器件的特性引數 進行約束,至於用示波器測量fpga時鐘,資料輸出埠延遲的方法暫時不做介紹。

1、system-centric

該方法是將fpga部分和外部器件聯合起來構成一個系統 進行時序約束分析,其特點是要用到外部器件的一些引數 比如tco,tsu,th 或fpga 到外部器件間的時鐘,資料走線延遲 。所以如果選用該方法時,你需要知道外部器件的引數。

(1)用外部器件的tsu ,th和時鐘,資料的走線延遲 來進行輸出最大最小延遲約束

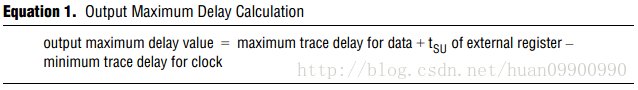

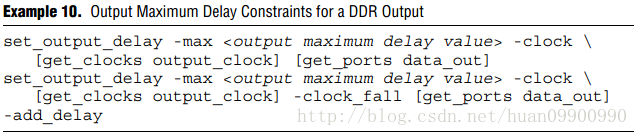

—-輸出最大延遲約束:即資料路徑的最大延遲+時鐘路徑的最小延遲+外部器件的tsu

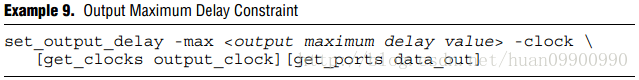

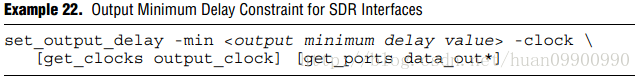

對於源同步SDR輸出約束指令如下:

output_clock:即 源同步的輸出時鐘

data_out*: 即源同步輸出的資料

對於源同步DDR輸出,其上升下降沿都需要約束,約束指令如下:

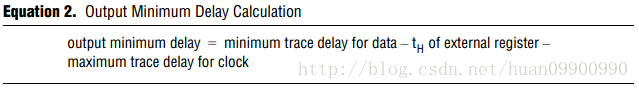

—-輸出最小延遲約束:即資料路徑的最小延遲+時鐘路徑的最大延遲-外部器件的th

對於源同步SDR輸出約束指令如下:

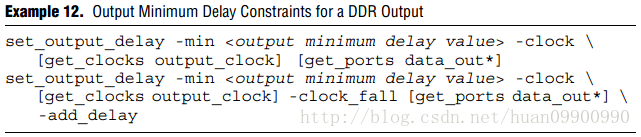

對於源同步DDR輸出,其上升下降沿都需要約束,約束指令如下:

2、FPGA-centric

該方法是以fpga為中心,進行源同步輸出延遲約束。fpga-centric是根據輸出時鐘和資料間的一個時鐘偏斜去進行輸出約束的。時鐘偏斜等於時鐘沿和資料沿之間的時間差,對於時鐘資料邊沿對齊介面 時鐘偏斜等於0;對於時鐘資料中心對齊,時鐘偏斜等於UI/2。SDR介面UI等於時鐘週期,DDR介面UI=時鐘週期/2。

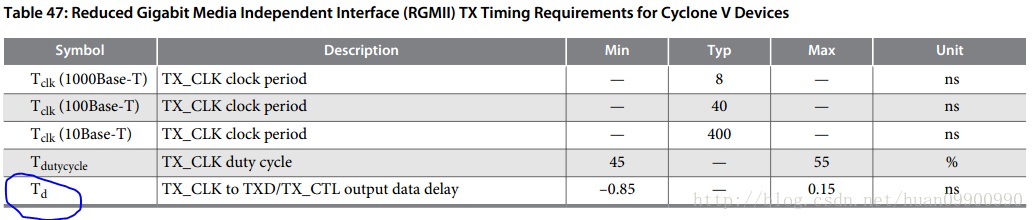

用FPGA-centric進行約束,你只需要知道fpga的輸出時鐘和資料間的偏斜值tskew就能進行輸出約束。下面是我查詢到的 altera cyclone v 晶片datasheet上給出RGMII介面的輸出時鐘和資料間的偏斜值。

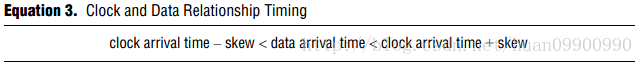

fpga-centric方法 即 時鐘 資料時序要滿足下面的公式:

資料的最早到達時間必須比時鐘到達時間-skew 大,否則不能滿足外部器件的th保持時間。

資料的最晚到達時間必須比時鐘到達時間+skew 小 ,否則不能滿足外部器件的tsu建立時間。

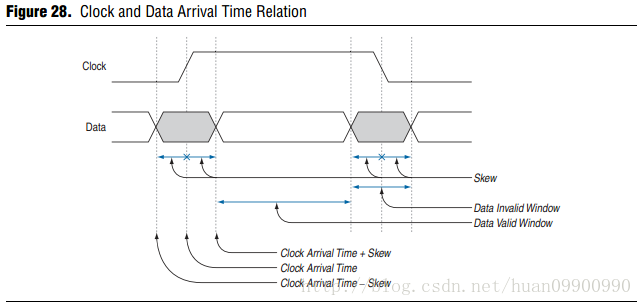

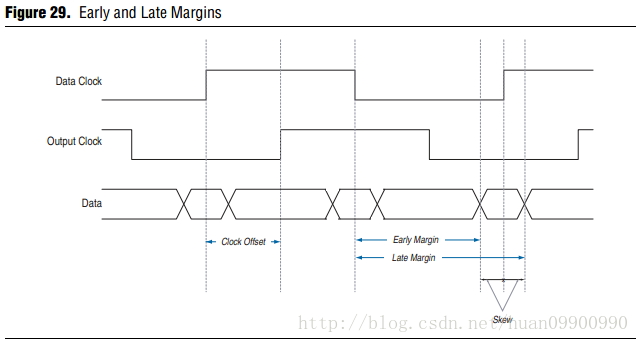

時鐘和資料間到達外部器件的時間關係如下圖所示:

(1) 根據時鐘資料間的建立保持關係進行源同步輸出時序約束

根據建立關係對輸出最大延遲進行時序約束

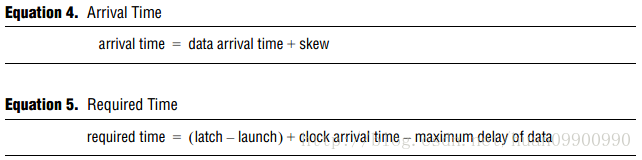

根據Equation 3 ,資料的最晚到達時間(data arrival +skew)必須比資料需求時間(clock arrival) 小 ,否則不能滿足外部器件的tsu建立時間,下面是資料到達時間和資料需求時間的計算器公式。

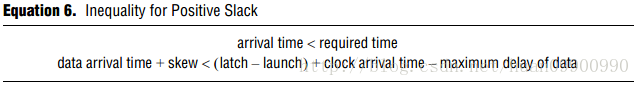

根據時鐘資料滿足建立時間正裕量,如下

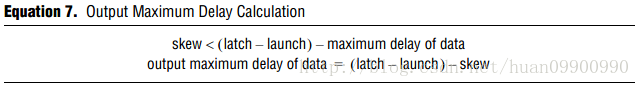

在源同步電路中,要求資料到達時間跟時鐘到達時間一致,所以根據此把Equation6 進行簡化得到下面Equation7的公式1以及輸出最大延遲值計算公式2

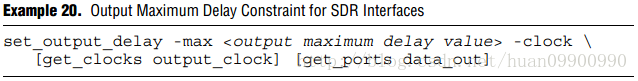

對於源同步SDR輸出約束指令如下:

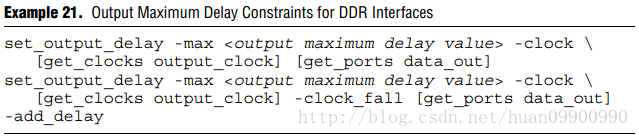

對於源同步DDR輸出,其上升下降沿都需要約束,約束指令如下:

根據保持關係對輸出最小延遲進行時序約束

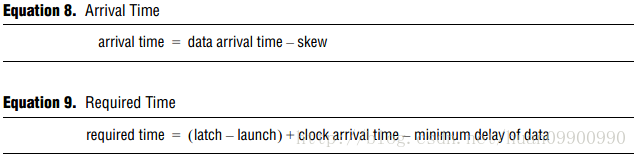

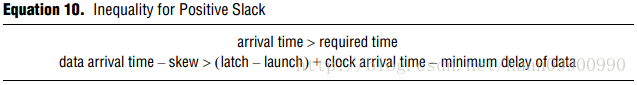

根據Equation 3 ,資料的最早到達時間(data arrival -skew)必須比資料需求時間(clock arrival) 大 ,否則不能滿足外部器件的th保持時間,下面是資料到達時間和資料需求時間的計算器公式。

下面是將Equation8,9的資料到達時間和資料需求時間代入後的公式

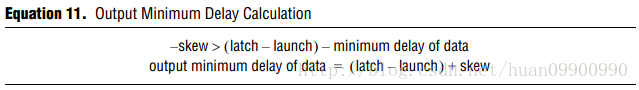

同樣根據在源同步電路中,要求資料到達時間跟時鐘到達時間一致,所以根據此把Equation10進行簡化得到下面Equation11的公式1以及輸出最小延遲值計算公式2,這裡的latch和launch 是保持的latch 和launch。

對於源同步SDR輸出約束指令如下:

對於源同步DDR輸出,其上升下降沿都需要約束,約束指令如下:

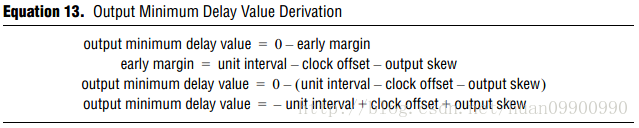

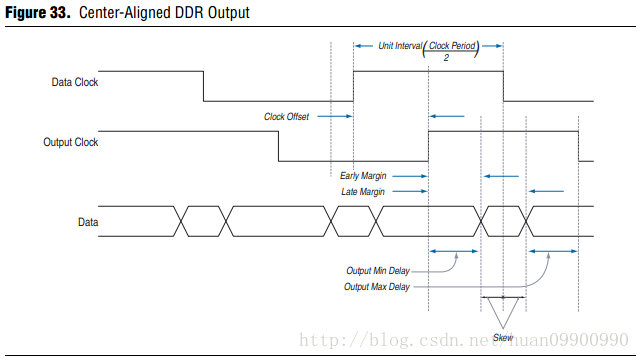

(2)用early and late margins進行約束

early margin等於minimum tco,late margin等於miximum tco。

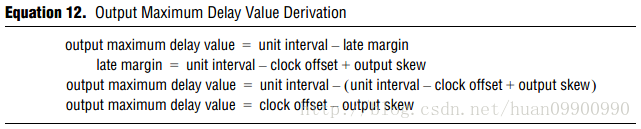

—-時鐘資料中心對齊的DDR介面,進行時序最大最小延遲值的公式推導。

輸出最大最小延遲值推導如下:

下面的這4中資料時鐘輸出形式,只需要把上面公式裡的clock offset,unit interval 替換成對應的值就可以了。

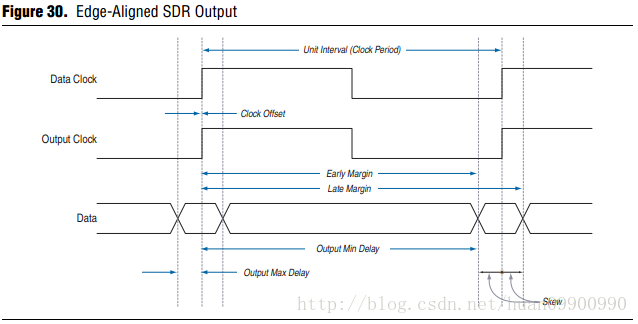

—-時鐘資料邊沿對齊的SDR介面,進行時序分析約束。

時鐘資料的輸出相位如下圖所示,此時clock offset為0 ,UI等於時鐘週期:

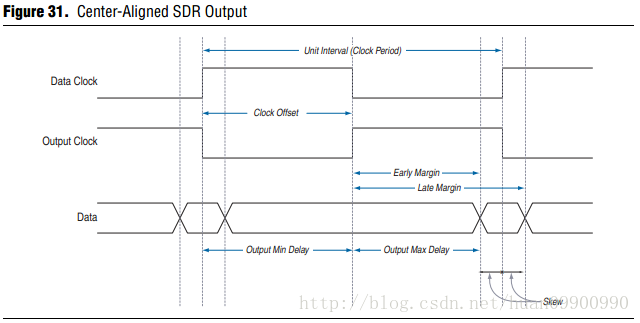

—-時鐘資料中心對齊的SDR介面,進行時序分析約束。

時鐘資料的輸出相位如下圖所示,此時clock offset為時鐘週期/2 ,UI等於時鐘週期:

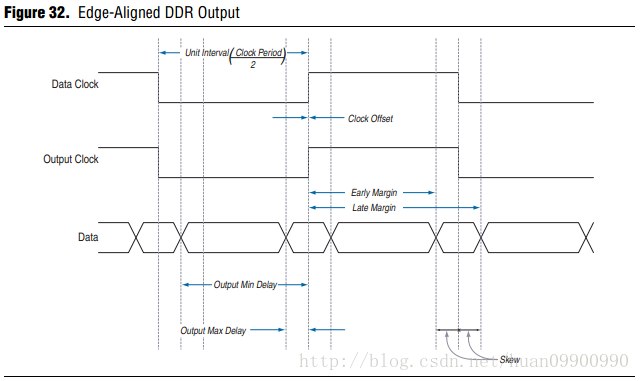

—-時鐘資料邊沿對齊的DDR介面,進行時序分析約束。

時鐘資料的輸出相位如下圖所示,此時clock offset為0 ,UI等於時鐘週期/2:

—-時鐘資料中心對齊的DDR介面,進行時序分析約束。

時鐘資料的輸出相位如下圖所示,此時clock offset為時鐘週期/4 ,UI等於時鐘週期/2: