編碼的奧祕:二進位制加法機

轉自:《編碼的奧祕》 第十二章

加法是最基本的算術運算。所以,如果想要建造一臺計算機(這是本書隱含討論的問題),必須首先知道如何構造一種機器,它可以把兩個數加起來。當你解決了這個問題,你會發現加法正是計算機唯一所做的事情,因為通過使用用於加法的機器,我們還可以構造用加法來實現減法、乘法、除法以及計算房產抵押款、引導向火星發射衛星、下棋和電話計費等等功能的機器。

同現代的計算器和計算機比起來,本章構造的加法機龐大、笨重、速度慢且噪聲大。但有意思的是構成它的部件完全是前幾章學過的電子裝置,如開關、燈泡、電線、電池以及可構成幾種邏輯閘的繼電器。這個加法機包含的所有部件都於 1 2 0年以前就已發明,而且,我們並不用真正地在屋子裡建造它,只需在紙上和腦子裡構造這臺機器就行了。

這個加法機只能工作於二進位制數,而且它缺少很多現代計算機(器)的輔助裝置。它不能用鍵盤來敲入你想加的數,代之的你只能用一系列開關表示待加的數。它也不能用顯示器顯示結果,你所看到的只是一排燈泡。

但這臺加法機確實實現了兩數相加的功能,而且其工作方式和計算機做加法十分相似。

二進位制加法與十進位制加法很像。當你相加十進位制數如 2 4 5 和6 7 3 時,你把問題分解成簡單的步驟,每一步只對一對十進位制數字相加。本例中,第 1 步是把 5和3加起來。生活中,你若能記住加法表,問題的解決就快多了。

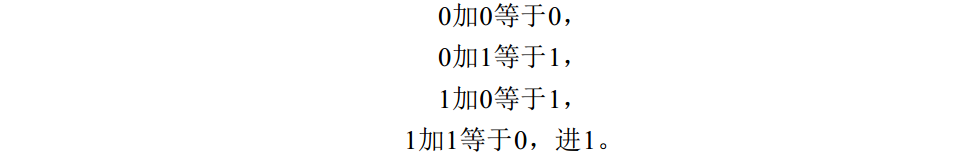

十進位制加法和二進位制加法的一大區別是二進位制數字的加法表要比十進位制數字的加法表簡單得多:

你可能在學校裡記過上面這張表,並背誦過如下口訣:

把相加結果的數前加上零,可以把加法表改寫成如下形式:

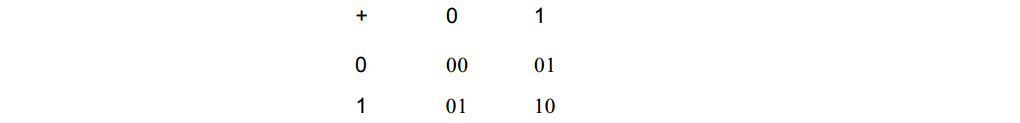

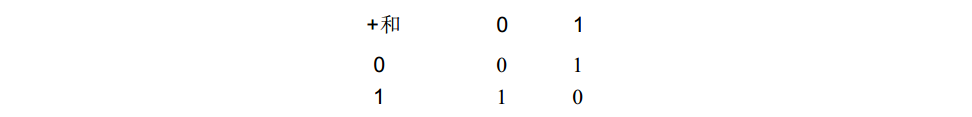

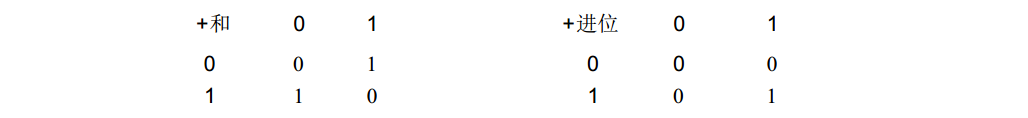

這樣一來,二進位制數字相加的結果是兩位數,分別稱為“和”和“進位”(比如“ 1 加1 等於0,進位是 1 ”)。現在,可以把這張二進位制加法表分成兩張表,第 1 張是表示“和”的表:

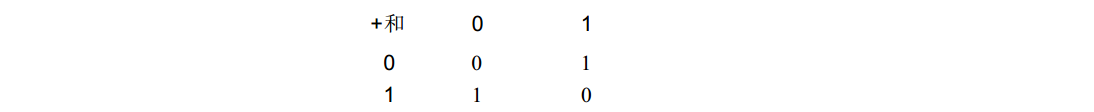

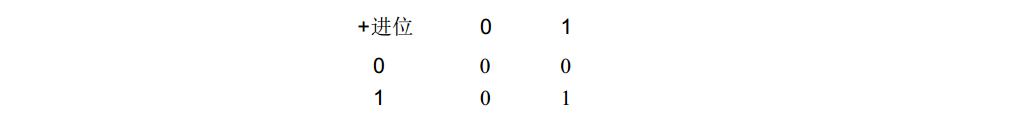

第2張是表示“進位”的表:

以這種方式來看待二進位制加法就很方便了,因為加法機會分開求和與進位。構造二進位制加法機需要設計一個能執行表中所描述操作的電路。因為電路的所有部件,如開關、燈泡、電線都是可以表示成二進位制數的,因而該電路由於僅工作於二進位制數從而大大降低了電路的複雜性。

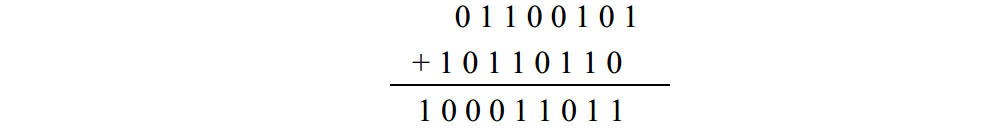

與十進位制加法一樣,二進位制加法也從最右邊的一列開始,逐列相加兩個數:

注意,當從右邊加到第 3列的時候,產生了一個進位。同樣的情況也發生在第 6、 7、 8列。

我們要加多大的數呢?由於這個加法機只是在腦子裡構造,因而可以加很長的數字。為更合理一些,選擇不超過 8位的二進位制數。也就是說,運算元的範圍是從 0 0 0 0 - 0 0 0 0~ 111 1 -1111,即十進位制的 0~2 5 5。兩個8位二進位制數的和最大可以是 1 - 1111 - 111 0,即 5 1 0。

此二進位制加法機的控制面板如下圖所示:

板上有兩行開關,每行 8個。這些開關集是輸入裝置,我們將用它輸入兩個 8位數。開關往下表示 0,往上表示 1 ,正如家裡牆上的開關。輸出裝置在板的底部,是一行燈泡,共 9個。這些燈泡用來表示加法的結果,不亮的燈泡表示 0,亮的表示 1 。我們用了 9個燈泡是因為兩個8位數相加的結果可能是 9位數。

加法機的餘下部分包含了以不同方式連線而成的邏輯閘。開關觸發邏輯閘中的繼電器,繼電器接著點亮相應的燈泡。例如,如果我們想把 0 11 0 - 0 1 0 1 和 1 0 11 - 0 11 0加起來(即前例中顯示的兩個數字),需把相應的開關設定成下面的樣子:

燈泡的亮暗表明答案是 1 - 0 0 0 1 - 1 0 11 。 (當然,這只是希望的情況。畢竟,我們還沒有把這個加法機構造出來!)

上一章提到過本書將會用到很多繼電器,本章中的 8位加法機就至少需要 1 4 4個繼電器,其中每一對數進行加法操作需要 1 8個繼電器( 8 × 1 8 = 1 4 4)。如果畫出完整的電路圖,你一定會大驚失色,任何人都無法將連成一堆的 1 4 4個繼電器看得明明白白,所以我們將用邏輯閘分步解決這個問題。

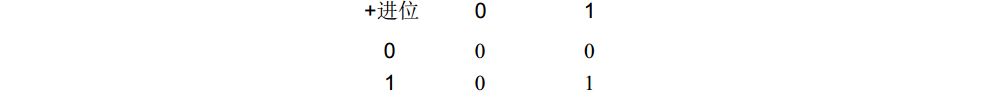

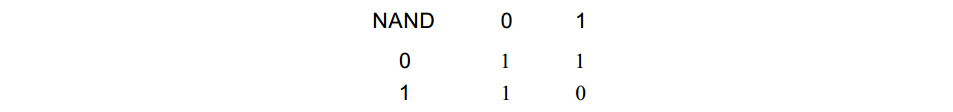

當你看到下面兩個 1 位二進位制數相加的進位表時,你可能立刻會想到邏輯閘和二進位制加法之間有某種聯絡:

你也許已意識到這和上章所述的與門的輸出是一樣的:

所以,與門可以用來計算兩個 1 位進位制數位相加得到的進位。

看來我們已取得一點兒進展了,下一步就要看看有沒有繼電器能完成下面的工作:

這是二進位制加法運算中的另一半問題,雖說表示和的這一位不如進位那麼容易實現,但我們會有辦法

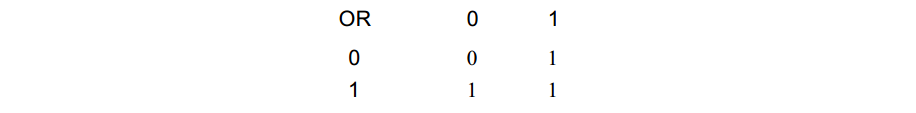

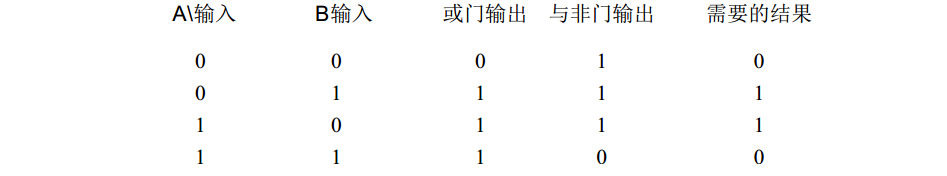

首先應意識到或門的輸出和我們所期望的很近似,只是右下角的結果不同:

而對於與非門而言,除了左上角的輸出不同以外,其他結果也與期望的一樣:

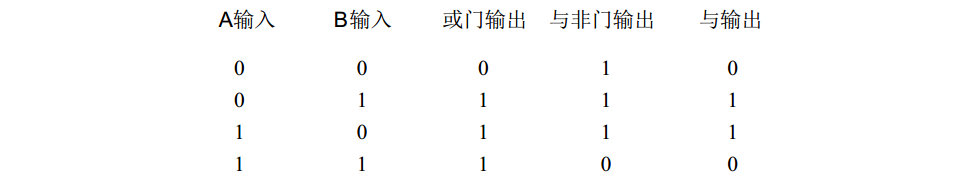

所以,使用相同的輸入,讓我們把與非門和或門連線起來:

下表總結了或門和與非門的輸出,並將其結果和加法機所要求的結果進行比較:

注意,當或門和與非門的輸出都為 1 時,就可以得到期望的結果 1 ,這暗示著把兩個輸出作為與門的輸入:

好,這樣就能滿足要求了。

整個電路仍然只有兩個輸入,一個輸出。兩個輸入既連到了或門,也連到了與非門。或門和與非門的輸出作為與門的輸入,從而得到預期的結果:

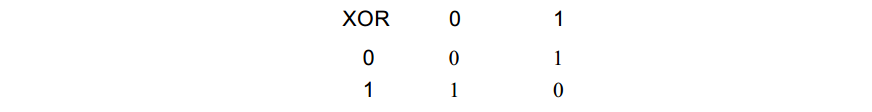

這個電路有它自己的名字,稱為“異或門( Exclusive OR gate 或 X O R)”。異或門輸出為1 時, A輸入為 1 或B輸入為 1 ,但不能同時為 1 。不用再去畫一個或門、一個與非門和一個與門,可以用電氣工程師規定的符號來表示它:

它看上去和或門很像,只是在輸入端還有一條曲線。異或門的行為表示如下:

異或門是本書需要詳細描述的最後一個邏輯閘(在電氣工程中有時還會遇到第六個門,稱為“同或門”,同或門只有兩個輸入相等時輸出才為 1 。同或門描述的輸出情況正好和異或門相反,所以這個門的符號和異或門相同,同時在輸出端有一個小圓圈)。

讓我們來總結一下。兩個二進位制數相加產生兩個表,一個是表示“和”的表,另一個是表示“進位”的表:

用下面兩個邏輯閘可以得到同樣的結果:

二進位制數的“和”可以由異或門得到,而“進位”可以由與門得到,所以可以把異或門和與門結合起來來完成兩個二進位制數 A和B的加法:

不用畫與門和異或門,可以把上圖簡單地表示成如下的樣子:

其中的方塊稱為“ 半加器( Half Adder)”,它可以把兩個二進位制位 A 和 B相加,從而得到一個和輸出 (簡稱S) 和一個進位輸出 (簡稱C O )。但大部分二進位制數是多於 1 位的,半加器不能夠把前一步的進位加到本次運算中。例如做如下加法:

只能用半加器來計算最右邊一列數:即 1 加1 等於 0,進位為 1 。對於右邊第 2列數,由於進位的存在,需要加 3 個數。接下來的幾列都有這個問題,每一列二進位制位的加法都包括了來自前一列的進位。

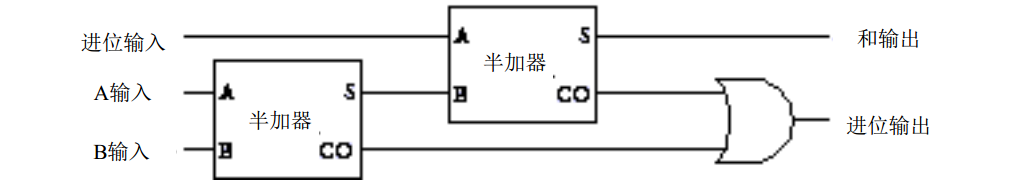

要把3個二進位制數相加,需要按如下方式把兩個半加器和一個或門連線起來:

要理解它的工作原理,先從最左邊第一個半加器的 A 輸入和 B 輸入開始,其輸出是一個和及相應的進位。這個和必須和前一列的進位輸入 (簡稱CI) 加起來,然後把它們輸入到第二個半加器。第二個半加器的和輸出是最後的和。兩個半加器的進位輸出又輸入到一個或門,或門產生了本次加法的進位輸出。你可能會想這裡還需要一個半加器,這當然是可行的。但當你把所有的可能情況考慮完,你會發現兩個進位不可能同時為 1 。當兩個輸入不能同時為 1時,或門已足夠用於表示兩個進位的加法,此時或門和異或門的功能是相同的。

上圖可簡化表示為下面的方塊圖,稱其為“ 全加器( Full Adder)”:

下面的表是對全加器所有可能的輸入及其相應輸出的小結:

前面說過加法機需要 1 4 4個繼電器,這個數目是如何得到的呢?每個與門、或門、與非門都需要 2個繼電器,所以,一個異或門需 6個繼電器。一個半加器由一個異或門和一個與門構成,所以它要 8個繼電器。 1 個全加器需要兩個半加器和一個或門,所以它要 1 8個繼電器。對於8位二進位制加法機而言,共需 8個全加器,因而總共是 1 4 4個繼電器。

回想一下本章最開始那個帶開關和燈泡的控制面板:

現在可以把這些開關和燈泡連線成全加器了。

首先把最右邊的兩個開關和一個燈泡連到一個全加器上,如下圖所示:

當把兩個二進位制數相加時,第 1 列的處理有所不同。因為接下去的幾列可能包括來自前面加法的進位,而第 1 列不會有進位,所以全加器的進位輸入端是接地的,這表示輸入為“ 0”。第1 列相加後很可能會產生一個進位輸出,這個進位輸出是下一列加法的輸入。

對於接下去的兩個二進位制位和燈泡,可以按如下辦法連線全加器:

第一個全加器的進位輸出是第二個全加器的進位輸入。接下去的每一列數都以這種方式連線,每一列的進位輸出都是下一列的進位輸入。

第八個燈泡和最後一對開關連到最後一個全加器上,連線方式如下圖所示:

這裡最後的進位輸出連到第九個燈泡上。

這樣, 8個全加器就構造成功了。

還可以用另一種方式來看 8個全加器的整合,每個全加器的進位輸出都是下一個全加器的進位輸入:

下面是一個完整的遮蔽在一個盒子裡的 8位加法器。輸入是 A和B標識為從A0~A7及B0~B 7。輸出為和輸出,標識為從 S0~S 7:

這是標識多位數字的常用方法。下標為 0的位 A0、 B0和 S0表示最右邊的、最不起眼的位。而位A7、 B7和S7是最左邊的、最引人注目的位。例如,下面展示的是這些字母是如何用來表示二進位制數 0 11 0 - 1 0 0 1 的:

下標始於 0,且向高位遞增的原因是它們和 2的乘方數(冪)是對應的:

如果把每個二進位制位和對應的 2的冪次方相乘再依次相加,你就會得到 0 11 0 - 1 0 0 1 的十進位制數表示,即 6 4 + 3 2 + 8 + 1 = 1 0 5。

8位加法器的另一種畫法是:

雙線箭頭包含了 8個輸入端,代表一組 8個分開的訊號。它們標識為 A7… A0、 B7…B 0、 S7… S0也用來表示一個 8位二進位制數。

一旦構造了一個 8位加法器,就可以構造另一個加法器。把它們級聯起來可以很容易地構成1 6位加法器:

右邊加法器的進位輸出連到左邊加法器的進位輸入端。左邊加法器的輸入包含了兩個加數的高8位,同時產生了結果的高 8位。

現在,你可能會問: “計算機真的是以這種方式把數字加起來的嗎?”

基本上是這樣的,但不完全是。

首先,加法器應該做得更快。如果你明白這個電路是如何工作的,你會看到最低位相加產生的進位作為下一列數相加的一個輸入,而第 3 列的加法又等著第 2列加法的進位,依此類推。加法器總體的速度等於加數的位數乘以單個全加器的速度。這種進位方式稱為行波進位 。更快的加法器使用稱為先行進位 的加法電路,從而加快了加法程序。

第二(但是十分重要),計算機再也不用繼電器了!儘管它們曾經用過。建於 2 0世紀 3 0年代初的第一批數字計算機使用繼電器,後來又用了真空管。現代計算機用電晶體。當用在計算機中時,電晶體和繼電器的功能差不多,但是電晶體速度更快,體積更小,更安靜,更省電,而且還便宜不少。構造一個 8位加法器仍然需要 1 4 4個電晶體(如果採用先行進位,則需要更多) ,但整體電路的體積卻小多了。