【 FPGA 】7 Series FPGA中對SRL的設計指導

Xilinx 7 Series FPGA and Zynq-7000 All Programmable SoC Libraries Guide for HDL Designs

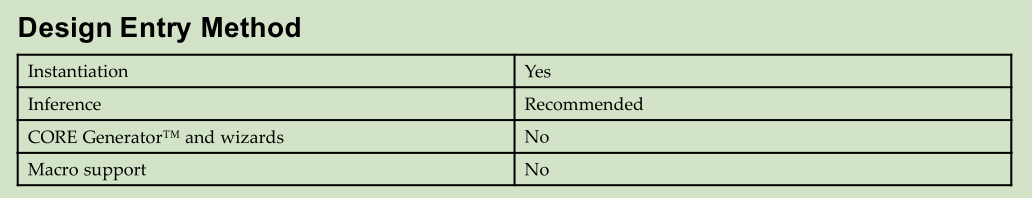

最近在看關於Ultrafast設計方法學的視訊以及Vivado design Methodology的使用者手冊時,總是提到SRL,我總是很困惑,總是用這個縮寫,到底是啥,也許沒有看這些東西的時候,我還知道它就是移位暫存器,可是我總以為這裡面提到的東西是什麼高階的玩意,誤導了自己,以為是什麼更高階的結構,於是一探究竟,查看了7系列FPGA的元件庫設計指導,也就是開頭提到的那一串英文,不就是一個移位暫存器LUT嘛。

這篇博文簡單對其進行一個介紹,以便能更深入地理解它。

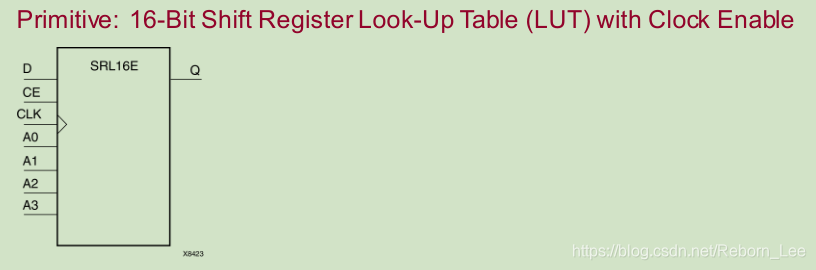

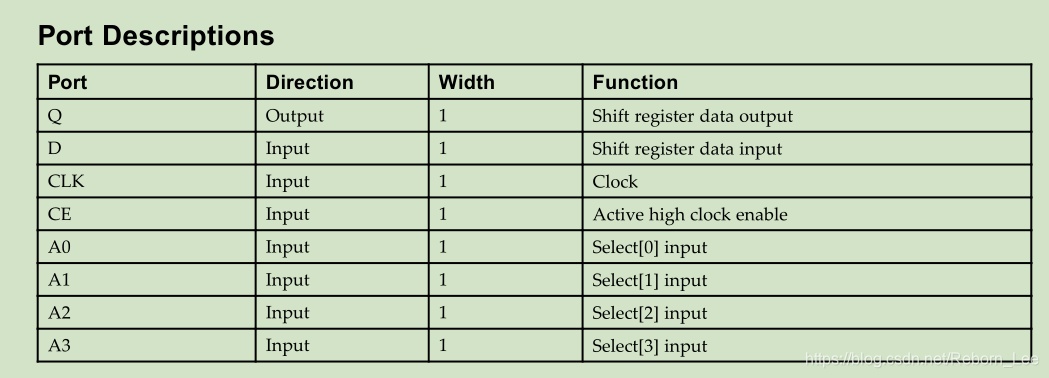

SRL16E

該設計元素是移位暫存器查詢表(LUT)。 輸入A3,A2,A1和A0選擇移位暫存器的輸出長度。

移位暫存器可以是固定的靜態長度,也可以動態調整。

•建立固定長度的移位暫存器 - 使用靜態值驅動A3至A0輸入。 移位暫存器的長度可以在1位到16位之間變化,由下式確定:長度=(8 x A3)+(4 x A2)+(2 x A1)+ A0 +1如果是A3,A2, A1和A0都是零(0000),移位暫存器是一位長。 如果它們都是1(1111),則它是16位長。

•動態更改移位暫存器的長度 - 更改驅動A3至A0輸入的值。 例如,如果A2,A1和A0都是1(111)並且A3在一(1)和零(0)之間切換,則移位暫存器的長度從16位變為8位。

在內部,移位暫存器的長度始終為16位,輸入線A3至A0選擇16位中的哪一位到達輸出。

通過將四位十六進位制數分配給INIT屬性來初始化移位暫存器LUT內容。 第一個或最左邊的十六進位制數字是最重要的位。 如果未指定INIT值,則預設值為四個零(0000),以便在配置期間清除移位暫存器LUT。

當CE為高電平時,資料(D)在低電平到高電平時鐘(CLK)轉換期間被載入到移位暫存器的第一位。 在隨後的低到高時鐘轉換期間,當CE為高電平時,資料在載入新資料時轉移到下一個最高位位置。 當達到由地址輸入確定的移位暫存器長度時,資料出現在Q輸出上。 當CE為低電平時,暫存器忽略時鐘轉換。

Verilog InstantiationTemplate

// SRL16E: 16-bit shift register LUT with clock enable operating on posedge of clock (Mapped to a SliceM LUT6)

// 7 Series

// Xilinx HDL Libraries Guide, version 14.7

SRL16E #(

.INIT(16'h0000) // Initial Value of Shift Register

) SRL16E_inst (

.Q(Q), // SRL data output

.A0(A0), // Select[0] input

.A1(A1), // Select[1] input

.A2(A2), // Select[2] input

.A3(A3), // Select[3] input

.CE(CE), // Clock enable input

.CLK(CLK), // Clock input

.D(D) // SRL data input

);

// End of SRL16E_inst instantiation

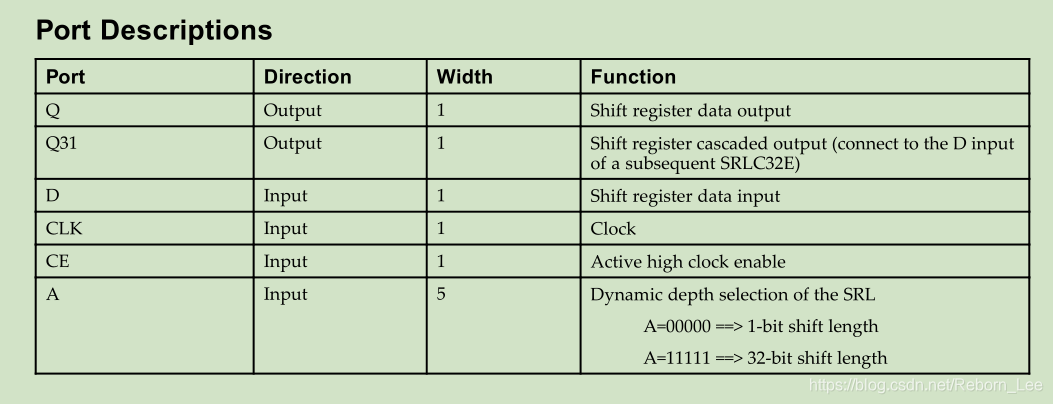

SRLC32E

該設計元素是在單個查詢表(LUT)內實現的可變長度,1至32個時鐘週期移位暫存器。 移位暫存器可以是固定長度,靜態長度,也可以通過改變元件的地址線來動態調整。 該元件還具有高電平有效時鐘使能和級聯功能,其中可以級聯多個SRLC32E,以建立更大的移位長度。

如果例項化,則應對此元件進行以下連線:

•將CLK輸入連線到所需的時鐘源,將D輸入連線到要移位/儲存的資料來源,將Q輸出連線到FDCE或FDRE輸入或其他適當的資料目標。

•CE時鐘使能引腳可以連線到設計中的時鐘使能訊號,或者如果不使用則連線到邏輯1。

•5位A匯流排可以連線到0到31之間的靜態值,以表示固定的1到32位靜態移位長度,或者它可以連線到適當的邏輯,以在1和32位之間的任何位置啟用變化的移位深度。

•如果要建立比32更長的移位長度,請將Q31輸出引腳連線到後續SRLC32E的D輸入引腳,以級聯並建立更大的移位暫存器。

•將Q31輸出連線到除另一個SRLC32E以外的任何其他裝置無效。

•如果需要,可選Q輸出仍可在級聯模式下使用。

•可以指定由32位十六進位制值組成的可選INIT屬性,以指示移位暫存器的初始移位模式。

•(INIT [0]將是第一個移出的值。)

Verilog InstantiationTemplate

// SRLC32E: 32-bit variable length cascadable shift register LUT (Mapped to a SliceM LUT6)

// with clock enable

// 7 Series

// Xilinx HDL Libraries Guide, version 14.7

SRLC32E #(

.INIT(32'h00000000) // Initial Value of Shift Register

) SRLC32E_inst (

.Q(Q), // SRL data output

.Q31(Q31), // SRL cascade output pin

.A(A), // 5-bit shift depth select input

.CE(CE), // Clock enable input

.CLK(CLK), // Clock input

.D(D) // SRL data input

);

// End of SRLC32E_inst instantiation