FPGA DDR3 Demo的測試和自建模擬平臺

阿新 • • 發佈:2018-12-23

一. Demo的測試:

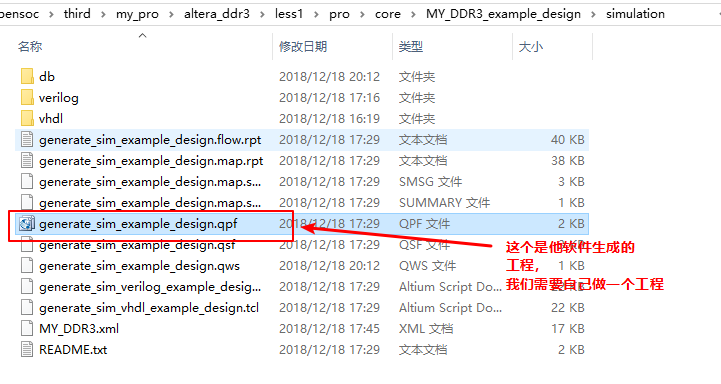

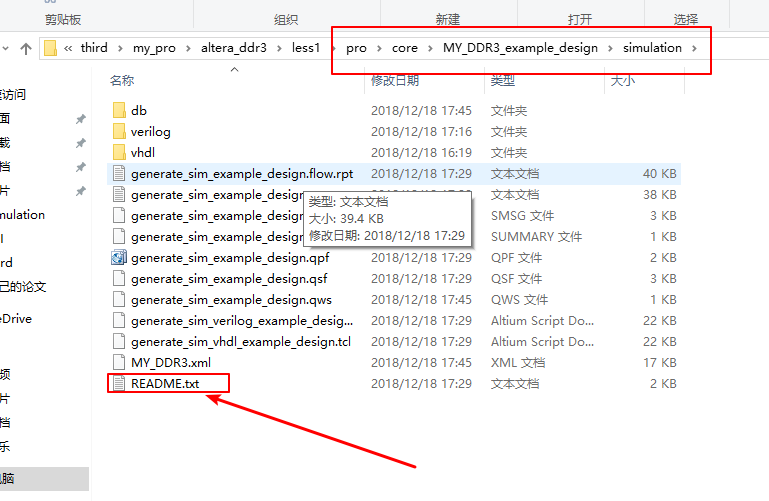

新建完一個DDR3的IP核後,在core的MY_DDR3_example_design的simulation資料夾裡面有README.txt

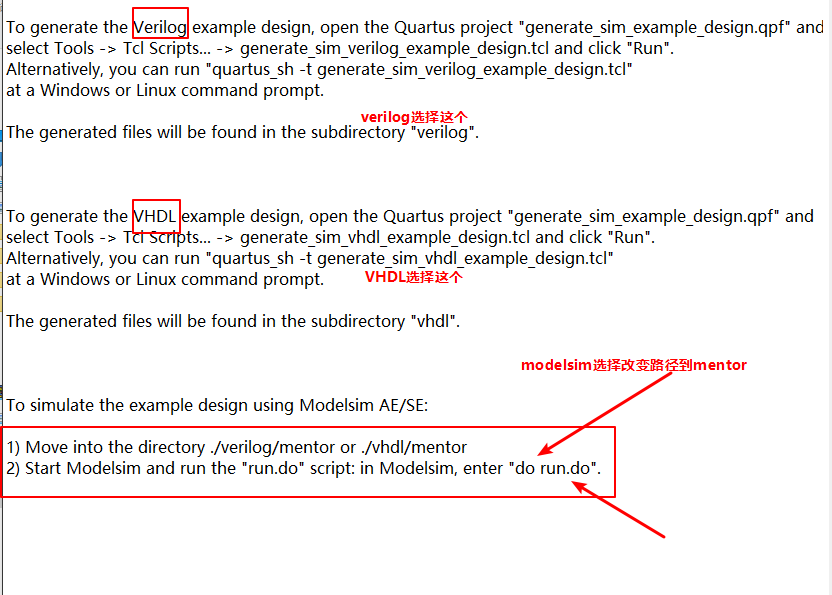

README裡面會有提示你需要有哪些步驟。

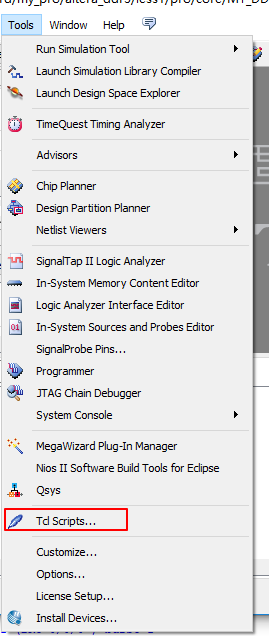

1.開啟模擬的工程,然後選擇執行tcl指令碼tcl scripts

然後點選run一下tcl。

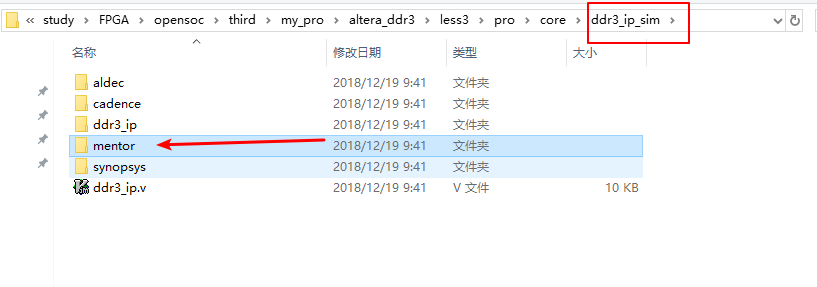

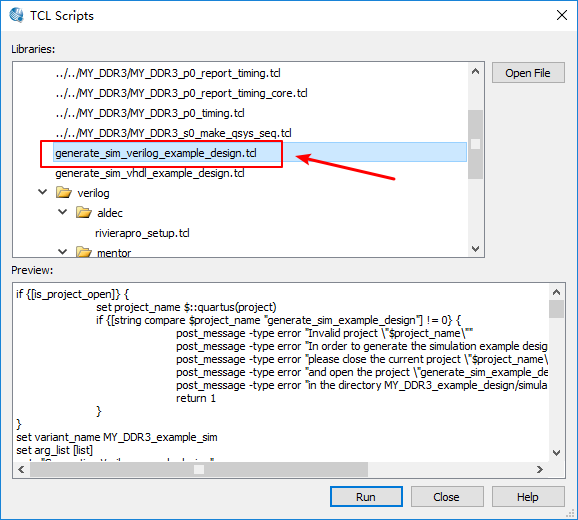

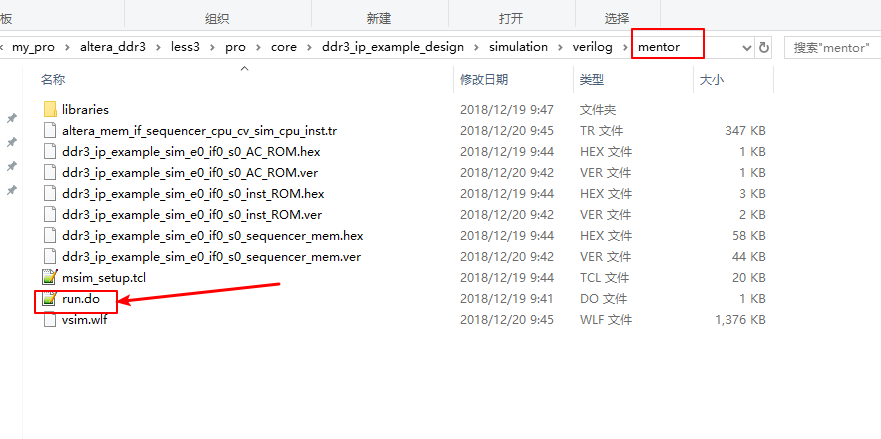

2.根據readme的提示,change Directory改變路徑到verilog / ... /mentor這個路徑下

然後執行路徑下的do檔案。

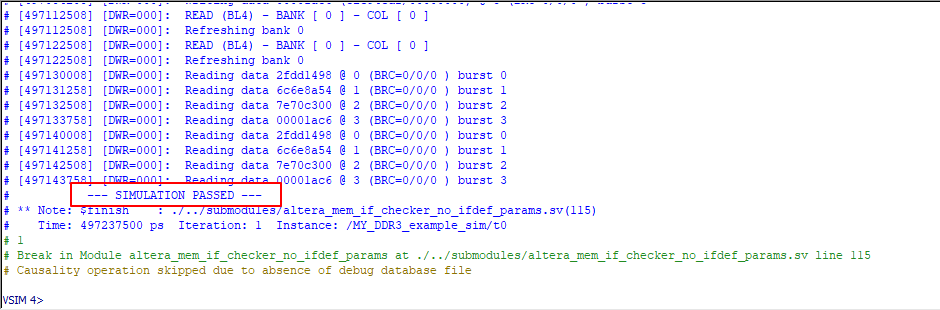

3.do完後,會提示simulation passen 模擬結束。

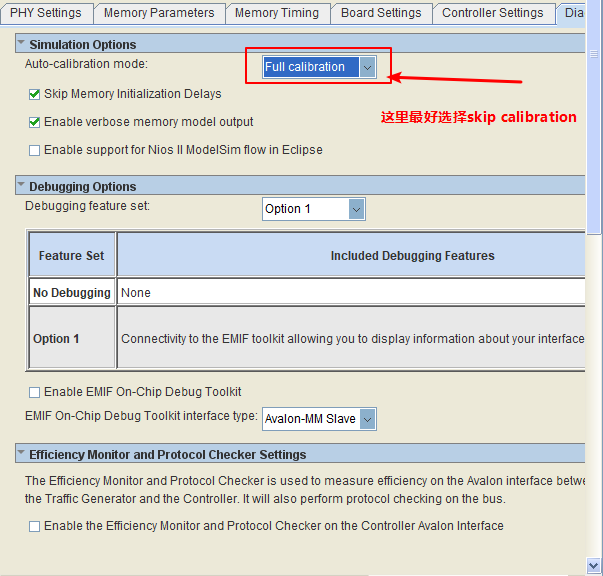

需要模擬的話,在生成IP核的時候,auto-calibration mode ————skip calibration.

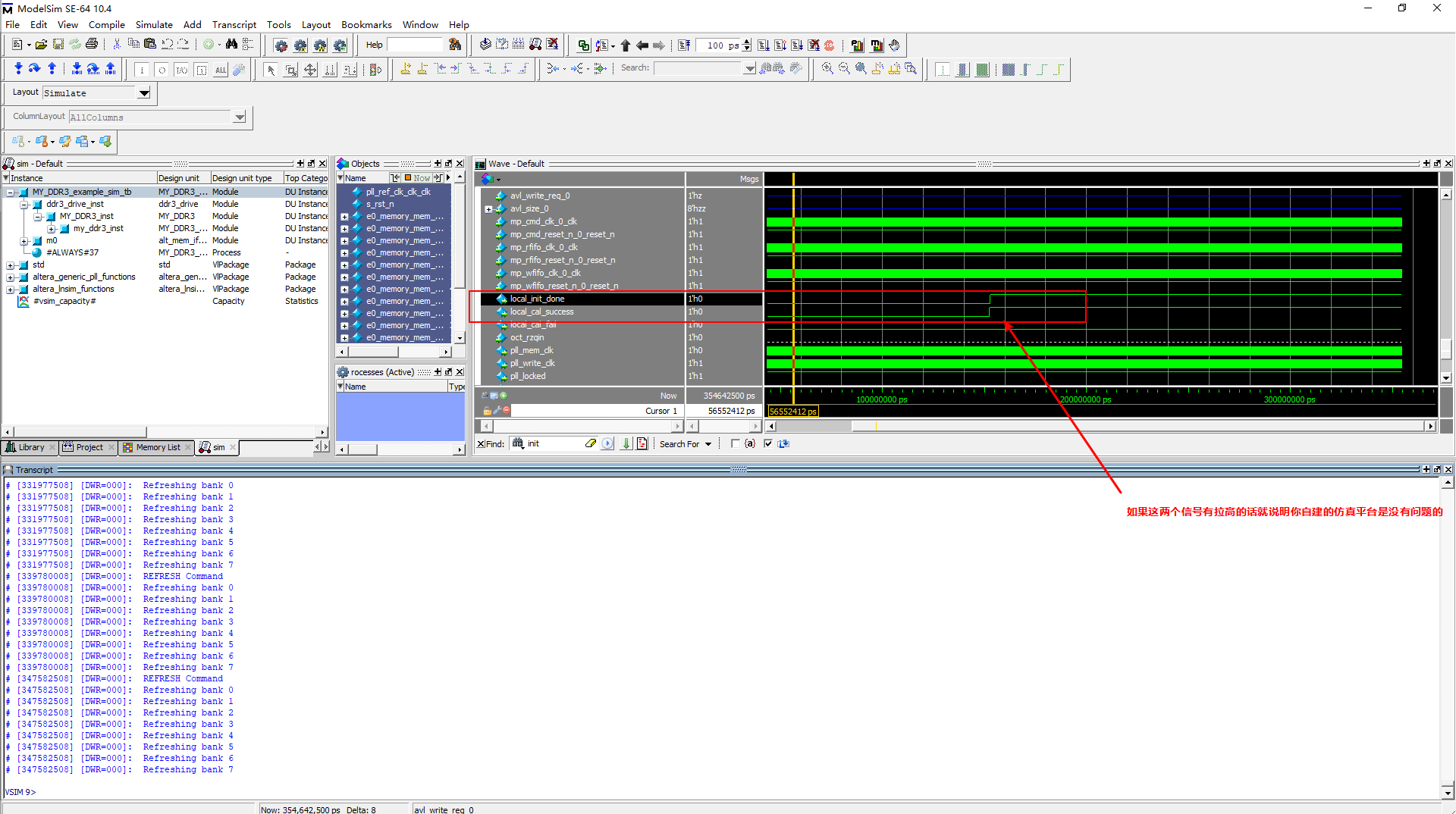

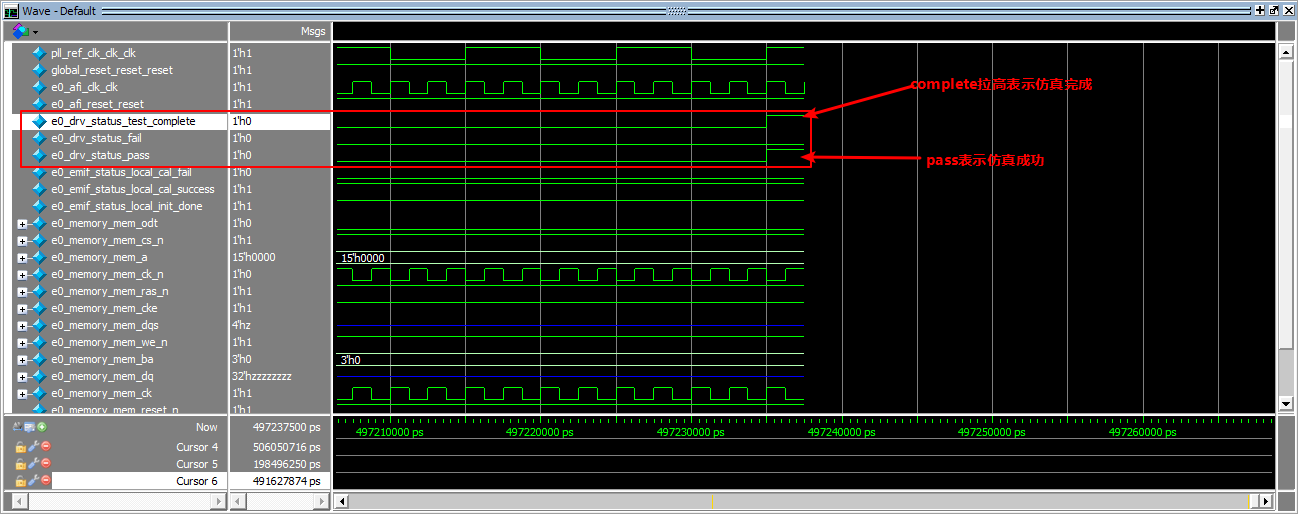

4.檢視模擬波形

二:自建模擬平臺:

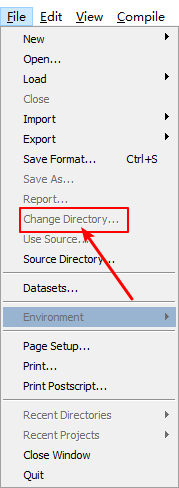

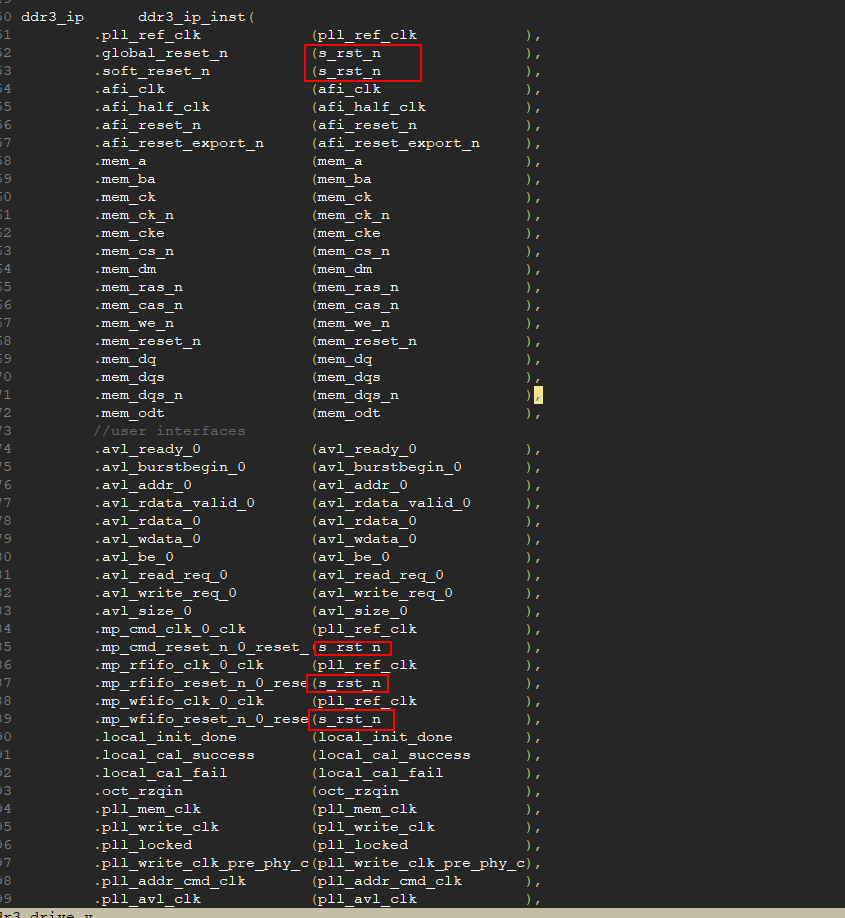

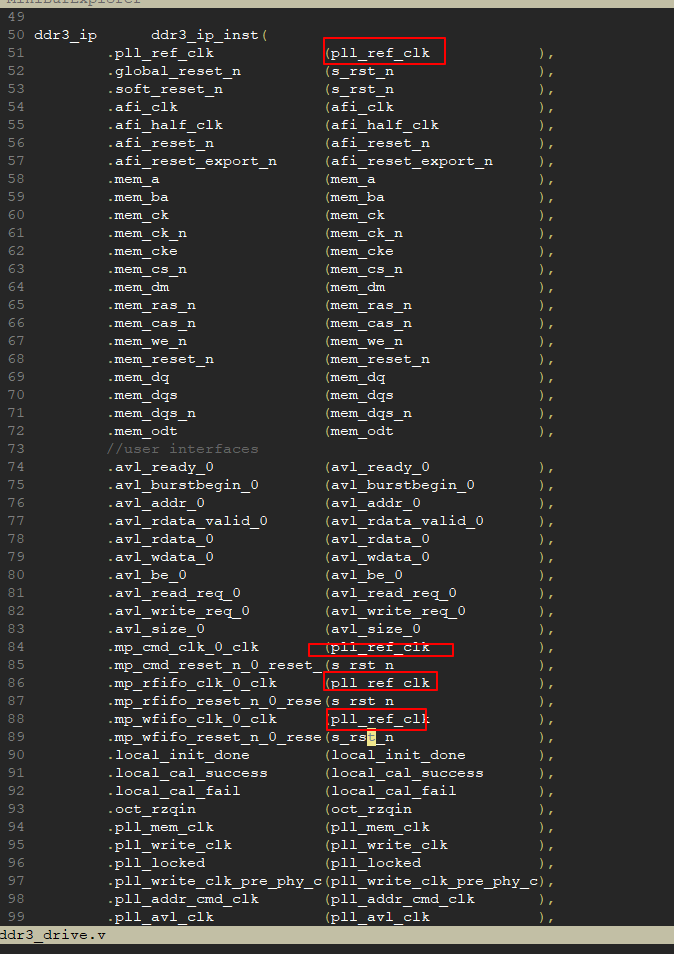

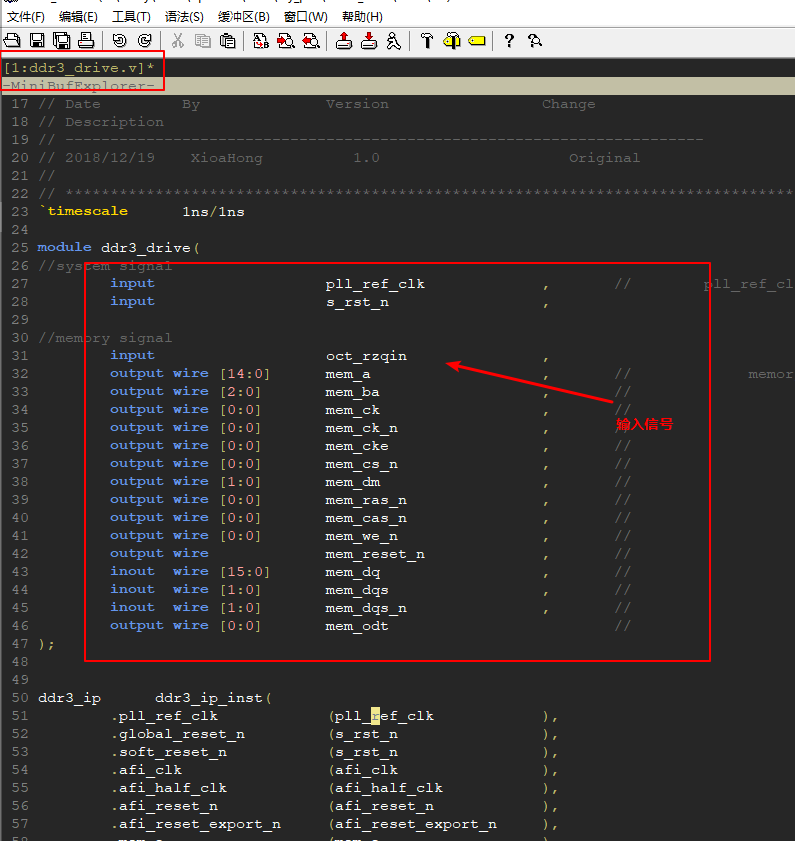

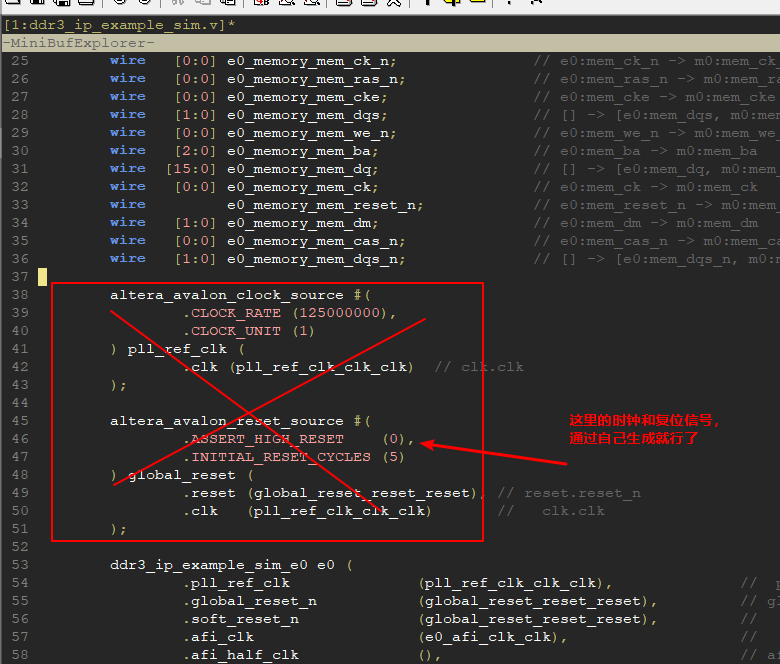

1.寫例化DDR3 IP核的頂層模組,將DDR3模組IP核例化一下。並且模板中的rst改成用系統的復位訊號。時鐘用系統的時鐘訊號。

2.將sim下的mentor裡面的tcl和模擬Demo中的do檔案放到自己的目錄下(tcl不是用這裡面的tcl檔案)。

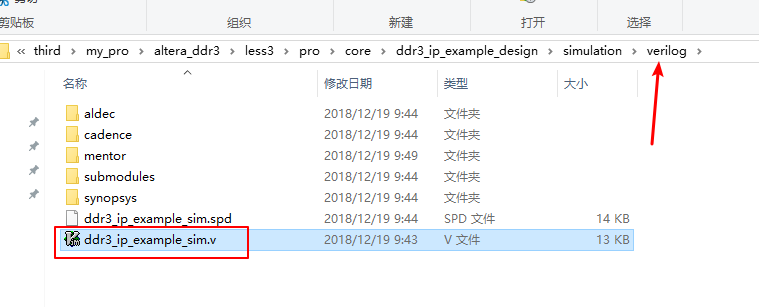

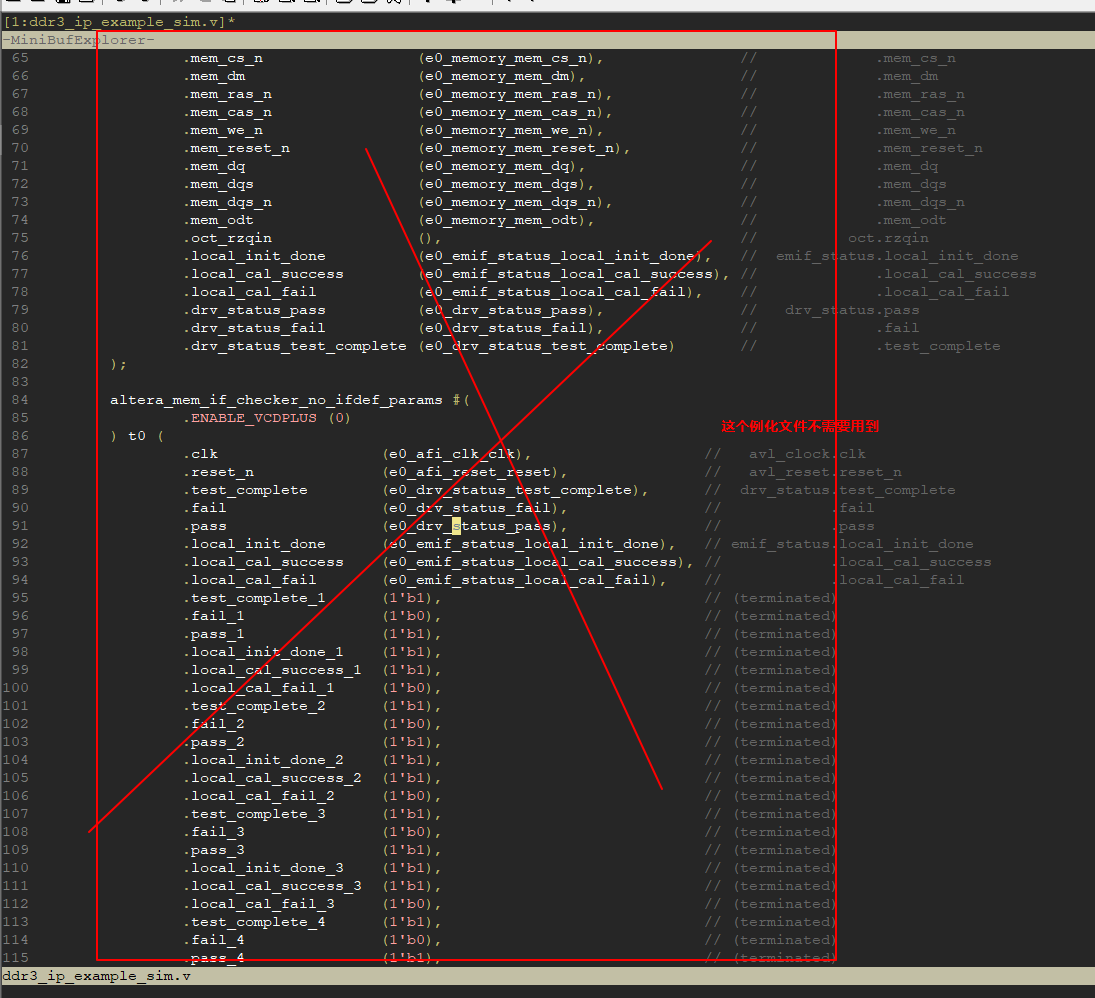

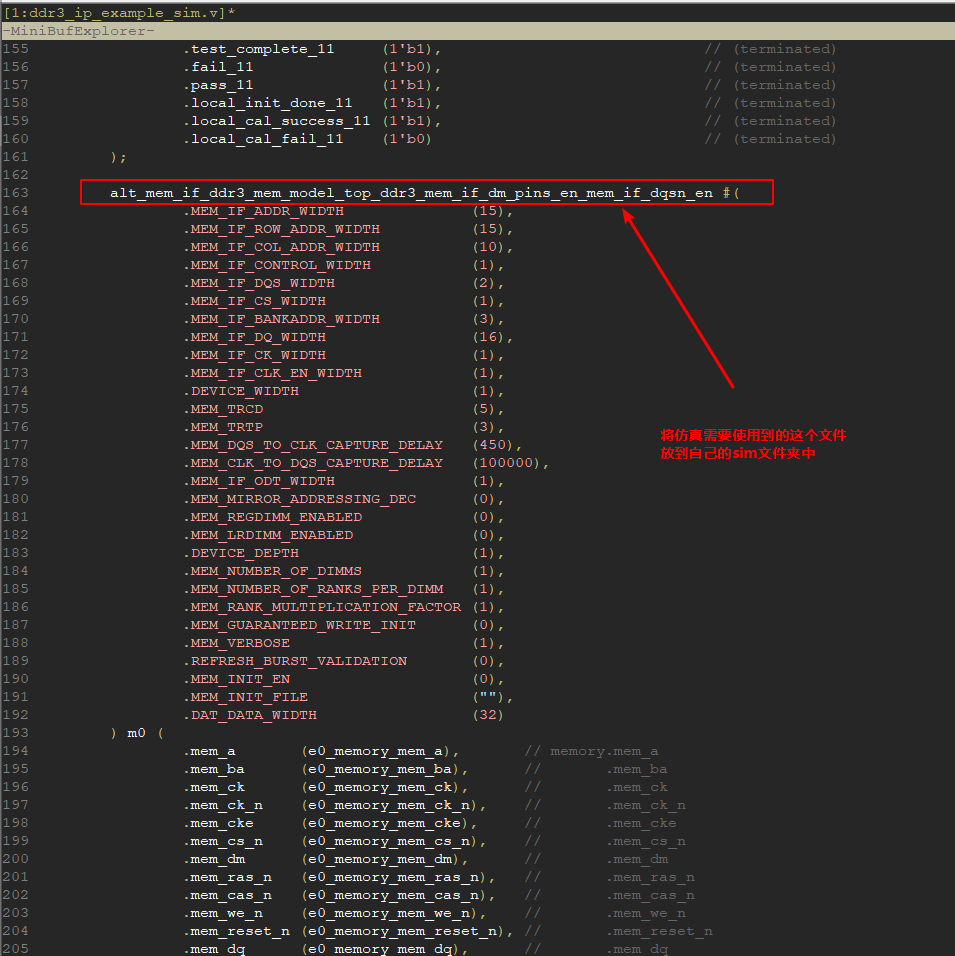

3.寫模擬tb檔案,模仿Demo的tb檔案就行,將ddr3_ip_example_sim.v這個檔案複製到自己的資料夾中,

然後將模擬檔案中需要用到的檔案放到sim資料夾中。

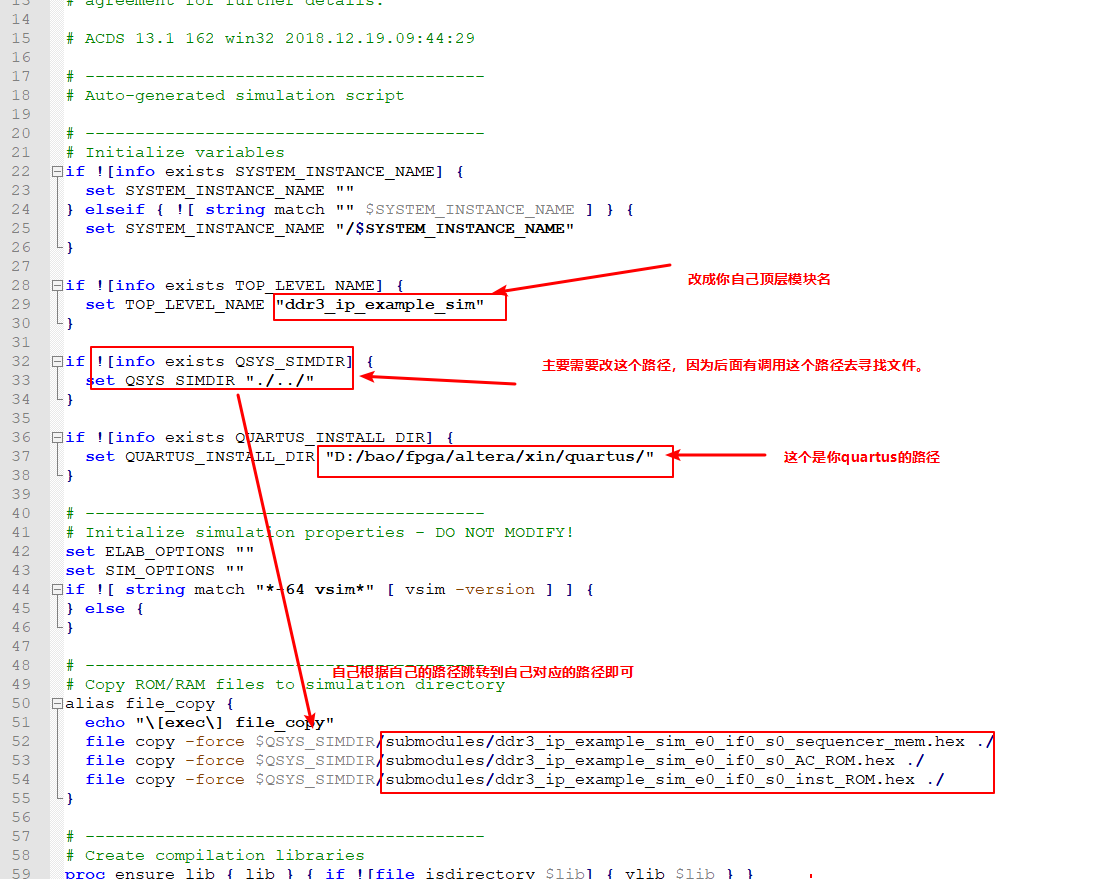

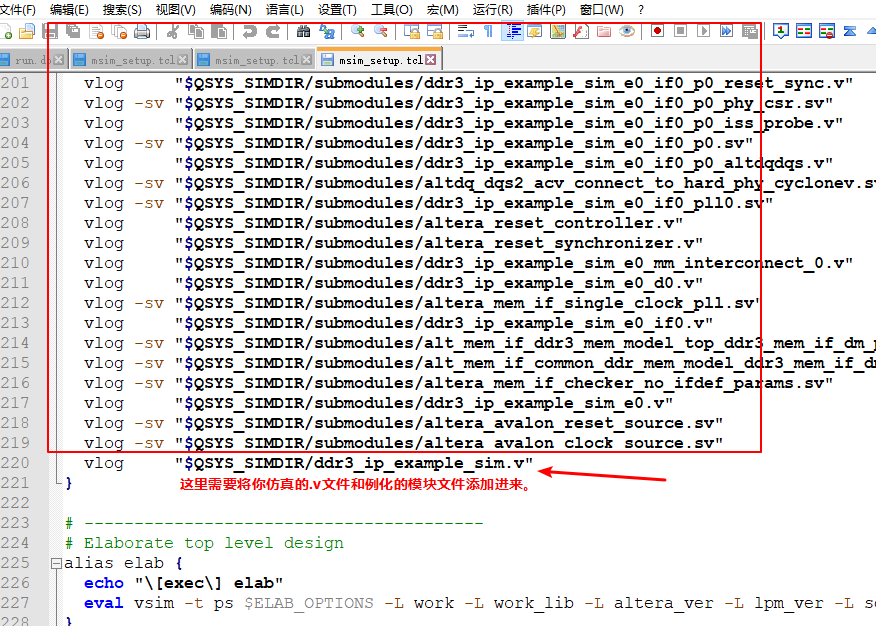

4.更改tcl指令碼檔案。主要是要修改TOP_LEVEL_NAME和

QSYS_SIMDIR這個路徑。然後將你自己寫的頂層模組新增到目錄下。因為tb檔案還包含了.sv字尾的檔案,vlog後面要+ -sv引數去編譯這個檔案。

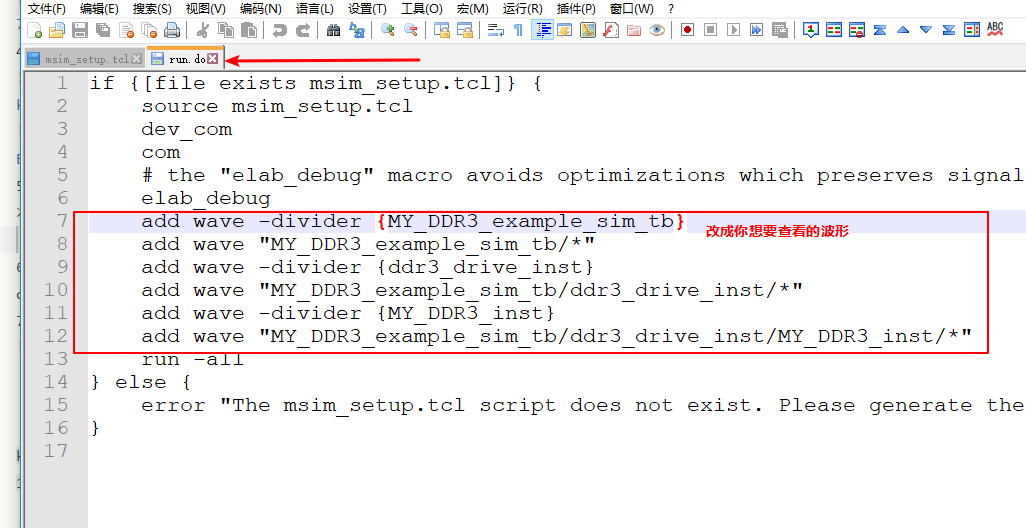

5.修改do檔案

將do檔案改成你自己需要觀看波形的檔名,將add wave改成你想要檢視波形的名字。

6.然後將modelsim的路徑改到你自己的路徑下,執行do檔案即可

7.自建模擬平臺的波形