FPGA的除錯-內嵌邏輯分析儀(SignalTap)(一)原理

對於FPGA除錯,主要以Intel FPGA為例,在win10 Quartus ii 17.0環境下進行模擬和除錯,開發板型別EP4CE15F17。主要包括一下幾個部分:

- FPGA的除錯-虛擬JTAG(Virtual JTAG)

- FPGA的除錯-線上儲存器內容編輯工具(In-system Memory Content Editor)

- FPGA的除錯-內嵌邏輯分析儀(SignalTap)

- FPGA的除錯-LogicLock

- FPGA的除錯-除錯設計的指導原則

上述內容主要參考《通訊IC設計》,有興趣的可以自己購買書籍進行研讀。

1、相關理論知識

1.1內嵌邏輯分析儀

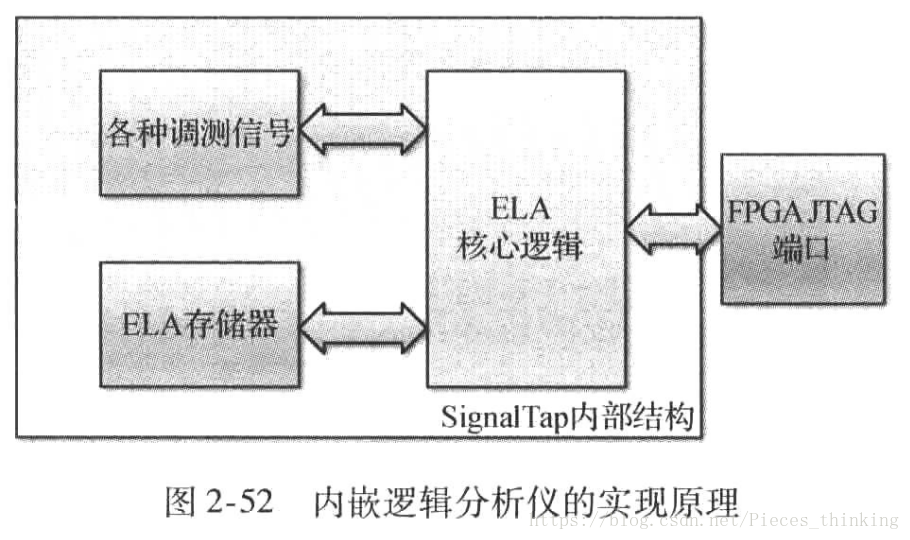

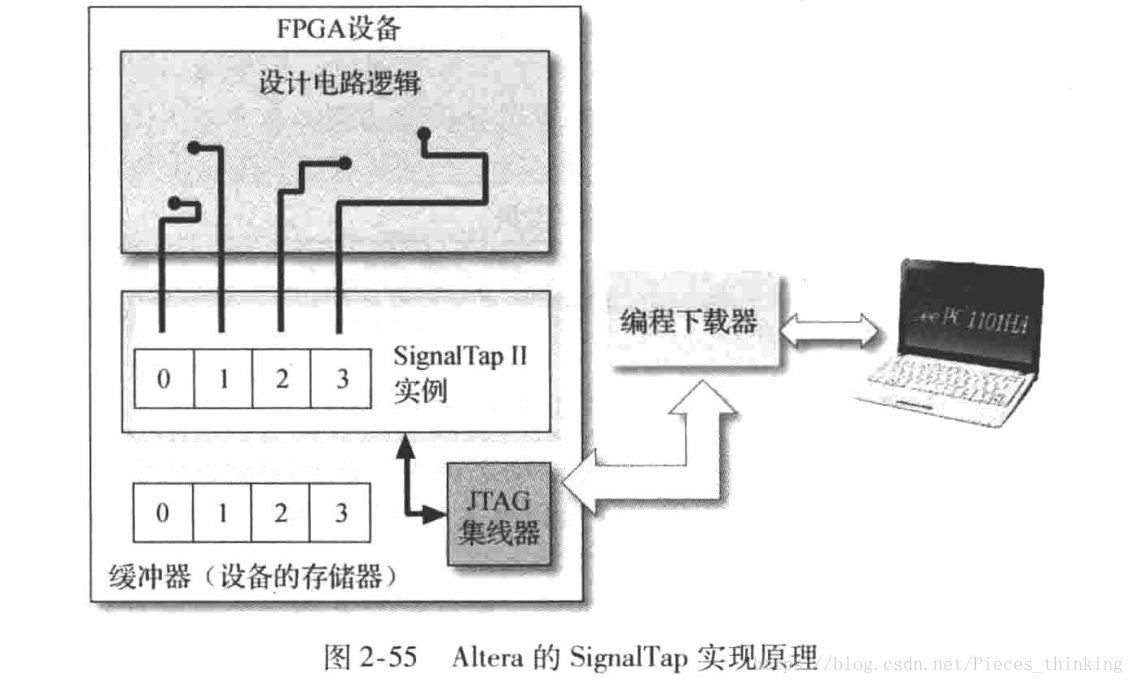

為方便使用者進行除錯,FPGA通常會內建訊號觀察邏輯,Altera提供的是GignalTap,而xilinx提供的則是ChipScope。此外還有第三方除錯工具,如Synopsys的Identify。這類工具的核心原理為:以預先設定的時鐘速率實時取樣FPGA的內部訊號或者引腳狀態,並存儲於FPGA的內部RAM中,然後通過統一的ELA(Embedded Logic Analyzer)進行資料分析和管理。當預設的觸發條件滿足後,ELA通過JTAG將儲存在片內RAM中的資料快取資料傳輸至PC上。當PC獲得JTAG回傳資料後,通過本地計算將對應的邏輯分析結果展現出來。

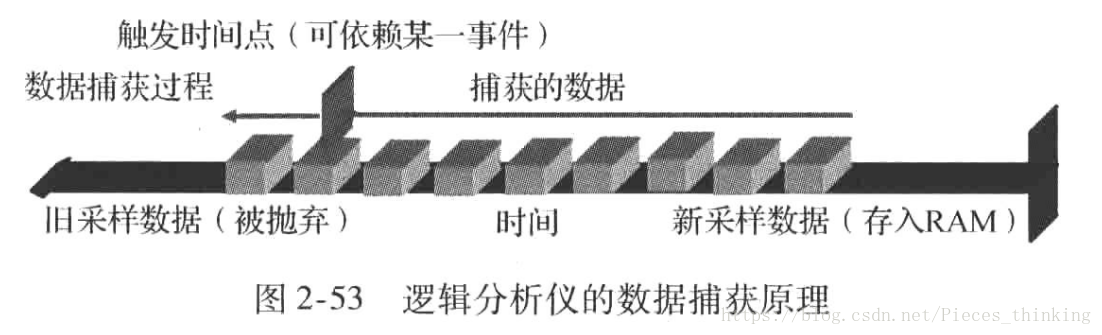

因此,無論是GignalTap還是ChipScope,其實都是在工程中額外加一些特殊模組實現訊號的採集,所付出的代價包括:邏輯單元、內部RAM以及ELA資源。邏輯分析儀的資料捕獲原理如圖2-53所示,所有儲存單元都是與當前邏輯設計的RAM共享的。如果當前邏輯佔用RAM較大,內嵌的邏輯分析儀功能將會有非常大的儲存深度限制。

從圖2-53很容易發現,邏輯觸發的時刻可以動態調整,而且儲存的資料長度與時間也很容易調整。此外由於FPGA內建可程式設計能力,所以觸發條件可以依賴於其他的事件觸發,這樣可以多級觸發,形成基於狀態的資料捕獲。

例如當A訊號為高電平,且持續32週期後,如果此時B訊號為低電平且C訊號有一個低脈衝,則觸發一個等待事件;當等待事件發生65536個時鐘週期後,再捕獲資料,並通過邏輯分析儀傳送出來。這就是基於狀態機觸發的邏輯分析功能,類似於Verilog中的Assertion斷言和FSM狀態機的有機結合體,是傳統邏輯分析儀無法完成的。由於現在的邏輯通常都比較複雜,基於傳統的條件觸發模式,往往耗時耗力,很難快速找到BUG;而狀態觸發往往能夠幫助設計者快速定位錯誤並除錯。

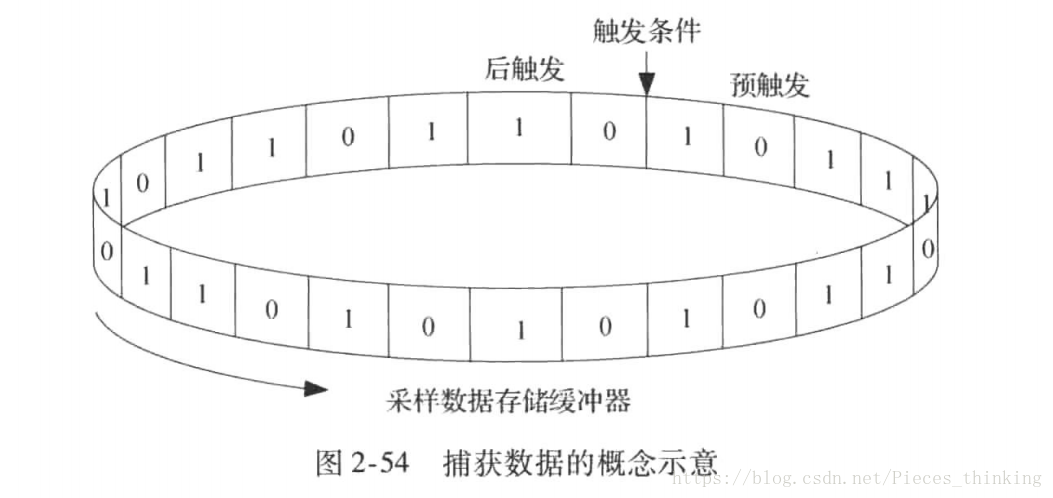

對於邏輯分析儀而言,除了觸發條件外,還有一個儲存位置的概念。正常情況下,FPGA會對需要CIA楊的資料一直取樣,當資料放滿後,將採用迴圈覆蓋的方式儲存,這類似於FIFO中的卷繞(WRAP)概念。當觸發器觸發後,通常緩衝器都是滿的;如果採用預觸發,將繼續記錄當前儲存容量12%的資料後停止(有些廠商是不再記錄,直接用當前記錄資料);如果採用後觸發,將繼續記錄當前儲存容量的88%的資料後,停止記錄(有些廠商是記錄全部容量);如果是中間觸發,將繼續記錄當前儲存容量的1/2的資料。實際上什麼時候開始記錄,什麼時候停止都可以通過狀態觸發實現。捕獲資料的概念示意圖如圖2-54所示。

下面通過SignalTAP為例,簡單講述內嵌邏輯分析儀的除錯技巧。

1.2 SignalTap

SignalTAP是Altera內建的邏輯訊號觀測工具,內部實現結構如圖所示。

根據前面的邏輯分析儀原理,很容易得知FPGA可以實現多個並行的ELA。通過FSM和條件判斷支援多級觸發,FPGA也能夠支援複雜的狀態機資料捕獲。令觸發條件加上一個計數器,就很容易使FPGA能在不同的起始時刻捕獲資料。而Altera所設計的SignalTAP正好是按照上訴方式設計的,其特點如下:

- 最大支援1024個數據捕獲通道

- 單個器件支援多個併發的邏輯分析模組,包括跨多個時鐘域的訊號

- 每個資料捕獲通道能夠支援10級觸發

- 支援在不同的位置進行捕獲,包括訊號前段、中段和後段。

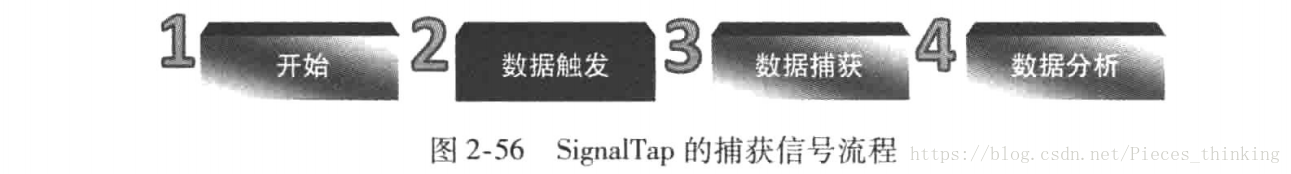

SignalTAP的捕獲流程如圖所示。

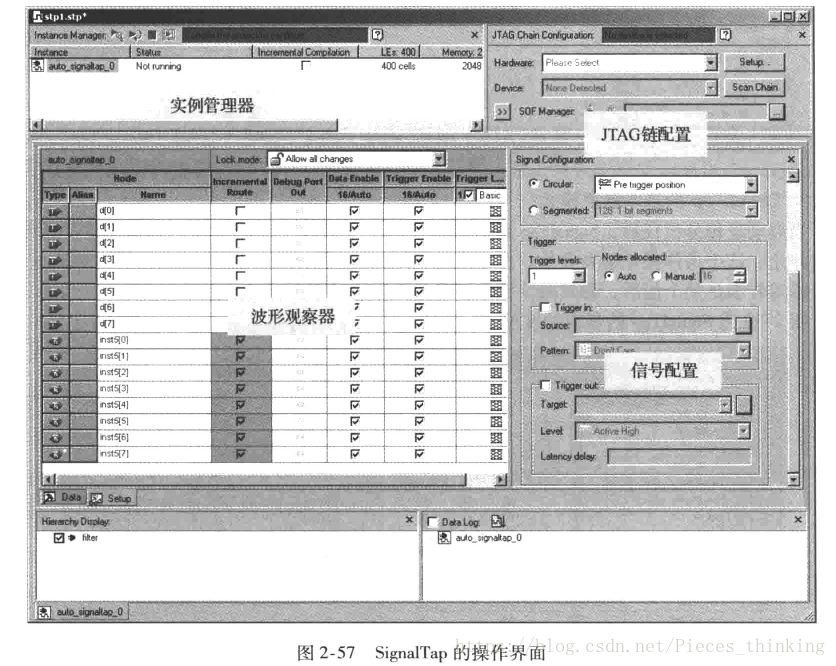

1.2.1 SignalTap的介面

操作介面如圖所示。

1.2.2 SignalTap的演示

演示放在例項裡

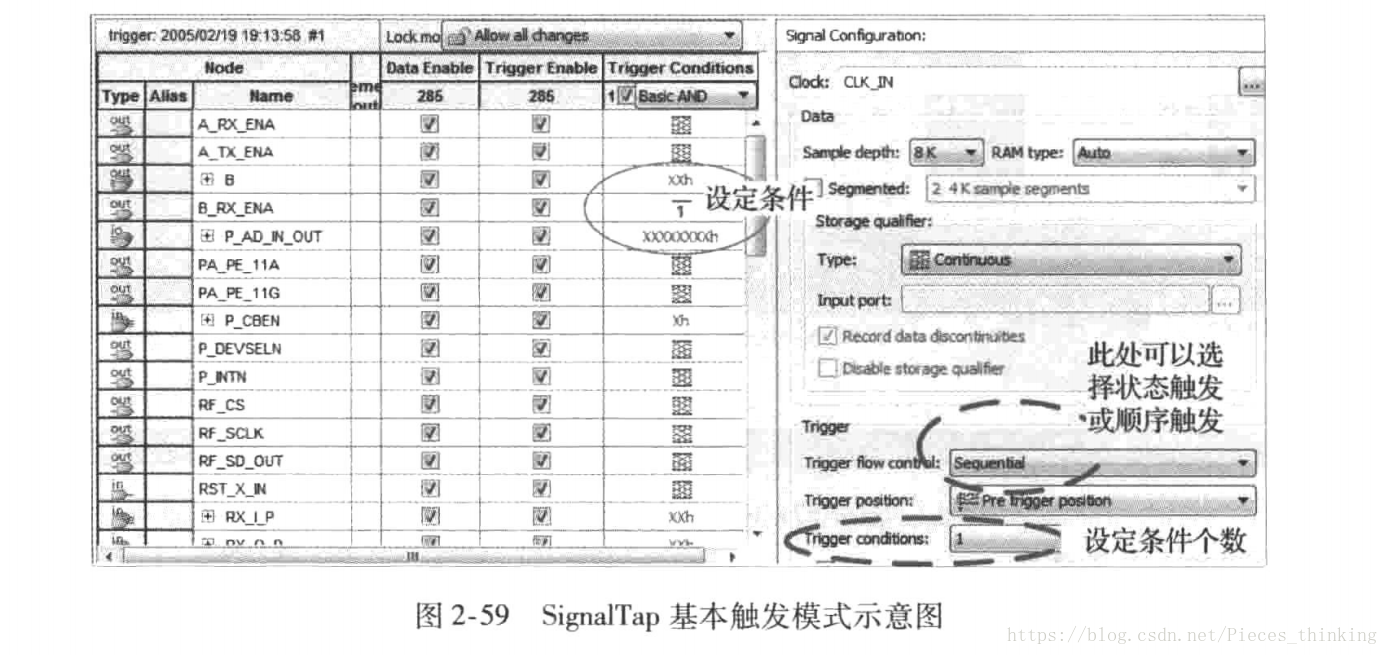

1.2.3 SignalTap的基本觸發模式

當啟動邏輯分析儀後,SignalTAP會對被監視的訊號進行不斷的取樣,一直到某個條件滿足後停止,這個條件就是觸發條件。在基本模式下,觸發條件被設定為當前訊號的邏輯組合。當邏輯組合滿足某個值後,觸發條件將被滿足,資料將被取樣儲存並上傳到PC。

下圖是SignalTAP的基本觸發模式示意圖。

1.2.4 SignalTap的Advanced Trigger模式

在訊號列表Trigger Conditions欄的頂端選擇Advanced,Advanced會彈出邏輯編輯器,在這裡可以設計一個複雜的觸發表示式。

1.2.4 SignalTap基於狀態觸發的觸發模式

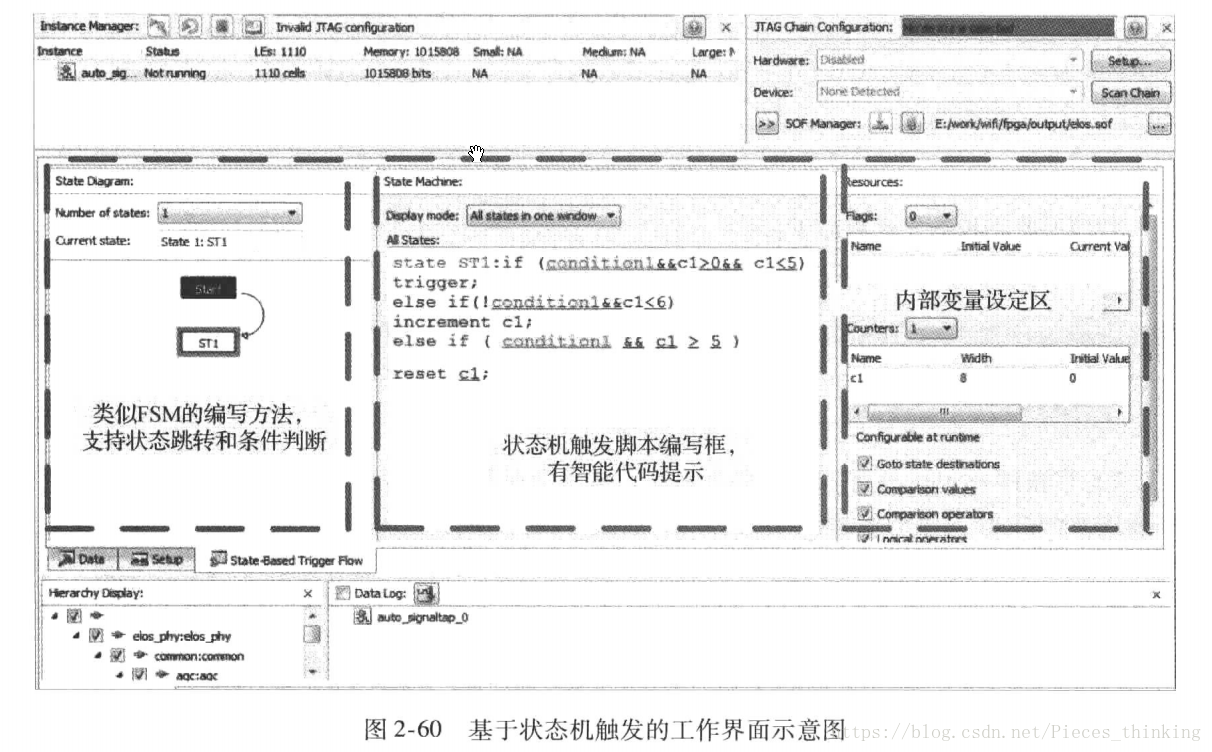

基於狀態觸發的邏輯分析儀模式是FPGA內嵌分析儀的而核心技術,主要技巧在於任何通過狀態觸發語句實現狀態機的觸發。下圖是狀態機觸發的工作介面。

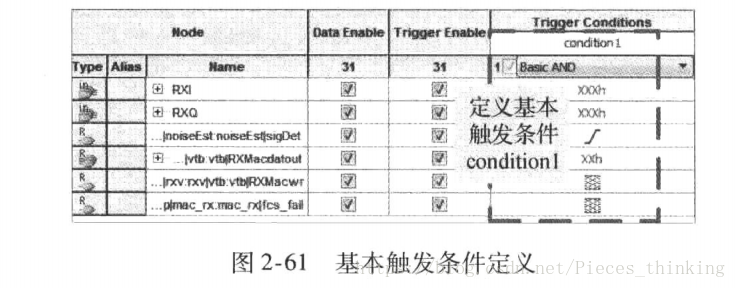

在設定觸發條件前,先需要確定基本的觸發條件,具體如圖所示。

在設定基本觸發條件後,就可以啟動狀態機的指令碼設計,下面通過幾個例子來說明狀態機觸發的實現方法:

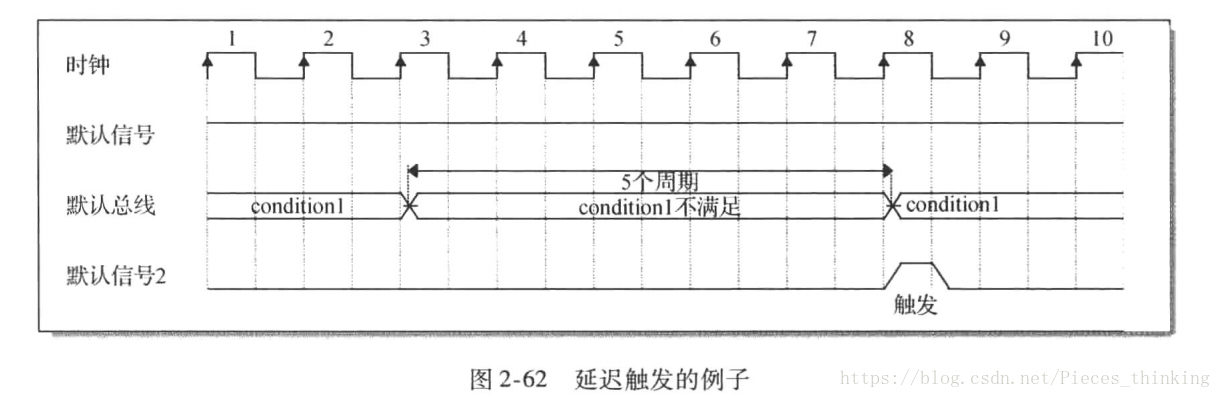

1)當條件condition1不滿足,且持續時間超過5個時鐘週期後,觸發觸發器,相關理想波形如圖所示:

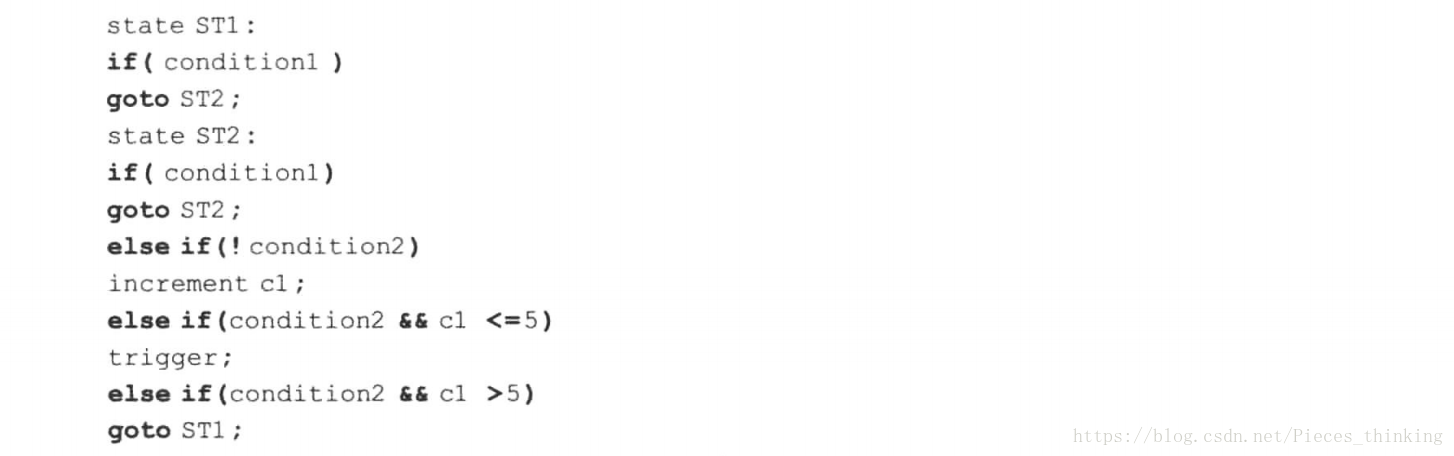

對應的狀態機觸發程式碼如下:

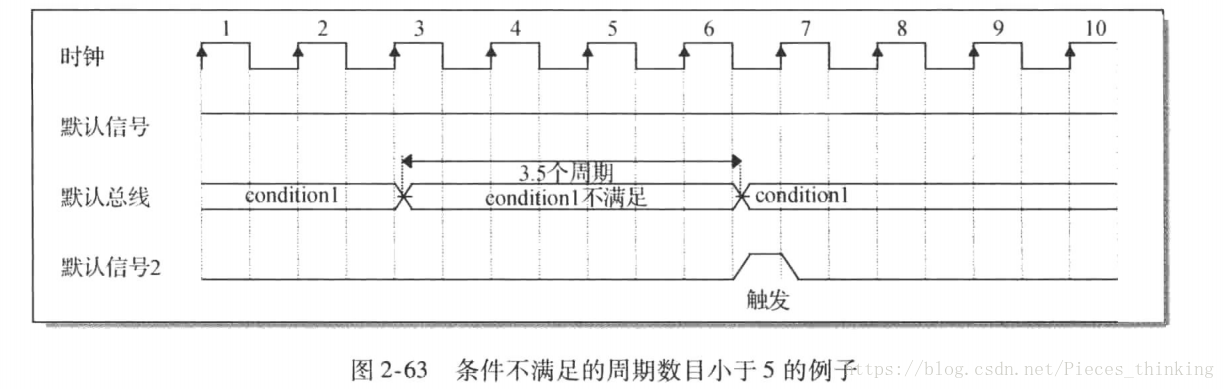

2)當條件condition1不滿足情況發生,且不滿足情況在不超過5個時鐘週期內,又發生條件condition1滿足的情況,則觸發觸發器,否則停止觸發。一個典型的例子圖下圖所示。

上訴觸發觸發器的指令碼如下:

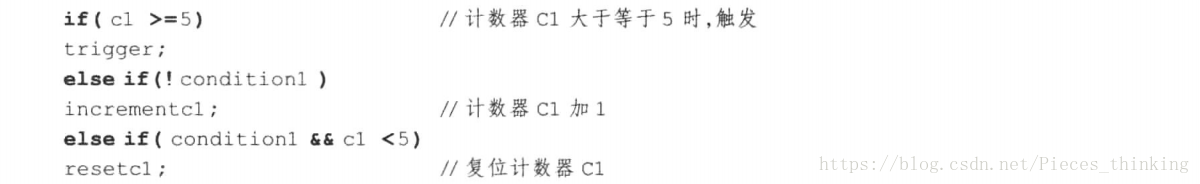

3)當condition條件滿足5次後,觸發觸發器,否則停止觸發。該例子的指令碼如下:

4)當condition1條件滿足後,如果condition2能夠滿足,則立即觸發觸發器,否則停止觸發。該例子的指令碼如下:

5)當condition1條件滿足後,如果5個取樣時鐘週期內,condition2能夠滿足,則立即觸發觸發器,否則停止觸發。該例子的指令碼如下:

由於任何複雜的條件都可以簡化為順序、分支和迴圈3種情況,通過計數器能夠實現迴圈,通過條件判斷可實現分支,而通過狀態機可實現流程控制。因此任意複雜的條件觸發,都能夠通過上訴條件組合捕獲。

前面所舉的5個例子,就是上訴不同場景的組合,因此讀者只需要將上訴5個例子進行組合就能基本掌握觸發條件的實現,熟練進行FPGA除錯。

2、簡單例項

留在下一篇吧。。。

傳送門 內容很豐富,點一下喲!