FPGA學習心得--01

1. Verilog

1.1 數字表示形式

例

:

多

少

位

的

什

麼

進

制

數

→

4

′

d

8

(

4

位

的

十

進

制

數

8

)

例:多少位的什麼進位制數 \rightarrow 4'd8 (4位的十進位制數8)

例:多少位的什麼進制數→4′d8(4位的十進制數8)

如果將

′

'

′ 一撇讀作漢字

的

的

的,Verilog的數字表示語法符合口頭語言的習慣。

1.2 資料型別

Verilog作為硬體描述語言,資料型別與硬體有直接對應關係。

| 資料型別 | 介紹 | 符號 |

|---|---|---|

| 暫存器 | 可以理解為一個抽象化的資料儲存單元,這與其他程式語言的變數概念很相近,只是Verilog以硬體暫存器作為變數的實現載體,而高階程式語言將使用一段記憶體來儲存變數值(或是CPU中的暫存器) | reg、integer、real |

| 線網 | 連線各個硬體功能單元的連線 | wire |

| 引數 | 有點類似於高階程式語言中的巨集定義 | parameter |

1.3 運算子

1.3.1 算數運算子

種類和功能和C其他程式語言一樣。

值得注意的是,乘除運算在底層實現時往往會比較消耗資源

1.3.2 拼接運算子

這個運算子是Verilog特有的運算子,作用是將兩個訊號繫結為一個訊號,例如:

{

a

,

b

}

→

將

a

,

b

兩

個

信

號

拼

接

起

來

作

為

一

個

新

信

號

\{a, b\} \rightarrow 將a, b兩個訊號拼接起來作為一個新訊號

{a,b}→將a,b兩個信號拼接起來作為一個新信號

1.3.3 賦值

| 符號 | = | <= |

|---|---|---|

| 含義 | 阻塞賦值語句 | 並行賦值語句 |

| 介紹 | 在always塊中,該賦值語句只有當前面的語句都執行完畢後才會執行,和其他順序執行的程式語言中賦值語句功能相同 | 在always塊中和其他語句並行執行,不等待上一條語句的執行結果 |

| 應用場景 | 1. assign語句 2. 不帶時鐘的always塊(組合邏輯) | 帶時鐘的always塊 |

1.3.4 其他

關係運算符; 邏輯運算子; 三目運算子 (條件運算子); 移位運算子

1.4 程式框架

model model_name ( input input_var_name output output_var_name ... ); parameter PAR_NAME =123 reg [:] reg_name wire wire_name assign wire_name = ... always @(posedge clk) begin if (...) else if (...) else end begin case(...) ... : ...; ... : ...; ... default : ; endcase end end endmodule

上面的虛擬碼定義了Verilog一個模組,begin、end的作用與C語言中的 " { } " "\{ \}" "{}"作用相同,begin、end程式碼段中的語句是順序執行的(並行賦值語句是例外)。為了保證程式碼的規範性,即使邏輯判斷分支中僅有一條語句,也可以用begin、end打包起來。

1.5 鎖存器

鎖存器與暫存器的最大區別是:鎖存器屬於組合邏輯,輸出電平變化僅與輸入訊號有關,不受時鐘約束。

鎖存器對輸入脈衝敏感,容易產生毛刺,這種瞬時的不確定性在後級電路中引發的BUG難以察覺。

另外由於FPGA中沒有現成的鎖存器資源,消耗底層資源。

鎖存器產生的原因往往是程式碼邏輯不完整。例如,if語句缺少else與之對應,case語句中沒有default等。

1.6 狀態機

1.6.1 狀態機適用的場景

某項工作需要按照固定的流程或步驟來完成,工作過程中總在各個階段之間切換。例子:升降機。

1.6.2 狀態機的優勢

開發人員在編寫程式碼時不需要考慮到所有狀態的排列組合,僅需要考慮各個工作狀態或工作階段之間的轉換條件。例如:升降機的控制程式不需要各個樓層分別編寫,而是通過狀態機來完成開關門、上升下降等動作。

1.6.3 狀態機的分類

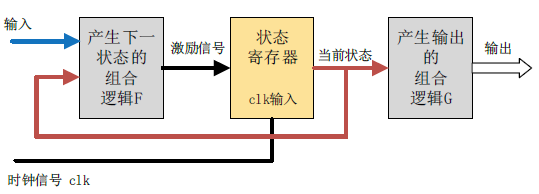

狀態機全稱“有限狀態機”。在電路實現上可以看作組合電路和時序電路的組合,狀態機的各個狀態往往是時序電路,而狀態之間的切換和輸出往往是組合邏輯實現的。根據狀態機的輸出是否和輸入相關,狀態機又分成“摩爾型狀態機”和“米勒型狀態機”。

| 狀態機分類 | 介紹 |

|---|---|

| 米勒型狀態機(Mealy) | 組合邏輯的輸出不僅取決於當前狀態還取決於狀態機的輸入 |

| 摩爾型狀態機(Moore) | 組合邏輯的輸出僅取決於當前的狀態 |

1.6.4 狀態機在Verilog中的寫法

1.6.4.1 二段式

一個always模組適用同步時序描述狀態轉移。

另一個always模組採用組合邏輯判斷狀態轉移條件,以及描述狀態機輸出。

1.6.4.2 三段式

一個always模組使用同步時序描述狀態轉換

一個always模組使用組合邏輯判斷狀態轉移條件

最後一個always模組用於描述狀態機輸出,可以採用時序電路,也可以使用組合電路。