FPGA設計思想(持續更新)

一、 流水線設計

將原本一個時鐘周期完成的較大的組合邏輯通過合理的切割後分由多個時鐘周期完成。該部分邏輯運行的時鐘頻率會有明顯對的提升,提高系統的性能用面積換速度

一個流水線設計需要4個步驟完成一個數據的處理過程,那麽從有數據輸入的第一個時鐘周期開始,直到第4個時鐘周期處理完第一個數據,但在以後的每一個時鐘周期都會有處理完成的數據輸出,流水線設計在開始處理時需要一定的處理時間,但以後就會不斷的輸出數據,從而大大提高處理速度。(面積換速度)如果不采用流水線設計,那麽處理一個數據就需要4個時鐘周期,而采用流水線設計則能夠提高將近4倍的處理速度

二、 跨時鐘域處理

有三種方法

- 打兩拍

- 異步雙口RAM

- 格雷碼轉換

1. 打兩拍方法

在進行uart串口通信的學習的過程中,遇到一個不理解的問題,在接收模塊中,小梅哥采取的設計方式是接收進行一步同步化處理,那麽為什麽要進行同步化處理呢?串口通信的設計,接收的波特率一般是發送波特率的16倍,單bit傳輸,我的理解是,在發送波特率下的串口數據傳輸到接收波特率下時,這個過程是跨時鐘的,對於小工程而言,不進行同步處理貌似沒有什麽關系,但是當工程對精度的要求比較強,外界幹擾比較大的情況下,我們就必須進行同步化處理,下面我將學習第一種針對單bit的跨時鐘域處理方法:打兩拍。打兩拍的方式,其實就是定義兩級寄存器對數據進行延拍。

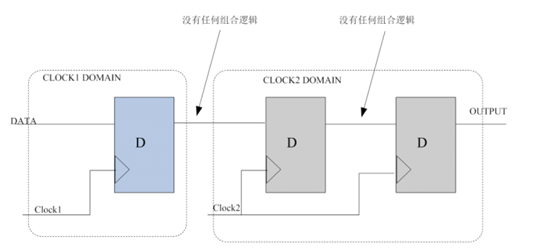

如上圖,第一個時鐘域將數據發送過來後,在第二個時鐘域裏用兩個D觸發器把接收數據進行延拍,中間沒有任何組合邏輯。

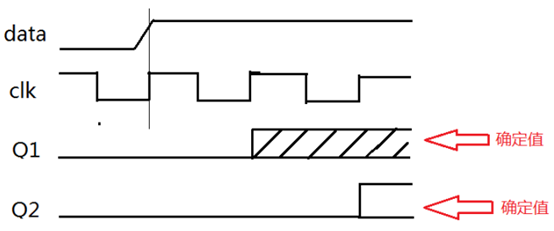

為什麽是進行兩級延拍呢?從上面的時序圖可以看出,data是第一個時鐘域的數據,Q1,Q2是第二個時鐘域的觸發器,在同一個clk時鐘下,假設當clk的上升沿來臨時,剛好采集到的數據是data的跳變沿(因為數據在有0變為1的時候,顯然不是垂直上去的,它有一個建立時間,所以clk的上升沿采集到跳變沿的情況是完全有可能的),這樣的話Q1接收的數據會處於亞穩態,但是我們至少可以保證,在clk下一個上升沿,data是穩定的,Q1基本上可以滿足第二級寄存器的保持時間和建立時間的要求,出現亞穩態的幾率會得到很大的改善。如果多加寄存器進行延拍,只是對Q2的數據進行了延拍,並沒有什麽意義,所以,我們選擇進行兩級延拍來處理單bit數據的跨時鐘域處理。

三、 一個讓我糾結了幾個月問題

一個讓我糾結了幾個月問題

Altera的板子按鍵按下去時0.不按下去是1,

Altera的板子按鍵按下去時0.不按下去是1,

Altera的板子按鍵按下去時0.不按下去是1,

重要的糾結說三遍

Xilinx的板子按下去時1,不按是0

FPGA設計思想(持續更新)