全網首創ISE入門級教程

轉眼間我已經大三了,現在成為了實驗室的負責人,對於下一屆學生的納新重任就交到了我的手上,想采取不同的方法暑假就可能對他們進行一些培訓,所以制作了此教程,說實話,在網上還沒有找到關於ISE的入門級使用教程呢!可謂是全網首創啊!話不多說,我們趕緊看看我的處女視頻教程吧!

互聯網是最好的學習平臺,讓貧富之間的教育資源差距減小,對於FPGA來說晚上的教學資料、視頻非常多,但是多數為Altera的QuartusII開發套件使用,而Vidado的使用貌似這兩年也多了起來,那麽ISE被拋棄了嗎?之前有過一個前輩做過關於ISE的使用教程,但那都涉及到攝像頭驅動的FPGA進階階段了,所以今天這套FPGA入門第一課的視頻教程,可真謂是全網首創關於ISE軟件的使用教程。這是西郵電院FPGA創新小組的納新公開課,FPGA入門第一課一位全加器的設計(ISE使用教程的百度雲盤鏈接在文章第五部分)。

一、 FPGA創新小組納新公告

FPGA創新實驗室處於西安郵電大學2號實驗樓(電子工程學院實驗樓)107實驗室。主要學習方向為數字集成電路設計(FPGA),每年九月份中旬進行納新,主要面向微電子系(集成電路和微電子專業)的16級學生。為了使納新結束後大家能夠快速進入學習狀態,我們暑假會針對納新考核進行相應的培訓,讓大家提前有一個對FPGA的認識並且能設計出一些簡單的電路。群文件有相關資料,請大家自行下載學習。前期需要大家將軟件下載安裝(鏈接如下),學習一些數電基礎知識(群文件有數電電子書康華光版),Verilog基本語法(請看群文件),後面的線上課程會再通知。大家有什麽疑問可以直接在群裏提出。

二、 FPGA是什麽

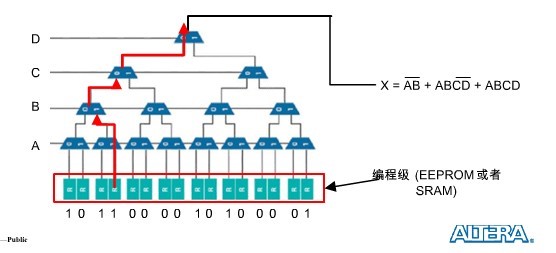

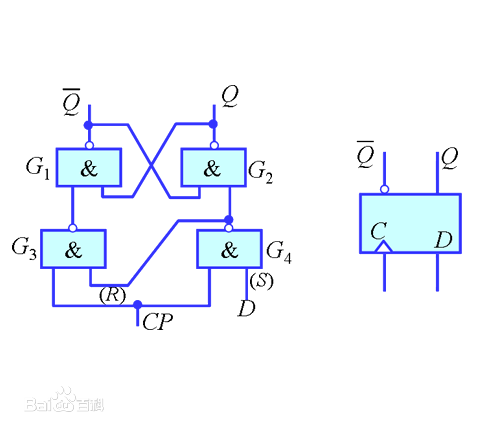

FPGA(Field-ProgrammableGate Array),即現場可編程門陣列,使用Verilog HDL(Hardware Description Language)進行描述,FPGA可以理解為把數字電路的元器件都集成到FPGA芯片內部,與門、或門、選擇器、D觸發器。實際上它內部構造是用FPGA利用小型查找表(LUT)來實現組合邏輯,每個查找表連接到一個D觸發器的輸入端,觸發器再來驅動其他邏輯電路或驅動I/O(input/output),由此構成了既可實現組合邏輯功能又可實現時序邏輯功能的基本邏輯單元模塊,這些模塊間利用金屬連線互相連接或連接到I/O模塊。

圖 - LUT實現原理圖

圖 – D觸發器

總的來說,它是利用verilogHDL硬件描述語言來描述數字電路,你所寫的代碼,映射到板子上實際上就是一些數字電路。

FPGA公司主要是兩個Xilinx和Altera(現intel PSG),我們目前用的ISE是Xilinx的開發套件,現在ISE更新到14.7已經不更新了,換成了另一款開發套件Vivado,也是Xilinx的產品,intel的開發套件是Quartus II系列,我們實驗室這兩款公司的開發板都有,不用對於入門來說,選擇ISE有兩個原因,一是它比Vivado快多了,二是它和Quartus II相比不用自己寫測試文件(激勵)。實驗室的板子這兩個公司都有,代碼都是可以移植的,學習的話都要學的,軟件不是問題,重點是FPGA的設計思想。

三、 FPGA與單片機的區別

對於單片機和FPGA的主要區別。單片機可以理解為跑程序的微型電腦,麻雀雖小五臟俱全,所以寫的代碼相當於程序,應該屬於軟件範疇。單片機寫出來程序,用編譯器編譯後實際上是一條條指令(MIPS指令),控制單片機去控制它的外圍器件。

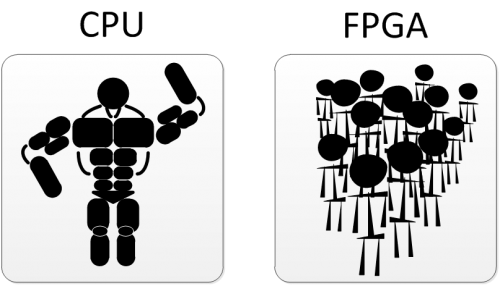

FPGA則應該理解為可編程的數字邏輯電路集成芯片,所以寫的代碼其實是在描繪一個數字邏輯電路。

兩者最大的區別應該是在速度上的區別,FPGA內部是並行的,所有的電路邏輯都是在同一個時鐘觸發下工作的,而單片機屬於單線程,內部屬於順序執行,一個執行完了再執行下一個。速度肯定要慢。

FPGA主要用於通信、圖像處理等領域,ASIC的設計驗證,就在去年到今年還有一個新的領域AI,用FPGA加速深度學習算法,BAT也都部署了FPGA雲服務器。因為其速度快的優點,所以用來處理數字信號是所擅長的。最經典的是2008年北京奧運會開幕式的畫卷顯示屏用的就是Altera Cyclone II FPGA驅動的。

在初學FPGA的時候容易的是把VerilogHDL當C語言來寫,把FPGA但單片機來用。寫的代碼不能稱之為程序,應該稱之為代碼,以區別和軟件的不同。

圖 – CPU與FPGA

四、 一位全加器的設計

需要基礎知識:二進制的加法運算、真值表、卡諾圖、Verilog HDL基本語法

1 + 1 =1 0; 1 + 0 = 1; 0 + 0 = 0;

全加器(Full Adder)

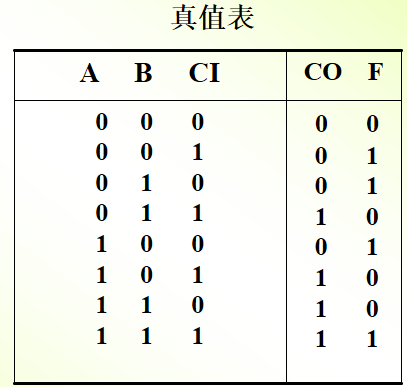

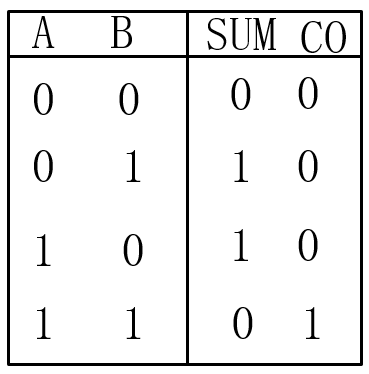

圖 - 一位全加器真值表

上圖是數電書上的全加器真值表,下圖是我自己畫的。

A和B為兩個加數,CI表示低位向本位的進位,CO本位向高位的進位。我們在這裏設計中用不到CI,設計超前進位加法器會用到。所以看右邊的圖就可以了。

Verilog有四種描述風格:晶體開關級描述風格、門級描述風格、數據流風格、行為級描述風格。

開關級描述風格太老我們不學。門級描述風格也太原始,交給你們數電老師去教。數據流描述風格雖然不常用,但是為了更加深刻理解組合邏輯的設計,所以後續課程在進行講解。今天我們就用最簡單,最迅捷的行為級描述來描述這一個一位加法器。

五、 ISE14.7使用流程

-

FPGA創新小組納新公開課class1:百度雲鏈接:http://pan.baidu.com/s/1bpAgmtD 密碼:psx2

視頻中有詳解

-

ISE14.7與Notepad++級聯:http://www.cnblogs.com/ninghechuan/p/6172237.html

-

註意

(1) Wire型數據只能能在assign語句裏賦值

(2)Reg型數據只能在initial塊,always塊,for賦值

六、 課後練習

-

重新新建一個工程,自主設計一個四位全加器,要求有仿真。最終將工程打包發送至我的郵箱ningh[email protected],可以編寫一份文檔對設計進行概述和說明,附加學習心得和感想

七、 你能得到什麽

-

首先是提高動手能力,很多東西自己動手做一遍和你從課本上學理論的感受是不一樣的。

-

我們實驗室每年都會組織參加各類電子競賽,增強項目實踐能力。

-

增加考研就業競爭力,

-

實驗室有空調,有空調,空調,調。

全網首創ISE入門級教程