STIL文件(DFT/IC測試方向)

相信很多工程師,特別是剛入行或準備入行的兄弟們或多或少聽過測試相關的東西。如果你想做DFT工程師的,測試工程師的,而對於設計/驗證工程師們如果能了解下STIL文件的原理,在和DFT/測試工程師聊技術聊測試pattern的時候就不會一臉懵逼了。

言歸正傳。STIL就是StandardTestInterfaceLanguage(標準測試接口語言),IEEE1450.x標準就是專門說的它,語法上很有內涵的感覺。但很明顯這就是用來描述測試pattern用的語言(Synoposys會采用STIL來描述掃描測試的過程,也就是SPF),就像verilog是用來描述硬件電路的語言一樣,會有很多語法規則。那我們來好好詳談語法規則?你肯定暈菜,我也會暈的......所以放棄吧。

通常STIL格式的pattern文件都是工具生成出來的,自己要像用verilog寫設計一樣寫一個完整的pattern文件,這個......你還是讓我回家種地吧。

其實對這門語言的了解不需要很深入,只需要能夠讀懂,然後能依葫蘆畫瓢的做點小修改就夠用了。好了,下面就跟著我來看看應該怎麽快速讀懂一個STIL描述的pattern文件。

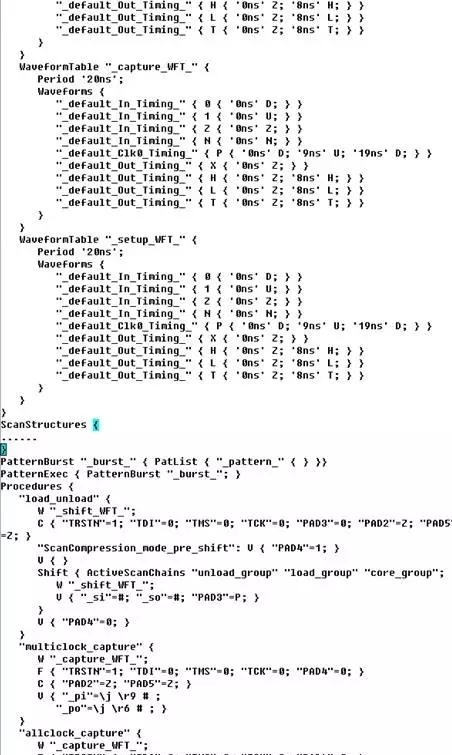

請看這個例子:

這是一個比較簡短的掃描測試STIL格式的pattern文件,從左往右基本顯示了主要的幾個部分。看到這樣一個文件,感覺無數草泥馬在眼前飛奔有木有?

我們這時需要思考一個問題,那就是這樣一個文件記載的究竟是什麽邏輯?既然是測試用的pattern文件,顯然它最主要的功能就是描述測試所需要用到的輸入輸出管腳信號名,以及測試的過程。這個過程就包含如何給激勵和給什麽激勵,以及最後期望得到什麽輸出和如何判斷比較輸出。從這個角度出發看待這個文件的話,其實就不難了。

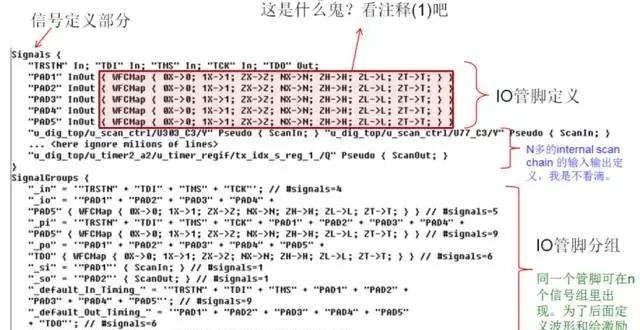

首先看看測試用的輸入輸出管腳怎麽描述的:

(1)這個有點復雜。是定義後面WaveFormTable和vector裏給的值的含義。註意這裏這個定義是針對雙向IO的,”0X”就表示給’0’輸入激勵同時不做任何輸出期望,在vector中就用’0’來完全表示,即有這樣的映射定義”0X->0”。0就是輸入0,1就是輸入1,Z就是高阻輸入,N就是沒有輸入,X表示不期望輸出,H表示期望輸出高,L表示期望輸出低,T表示三態輸出。

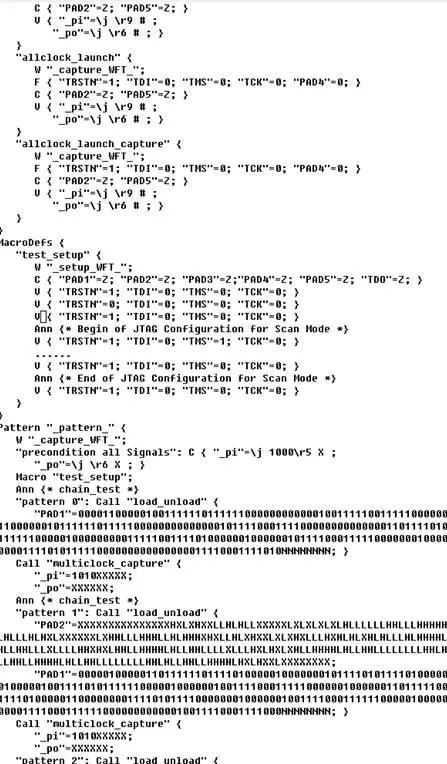

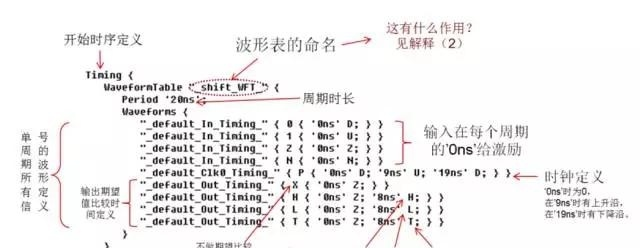

管腳信號的定義有了,那下面就該是定義這些管腳的輸入輸出的時序波形了,這個定義模塊就是Timing裏的WaveFormTable了。這個很重要,基本看懂了這個,就看懂了這個STIL文件的一半。在講解這個時序波形定義之前,需要普及以一個小概念,不然理解要講的東西就費勁了。這個概念就是測試波形的周期化。簡單說來就是測試過程中,所有信號的激勵都是按照時鐘的周期一個周期一個周期給的,對輸出的期望也是一個周期一個周期進行對比檢查的。所以測試pattern在波形上是很有規律性的,而這個規律性就是通過下面WaveFormTable來定義的:

這個掃描測試過程定義中的”load_unload”過程就是定義常說的”shift”過程,因為在”shift”過程中,既有掃描輸入(load)又有掃描輸出(unload)。另外這裏有四個(怎麽又是四???別想太多,純屬巧合,如有雷同。。。)”*_capture”過程的定義,這個是為不同的pattern類型準備的。在後面具體的pattern裏會有調用聲明要用哪個capture過程。

有沒有發現,其實STIL文件裏也是一套套一套,套路相當深。

到這裏,其實我們已經差不多可以在腦子裏對這個掃描測試的波形有概念了,基本可以畫出個大概的波形圖了。

具體的波形就要依據定義在Pattern模塊裏的vector賦值給TMS,TDI和PAD1了。TDO和PAD2是輸出,實際輸出波形是依賴內部電路邏輯的,可以說不可知,但是我們可以對他們的輸出作期望值比較,這個在Pattern模塊裏也是有給定的。

到此為止,相信你已經也可以比較輕松的看懂這個STIL格式的掃描pattern文件了。突然發覺其實也不難。

額外說一句,與STIL格式類似的還有WGL格式,在理解波形上思路是一致的,在語法上也是有很多相通的地方。

STIL文件(DFT/IC測試方向)