關於並發可見性的一點理解

在看 《深入理解計算機系統》(CSAPP)第6章存儲器層次結構 的時候突然想到在java並發編程 中的 可見性的問題,在這裏簡單記錄一下,也不一定正確 ^_^

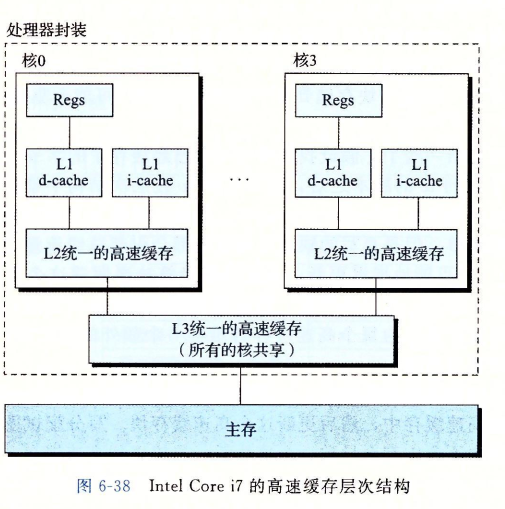

我們從上面的圖中可以看到Intel Core i7 中有4核,每一個核心中都有獨立的L1 L2 高速緩存, 四個核心共享L3高速緩存。

假設L1 L2高速緩存在數據寫的時候采用的是寫回的策略,簡單來說就是僅僅更新高速緩存中的數據,這有在根據替換策略這條數據將要被新數據替換的時候才寫回到更低層次的存儲器中。

那麽現在有這樣的場景: 每一核中都運行著一個線程,而這些線程共享同一變量a,如果線程0(運行在核0)對變量a執行寫操作,那麽從圖中我們可以看到僅僅會更改核0中的L1高速緩存,另外三個核上運行的線程在寫回操作(準確的說是 核0需要至少寫回到L3,而另外三個核重新從L3讀)前是不會看到這次寫操作的,這就是並發編程中的寫可見性問題。

以上這是暫時的理解,留作記錄以後補充。

關於並發可見性的一點理解

相關推薦

關於並發可見性的一點理解

ava ima 深入理解 補充 並發編程 緩存 png java mage 在看 《深入理解計算機系統》(CSAPP)第6章存儲器層次結構 的時候突然想到在java並發編程 中的 可見性的問題,在這裏簡單記錄一下,也不一定正確 ^_^ 我們從上面的圖中可以看到Inte

java 並發原子性與易變性 來自thinking in java4 21.3.3

tom element mat check vol 競爭 -s argument track java 並發原子性與易變性 具體介紹請參閱thinking in java4 21.3.3 thinking in java 4免費下載:http://downloa

高並發高性能場景(搶購、秒殺、搶票、限時競答)解決方案

網絡 讀寫分離 border 分布式系統 col 是把 qps 情況 自動註冊 技術指標: PV(Page View, 頁面瀏覽量)在千萬級別QPS(Query Per Second, 每秒處理請求數)在百萬級別數據量在千億級別接口響應速度不能超過150毫秒用戶提交請求到頁

15套java架構師、集群、高可用、高可擴展、高性能、高並發、性能優化、Spring boot、Redis、ActiveMQ、Nginx、Mycat、Netty、Jvm大型分布式項目實戰視頻教程

mycat 擴展 並發解決方案 入門到 -1 高端 資料 src nio * { font-family: "Microsoft YaHei" !important } h1 { background-color: #006; color: #FF0 } 15套java

[轉]Golang號稱高並發,但高並發時性能不高

大量 異步操作 而不是 需要 數據返回 管道 是否 回收 連續 1.管道chan吞吐極限10,000,000,單次Put,Get耗時大約100ns/op,無論是采用單Go程,還是多Go程並發(並發數:100, 10000, 100000),耗時均沒有變化,Go內核這對cha

2018最新技術Java架構師高並發高性能高可用分布式集群電商緩存性能調優設計模式項目實戰視頻教程

tcp ice cti HA 統架構 朋友 ear ppc iat 36套精品Java精品高級課,架構課,java8新特性,P2P金融項目,程序設計,功能設計,數據庫設計,第三方支付,web安全,高並發,高性能,高可用,分布式,集群,電商,緩存,性能調優,設計模式,項目實戰

39套精品Java從入門到架構師|高並發|高性能|高可用|分布式|集群|電商緩存|性能調優|設計項目實戰|視頻教程

mon 高並發 三十七 大數據高並發 教程 功能設計 lesson java高級 spring 精品Java高級課,架構課,java8新特性,P2P金融項目,程序設計,功能設計,數據庫設計,第三方支付,web安全,高並發,高性能,高可用,分布式,集群,電商,緩存,性能調優,

同步異步,並發並行概念的理解

刪除 等待 系統 同一時間 概念 時間間隔 計算 修改 運行時 同步與異步:同步:發送一個請求,等待返回,然後再發送下一個請求 異步:發送一個請求,不等待返回,隨時可以再發送下一個請求 同步可以避免出現死鎖,讀臟數據的發生,一般共享某一資源的時候用,如果每個人都有修改權限

Java從入門到架構師|高並發|高性能|高可用|分布式|性能調優|設計模式|大型電商項目

還要 兼容 原型 簡單 pro 圖片 性能調優 構圖 重點 沒有設計的思想,你就不能成為一名架構師。架構師是一個能擼的了一手好代碼,畫的了一個漂亮的UML/原型,寫的了一篇技術文檔,更加能解決好項目關鍵技術的綜合人才。架構師=前端工程師+後端程序員+系統分析師+關鍵技術解決

架構師項目實戰高並發高性能

項目實戰 之前 ima 三層 inf 詳細 and 可用 訂單 架構以及我理解中架構的本質 在開始談我對架構本質的理解之前,先談談對今天技術沙龍主題的個人見解,千萬級規模的網站感覺數量級是非常大的,對這個數量級我們戰略上 要重 視 它 , 戰術上又 要 藐 視 它。先舉個

談談我對JAVA記憶體可見性的理解 JAVA

首先要明確一點,每個執行緒都有屬於自己的工作記憶體。 出了執行緒自己擁有的工作記憶體外,還有公共記憶體。 假設我們有一個變數i,然後我們啟動兩個執行緒,這個時候i就會被拷貝成兩份副本分別給兩個執行緒的工作記憶體。 然後,這兩個執行緒如果對i進行操作,系統首先會將改變後的i先寫到執行緒的工

PHP秒殺系統 高並發高性能的極致挑戰

target redis 刷單 -a 我們 功能開發 目標 訪問速度 活動 第1章 課程介紹秒殺系統在各種網站和應用中經常會用到。本課程從基本的系統設計和基礎功能開始教導大家用PHP來設計和實現秒殺系統,並且為海量並發提供更高級的技術方案和實現手段。 1-1 課程導學1-2

網站高並發優化性能調優總結

靜態 查找 產生 奔潰 根據 打開 地方 siam 總結 最近在對PHP網站高並發高性能有所領悟,今天寫一篇關於這方面的文章。今天用我的測試站點:http://zhimo.yuanzhumuban.cc/來講解實例。 支模網整體開發到上線為10個月左右,後端

大話SQL Server性能優化(MSSQL高並發、性能調控、實踐)

索引 sha 簡單 系統性能 密碼 速度 ref 多應用 通過 大話SQL Server性能優化(MSSQL高並發、性能調控、實踐)網盤地址:https://pan.baidu.com/s/1KxdfcQD0XGD3M2ja_Y7UWQ 提取碼:435v備用地址(騰訊微雲)

java並發:CopyOnWriteArrayList簡單理解

內存 arr cif spa pen obj boolean iter list Java集合的快速失敗機制 “fail-fast” "fail-fast"是java集合的一種錯誤檢測機制,當多個線程對集合進行結構上的改變的操作時,有可能會產生 fail-fast 機制。

分布式架構、高可擴展、高性能、高並發、性能優化,微服務

消息總線 通過 dubbo dock 用戶 soc 銀聯 跟蹤 二維 微服務專題 你還不知道微服務?怎麽加(zhuang)薪(bi) SpringBoot 與微服務的區別於聯系 快速構建SpringBoot工程 SpringBoot核心組件剖析 快速集成mybatis實戰

PHP秒殺系統 高並發高性能的極致挑戰

靈活 課程 才有 ... lnmp平臺 高性能 單表 mysql 秒殺系統 第1章 課程介紹秒殺系統在各種網站和應用中經常會用到。本課程從基本的系統設計和基礎功能開始教導大家用PHP來設計和實現秒殺系統,並且為海量並發提供更高級的技術方案和實現手段。第2章 系統技術選型分析

原子性和可見性的理解

併發程式設計中常見的兩個問題:原子性和可見性,雖然經常討論,但是隻是停留在應用層面,理解仍然還不是特別深刻。做個筆錄加深一下自己的理解。 原子性:定義為不可被分割的操作。單個指令可以是原子的,多個指令通過加鎖的方式也可以實現原子性。原子性可以是針對單核多執行緒,也可以針對多

Java高並發高性能分布式框架從無到有微服務架構設計

創建 最終 轉移 lis 分布式 err 靜態頁面 提升性能 squid 微服務架構模式(Microservice Architect Pattern)。近兩年在服務的瘋狂增長與雲計算技術的進步,讓微服務架構受到重點關註 微服務架構是一種架構模式,它提倡將單一應用程序劃分

聊聊高並發(十九)理解並發編程的幾種"性" -- 可見性,有序性,原子性

sock clas 關註 條件 infoq zed 應該 單獨 ssa 這篇的主題本應該放在最初的幾篇。討論的是並發編程最基礎的幾個核心概念。可是這幾個概念又牽扯到非常多的實際技術。比方Java內存模型。各種鎖的實現,volatile的實現。原子變量等等,每個都可以展開