淺談Verilog HDL代碼編寫風格

消失了好久,沒有寫文章,也沒有做筆記,因為最近再趕一個比賽,時間很緊,昨天周六終於結束了,所以趁著周末這會兒有時間,寫點東西,記錄下來。首先我學習FPGA才一年多,我知道自己沒有資格談論一些比較深層次的問題,對於這個行業來說可能我才是一直腳踩在門外面。所以這篇文章是寫給一些剛開始學習FPGA、Verilog HDL的同學,我看過一些大神寫的代碼,然後盡量模仿大神寫法,經過好幾個大神的影響和自己的習慣摸索,最終算是總結出了一套自己的代碼書寫風格,當然我的代碼風格還是一直在進化中。現在將自己的一些經驗總結出來,希望對剛開始學習FPGA的朋友有所幫助。

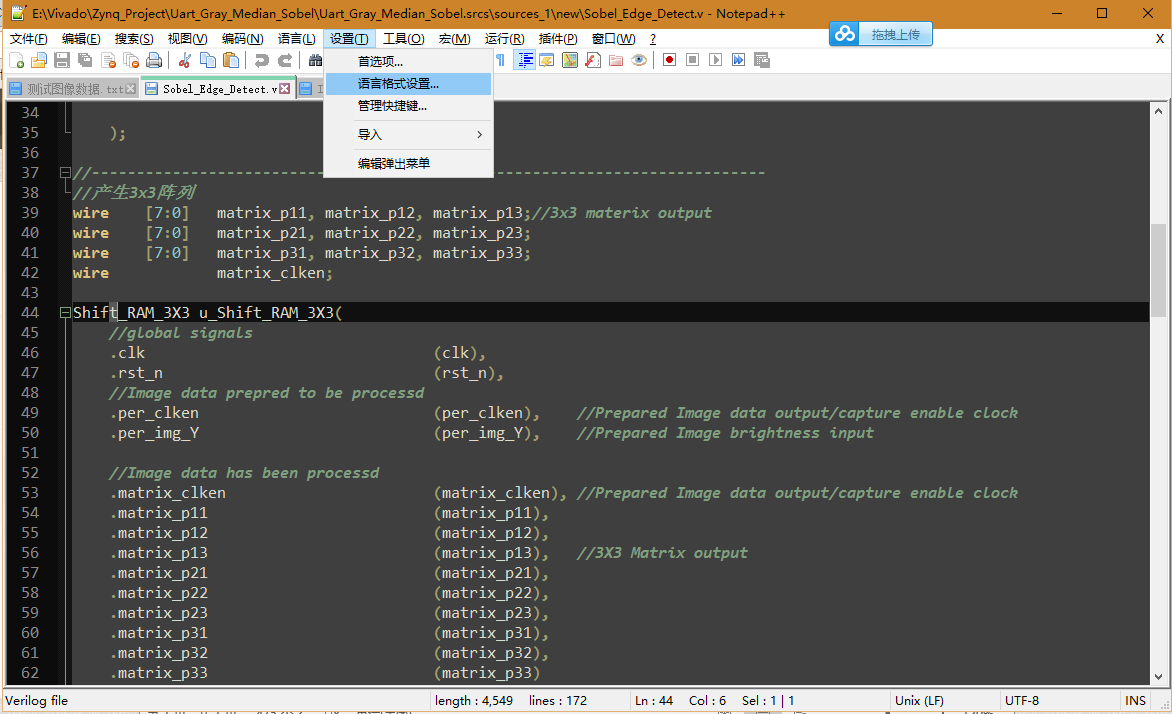

首先,第一我還是要強調的是編輯器的作用,工欲善其事,必先利其器。之前整理過一篇,如何高效的編寫Verilog HDL——菜鳥篇,點擊查看。其中我介紹了使用notepad++的一些小技巧,當然還有很多網友使用gvim編輯器,對gVim編輯器,我也了解了很多,雖然上手比較麻煩,但是一勞永逸,我之後也是打算學習該編輯器的使用的,目前,時間比較緊,所以就暫且先用notepad++吧。熟悉verilog的人都知道,Verilog HDL設計其實使用20%的語法就可以設計出90%以上的電路,其中最長用的便是always塊了,用軟件自帶的IDE的話編寫效率其實是很差的。所以說一個好的順手的編輯器至關重要,對於我們這些苦逼的技術工作者來說,經常看電腦屏幕一看就是一整天,然後還天天看,所以用Notepad++更換主題可以更好的為革命保護視力,

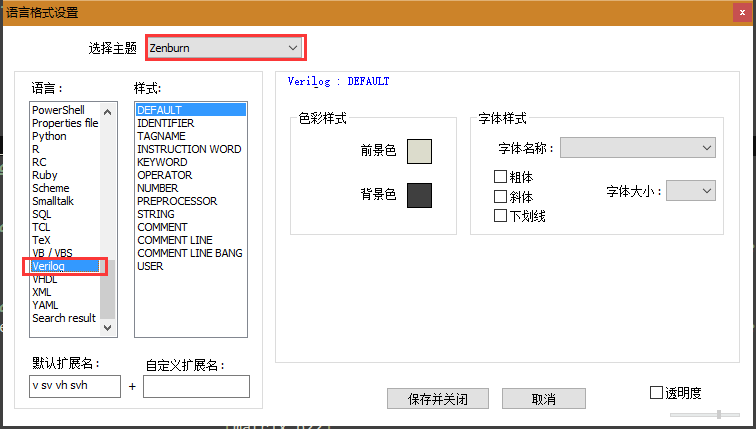

點擊設置——語言格式設置,可設置編輯器主題

這裏我選擇的是如圖所示的主題,我比較喜歡這個比較暗的顏色,

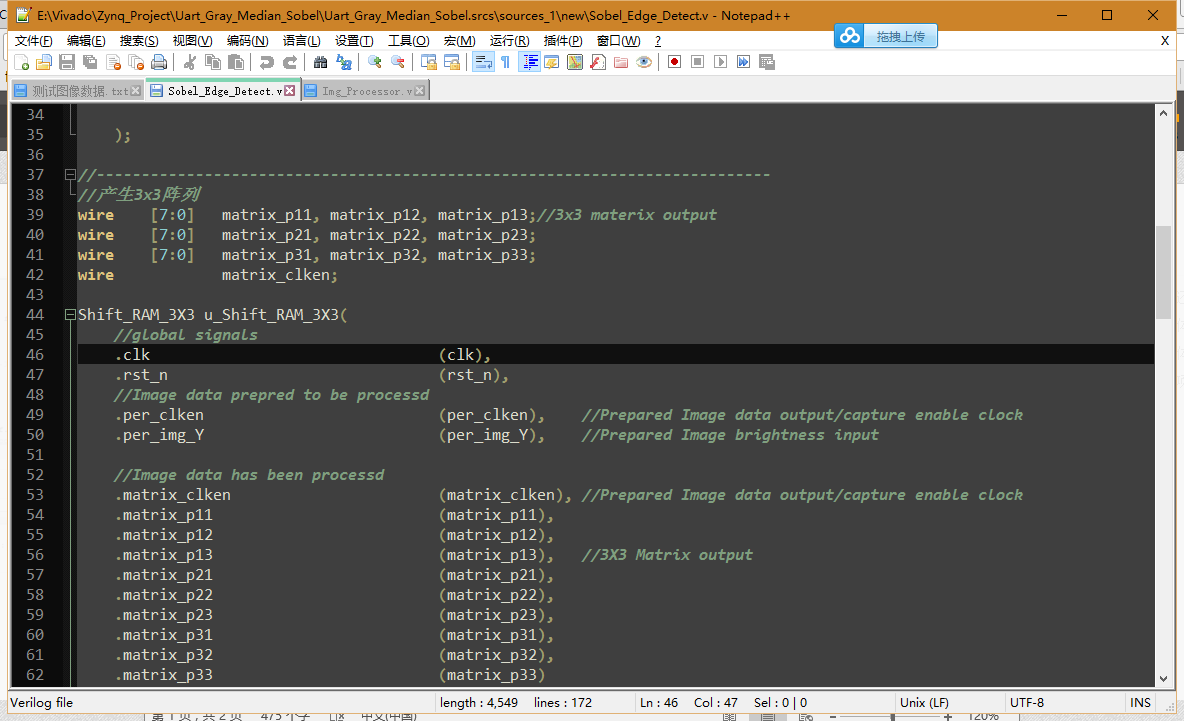

最終呈現的效果便如下圖所示,是不是看起來很舒服呢!

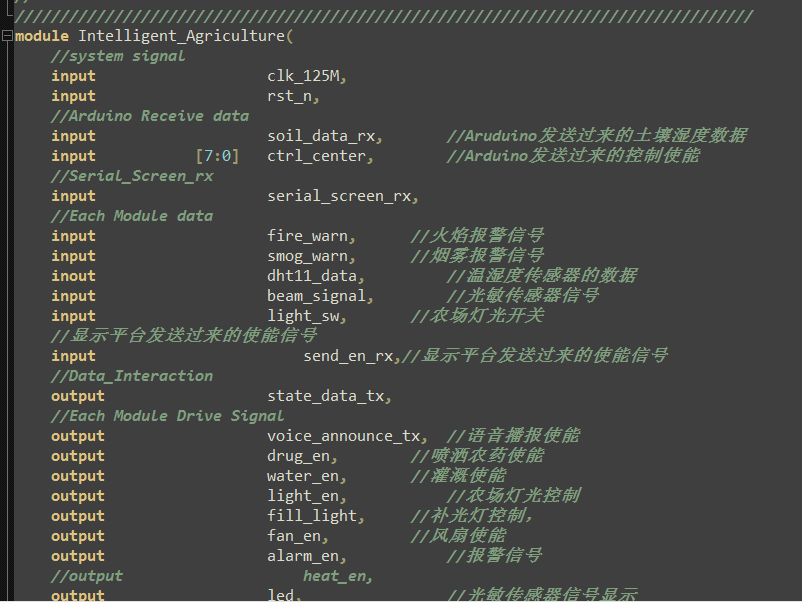

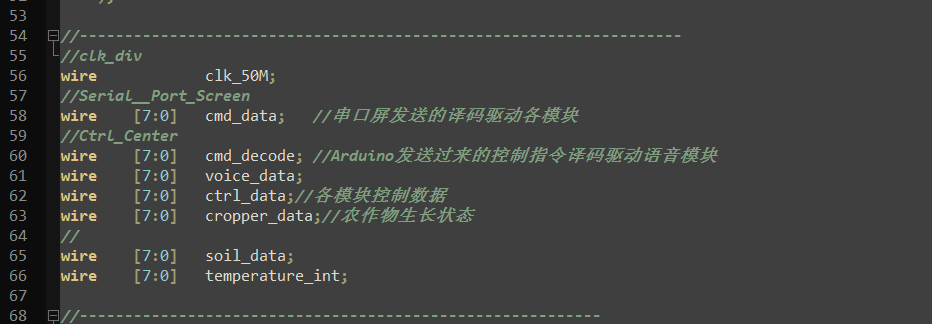

第二、代碼的端口命名、內部寄存器的命名。下圖是我們最近做的項目,可以看出在端口眾多的情況下,端口的命名有多重要,基本上從信號的命名就可以直接聯想到該信號的作用,同理,內部使用寄存器的命名也是如此。對於使用的系統時鐘命令最好是用clk+後綴,加上時鐘的頻率。這樣不僅自己看起來方便,別人看起來也方便。因為很多情況下,不同開發板的晶振是不一樣的,但是編寫者知道,其他人就未必知道了。我還真見過always@(posedge A or negedge B)這樣寫的人的,當然他也是剛開始學習了。

復位信號也直觀只要,我習慣上寫的而是rst+後綴,高電平有效還是低電平有效,rst_n(低電平有效negedge),rst_p(高電平有效posedge),我看過一些書上的復位信號命名的是clr,其實這兩種命名的方法根本沒有區別,一般情況下,我們復位都是將寄存器置數為0,也相當於清零,但也不排除,復位是給置數的情況,所以我習慣上使用rst_n來復位,及低電平復位。

其他的信號也就類似的,總結下來上就是,給信號起一目了然的名字,盡量使用縮寫,不要信號的名字太長,信號的名字和功能作用中間用下劃線隔開,要習慣性的給信號後面編寫註釋,給你編寫的代碼塊做註釋,給你編寫的模塊做註釋,請記住你的代碼不是給你一個人寫的。

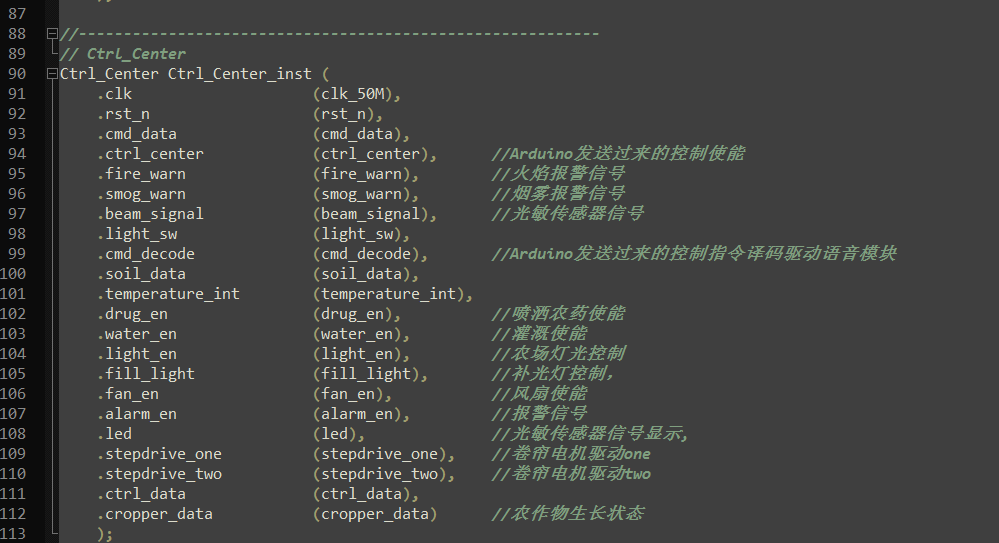

第三、代碼的工整。從上圖中可以看到,我在定義端口的時候是直接定義在module內部的,很多人的寫法是先在module內部定義一遍端口,然後再module下面再寫一遍input/output定義,其實這兩種方式都可以,那麽我為什麽選擇直接寫在module內部呢,,,因為我懶啊。在編寫代碼的時候多用空格和TAB,把定義的信號對齊,這樣寫出代碼是很漂亮的,每一段代碼之間應該用分隔線隔開,這樣整體看起來很清晰。

模塊端口的實例化也是,這樣的代碼自己看著漂亮,別人看著也舒服,而且從頂往下看都會很明了。

第四、在設計中多實用時序邏輯,尤其是直接需要輸出的端口。在我最近做的那個項目裏,我使用了一些組合邏輯來做控制,但是後來發現這樣會有一個弊端,每次系統上電的時候會有一段不穩定時間,在這段時間裏,我的那幾個控制模塊就無規則的在亂啟動,即使是在復位的情況下,這樣可能會引起一些麻煩造成系統的不穩定,如果采用是時序邏輯的話,就完全可以避免這個問題了,在系統上電的時候,復位低有效,等上電穩定後,將復位鍵變為高電平。

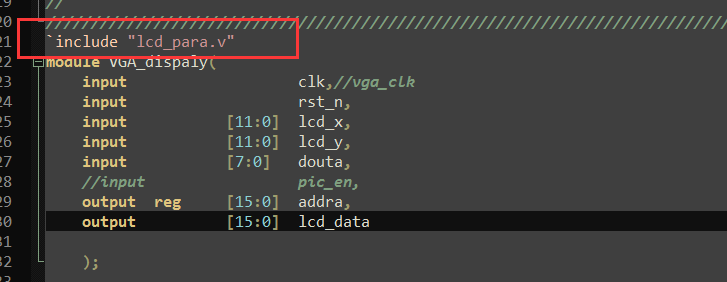

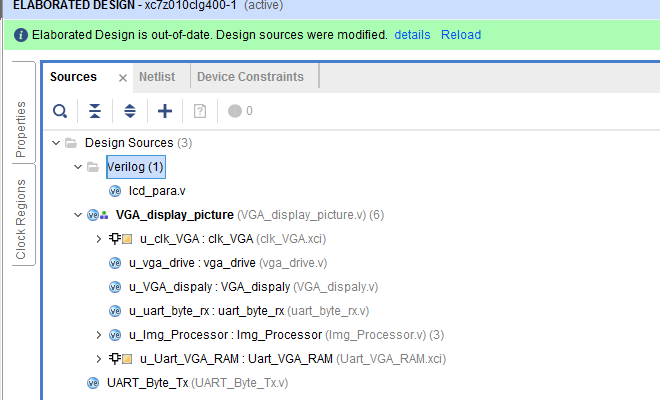

第五、如果一個工程裏,同一個宏定義需要在多個文件裏調用的話,建議使用調用文件。比如我在寫VGA驅動的時候,行掃描、場掃描和各種顏色的定義參數需要在多個模塊中使用,所以可在模塊內部直接寫如下圖所示部分,把”`define”定義放在一個單獨的文件裏面,”parameter”參數定義肯定必須是在模塊內部了,檢查重復定義。

第六、使用異步復位、同步置數的設計思想(可以了解一下異步復位、同步釋放),而且一個always塊裏,盡量值操作一個寄存器。一個模塊的代碼不要寫的太多,使用模塊化設計,而且在頂層文件裏盡量不了寫代碼,為了在檢查RTL圖的時候比較方便明了的看出各個模塊之間的連線圖。模塊內部不應該使用內部使用,同一個模塊內的時鐘應該是同一個時鐘驅動下的,如果要使用別的時鐘進行驅動的話,必須使用時鐘使能而不是時鐘觸發,保持所有always塊是同一個時鐘上升沿觸發,如果確實要使用內部時鐘 門控時鐘 或內部的復位信號 將它們放在頂層將這些信號的產生放在頂層的一個獨立模塊 這樣所有的子模塊分別使用單一的時鐘和復位信號。對於使用if——else if——else或case語句必須把所有的情況都寫上,避免生成鎖存器。最重要的第一點,寄存器類型的數據應該有復位,我不習慣使用initial語句進行初始化,一般都是用異步復位來為維持系統的穩定。還有平時寫代碼的時候盡量不要使用for循環,當然有些必要的時候也是可以用的。

第七、如果你遇到實在不好解決的設計,那麽這個時候,你就可以考慮一下狀態機了。

我能想到的目前就只有這麽多了,還有什麽是我沒有想到了和我做的可以留言告訴我。

轉載請註明出處:NingHeChuan(寧河川)

個人微信訂閱號:開源FPGANingHeChuan

如果你想及時收到個人撰寫的博文推送,可以掃描左邊二維碼(或者長按識別二維碼)關註個人微信訂閱號

知乎ID:NingHeChuan

微博ID:NingHeChuan

原文地址:http://www.cnblogs.com/ninghechuan/p/7859690.html

淺談Verilog HDL代碼編寫風格