# 2017-2018-1 20155319 《信息安全系統設計基礎》第十一周學習總結

2017-2018-1 20155319 《信息安全系統設計基礎》第十一周學習總結

教材學習內容總結

一、概述

虛擬存儲器的三個重要能力:

- 它將主存看成是一個存儲在磁盤上的地址空間的高速緩存,在主存中只保存活動區域,並根據需要在磁盤和主存之間來回傳送數據,通過這種方式,高效的使用了主存 - 它為每個進程提供了一致的地址空間,從而簡化了存儲器管理 - 它保護了每個進程的地址空間不被其他進程破壞虛擬存儲器是中心的、強大的、危險的。

二、地址

1.物理和虛擬尋址

(1)物理尋址

主存被組織成一個由M個連續的字節大小的單元組成的數組,依次類推的尋址方式稱為物理尋址。

(2)虛擬尋址

CPU生成一個虛擬地址(VA)來訪問主存,在被傳送到存儲器之前先轉換成適當的物理地址。地址翻譯通過CPU芯片上的存儲器管理單元完成。

2.地址空間

地址空間是一個非負整數地址的有序集合:{0,1,2,……}(1)線性地址空間

- 地址空間中的整數是連續的。(2)虛擬地址空間

- CPU從一個有 N=2^n 個地址的地址空間中生成虛擬地址,這個地址空間成為稱為虛擬地址空間。

(3)物理地址空間

- 與系統中的物理存儲器的M個字節相對應。

(4)地址空間的大小

- 由表示最大地址所需要的位數來描述。

- N=2^n:n位地址空間主存中的每個字節都有一個選自虛擬地址空間的虛擬地址和一個選自物理地址空間的物理地址。三、虛擬存儲器

1.作為緩存的工具

虛擬存儲器——虛擬頁VP,每個虛擬頁大小為P=2^平字節 物理存儲器——物理頁PP,也叫頁幀,大小也為P字節。

任意時刻,虛擬頁面的集合都被分為三個不相交的子集:

- 未分配的:VM系統還沒分配/創建的頁,不占用任何磁盤空間。

- 緩存的:當前緩存在物理存儲器中的已分配頁

- 未緩存的:沒有緩存在物理存儲器中的已分配頁

(1)DRAM緩存的組織結構

- 不命中處罰很大

- 是全相聯的——任何虛擬頁都可以放在任何的物理頁中。

- 替換算法精密

- 總是使用寫回而不是直寫。

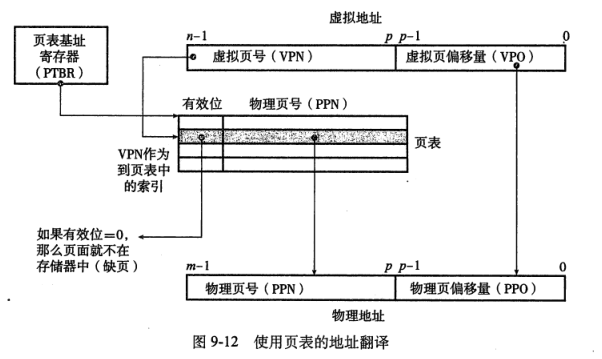

(2)頁表

頁表:是一個數據結構,存放在物理存儲器中,將虛擬頁映射到物理頁,就是一個頁表條目的數組。頁表就是一個頁表條目PTE的數組。

PTE:由一個有效位和一個n位地址字段組成的,表明了該虛擬頁是否被緩存在DRAM中。頁表的組成:

有效位+n位地址字段- 如果設置了有效位:地址字段表示DRAM中相應的物理頁的起始位置,這個物理頁中緩存了該虛擬頁。

- 如果沒有設置有效位:

- 空地址:表示該虛擬頁未被分配

- 不是空地址:這個地址指向該虛擬頁在磁盤上的起始位置。

(3)缺頁

缺頁:就是指DRAM緩存不命中。

缺頁異常:會調用內核中的缺頁異常處理程序,選擇一個犧牲頁。

頁:虛擬存儲器的習慣說法,就是塊

交換=頁面調度:磁盤和存儲器之間傳送頁的活動

按需頁面調度:直到發生不命中時才換入頁面的策略,所有現代系統都使用這個。

(4)虛擬存儲器中的局部性

局部性原則保證了在任意時刻,程序將往往在一個較小的活動頁面集合上工作,這個集合叫做工作集/常駐集。所以只要程序有良好的時間局部性,虛擬存儲器系統就能工作的相當好。

顛簸:工作集大小超出了物理存儲器的大小。

2.作為存儲器管理的工具

操作系統為每個進程提供了一個獨立的頁表,也就是一個獨立的虛擬地址空間。- 多個虛擬頁面可以映射到同一個共享物理頁面上。

存儲器映射:將一組連續的虛擬頁映射到任意一個文件中的任意位置的表示法。

按需頁面調度和獨立的虛擬地址空間的結合簡化了鏈接和加載、代碼和數據共享,以及應用程序的存儲器分配。

- 簡化鏈接:獨立的地址空間允許每個進程的存儲器映像使用相同的基本格式,而不管代碼和數據實際存放在物理存儲器的何處。 - 簡化加載:虛擬存儲器使得容易想存儲器中加載可執行文件和共享文件對象。 - 簡化共享:獨立地址空間為操作系統提供了一個管理用戶進程和操作系統自身之間共享的一致機制。 - 簡化存儲器分配:虛擬存儲器為向用戶進程提供一個簡單的分配額外存儲器的機制。

3.作為存儲器保護的工具

通過在PTE上添加一些額外的許可來控制對一個虛擬頁面的內容訪問。PTE的三個許可位:

SUP:表示進程是否必須運行在內核模式下才能訪問該頁

READ:讀權限

WRITE:寫權限

4.地址翻譯

(1)地址翻譯

地址翻譯就是一個N元素的虛擬地址空間VAS中的元素和一個M元素的物理地址空間PAS中元素之間的映射。

MAP: VAS → PAS ∪ ?這裏

MAP = A‘ ,如果虛擬地址A處的數據在PAS的物理地址A‘處 MAP = ? ,如果虛擬地址A處的數據不在物理存儲器中如何用頁表實現這種映射

當頁面命中時,CPU硬件執行步驟

- 處理器生成虛擬地址,傳給MMU

- MMU生成PTE地址,並從高速緩存/主存請求得到他

- 高速緩存/主存向MMU返回PTE

- MMU構造物理地址,並把它傳給高速緩存/主存

- 高速緩存/主存返回所請求的數據給處理器。

處理缺頁時,CPU硬件執行步驟

- 處理器生成虛擬地址,傳給MMU

- MMU生成PTE地址,並從高速緩存/主存請求得到他

- 高速緩存/主存向MMU返回PTE

- PTE中有效位為0,觸發缺頁異常

- 確定犧牲頁

- 調入新頁面,更新PTE

- 返回原來的進程,再次執行導致缺頁的指令,會命中

(2)結合高速緩存和虛擬存儲器

- 在既使用SRAM高速緩存又使用虛擬存儲器的系統中,大多數系統選擇物理尋址。

- 兩者結合的主要思路是地址翻譯發生在高速緩存之前。

- 頁表目錄可以緩存,就像其他的數據字一樣。

(3)利用TLB加速地址翻譯

TLB:翻譯後備緩沖器,是一個小的、虛擬存儲的緩存,其中每一行都保存著一個由單個PTE組成的塊- 步驟

- CPU產生一個虛擬地址

- MMU從TLB中取出相應的PTE

- MMU將這個虛擬地址翻譯成一個物理地址,並且將它發送到高速緩存/主存

- 高速緩存/主存將所請求的數據字返回給CPU

(4)多級頁表

多級頁表——采用層次結構,用來壓縮頁表。以兩層頁表層次結構為例,好處是:

- 如果一級頁表中的一個PTE是空的,那麽相應的二級頁表就根本不會存在

只有一級頁表才需要總是在主存中,虛擬存儲器系統可以在需要時創建、頁面調入或調出二級頁表,只有最經常使用的二級頁表才緩存在主存中。

代碼調試中的問題和解決過程

暫無。實驗中寫出

代碼托管

(statistics.sh腳本的運行結果截圖)

上周考試錯題總結

已用博客補充。

| 代碼行數(新增/累積) | 博客量(新增/累積) | 學習時間(新增/累積) | 重要成長 | |

|---|---|---|---|---|

| 目標 | 5000行 | 30篇 | 400小時 | |

| 第一周 | 200/200 | 2/2 | 20/20 | |

| 第二周 | 300/500 | 2/4 | 18/38 | |

| 第三周 | 500/1000 | 3/7 | 22/60 | |

| 第四周 | 300/1300 | 2/9 | 30/90 |

嘗試一下記錄「計劃學習時間」和「實際學習時間」,到期末看看能不能改進自己的計劃能力。這個工作學習中很重要,也很有用。

耗時估計的公式

:Y=X+X/N ,Y=X-X/N,訓練次數多了,X、Y就接近了。

參考:軟件工程軟件的估計為什麽這麽難,軟件工程 估計方法

計劃學習時間:11小時

實際學習時間:8小時

# 2017-2018-1 20155319 《信息安全系統設計基礎》第十一周學習總結