阻抗匹配處理方式

關於阻抗匹配的處理方式

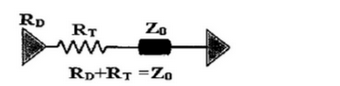

串聯端接方式

靠近輸出端的位置串聯一個電阻,要達到匹配效果,串聯電阻和驅動端輸出阻抗的總和應等於傳輸線的特征阻抗Z0。

在通常的數字信號系統中,器件的輸出阻抗通常是十幾歐姆到二十幾歐姆,傳輸線的阻抗通常會控制在50歐姆,所以始端匹配電阻常見為33歐姆電阻。

當然要達到好的匹配效果,驅動端輸出到串聯電阻這一段的傳輸路徑最好較短,短到可以忽略這一段傳輸線的影響。

串聯電阻優缺點如下:

優點

1、只需要一個電阻;

2、沒有多余的直流功耗;

3、消除驅動端的二次反射;

4、不受接收端負載變化的影響;

缺點

1、接收端的一次發射依然存在;

2、信號邊沿會有一些變化;

3、電阻要靠近驅動端放置,不適合雙向 傳輸信號;

4、在線上傳輸的電壓是驅動電壓的一半,不適合菊花鏈的多型負載結構。

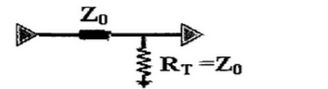

並聯端接方式

並聯端接又叫終端匹配,要達到阻抗匹配的要求,端接的電阻應該和傳輸線的特征阻抗Z0相等。

在通常的數字信號傳輸系統裏,接收端的阻抗範圍為幾兆到十幾兆,終端匹配電阻如果和傳輸線的特征阻抗相等,其和接收端阻抗並聯後的阻抗大致還是在傳輸線的特征阻抗左右,那麽終端的反射系數為0。不會產生反射,消除的是終端的一次反射。

並聯端接優缺點

優點

1、適用於多個負載

2、只需要一個電阻並且阻值容易選取

缺點

1、增加了直流功耗

2、並聯端接可以上拉到電源或者下拉到地,是的低電平升高或者高電平降低,減小噪聲容限。

AC並聯端接

並聯端接為消除直流功耗,可以采用如下所示的AC並聯端接(AC終端匹配)。要達到匹配要求,端接的電阻應該和傳輸線的特征阻抗Z0相等。

優缺點描述如下:

優點

1、適用於多個負載

2、無直流功耗增加

缺點

1、需要兩個器件

2、增加了終端的容性負載,增加了RC電路造成的延時

3、對周期性的信號有效(如時鐘),不適合於非周期信號(如數據)

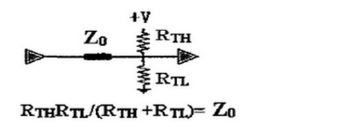

戴維南端接

戴維南端接同終端匹配,如圖,要達到匹配要求,終端的電阻並聯值要和傳輸線的特征阻抗Z0相等。

優缺點描述:

優點

1、適用於多個負載

2、很適用於SSTL/HSTL電平上拉或下拉輸出阻抗很好平衡的情況。

缺點

1、直流功耗增加

2、需要兩個器件

3、端接電阻上拉到電源或下拉到地,會使得低電平升高或高電平降低

4、電阻值較難選擇,電阻值取值小會使低電平升高,高電平降低更加惡劣;電阻值取大有可能造成不能完全匹配,使反射增大,可以通過仿真來確定。

版權所有權歸卿萃科技 杭州FPGA事業部,轉載請註明出處

作者:杭州卿萃科技ALIFPGA

原文地址:杭州卿萃科技FPGA極客空間 微信公眾號

掃描二維碼關註杭州卿萃科技FPGA極客空間

阻抗匹配處理方式