U8g2庫I2C總線再次突破性調試成功

這次采用U8X8的方式,不再采用u8g2,因為後者一直報內存問題。所以采用了不占內存的u8x8模式

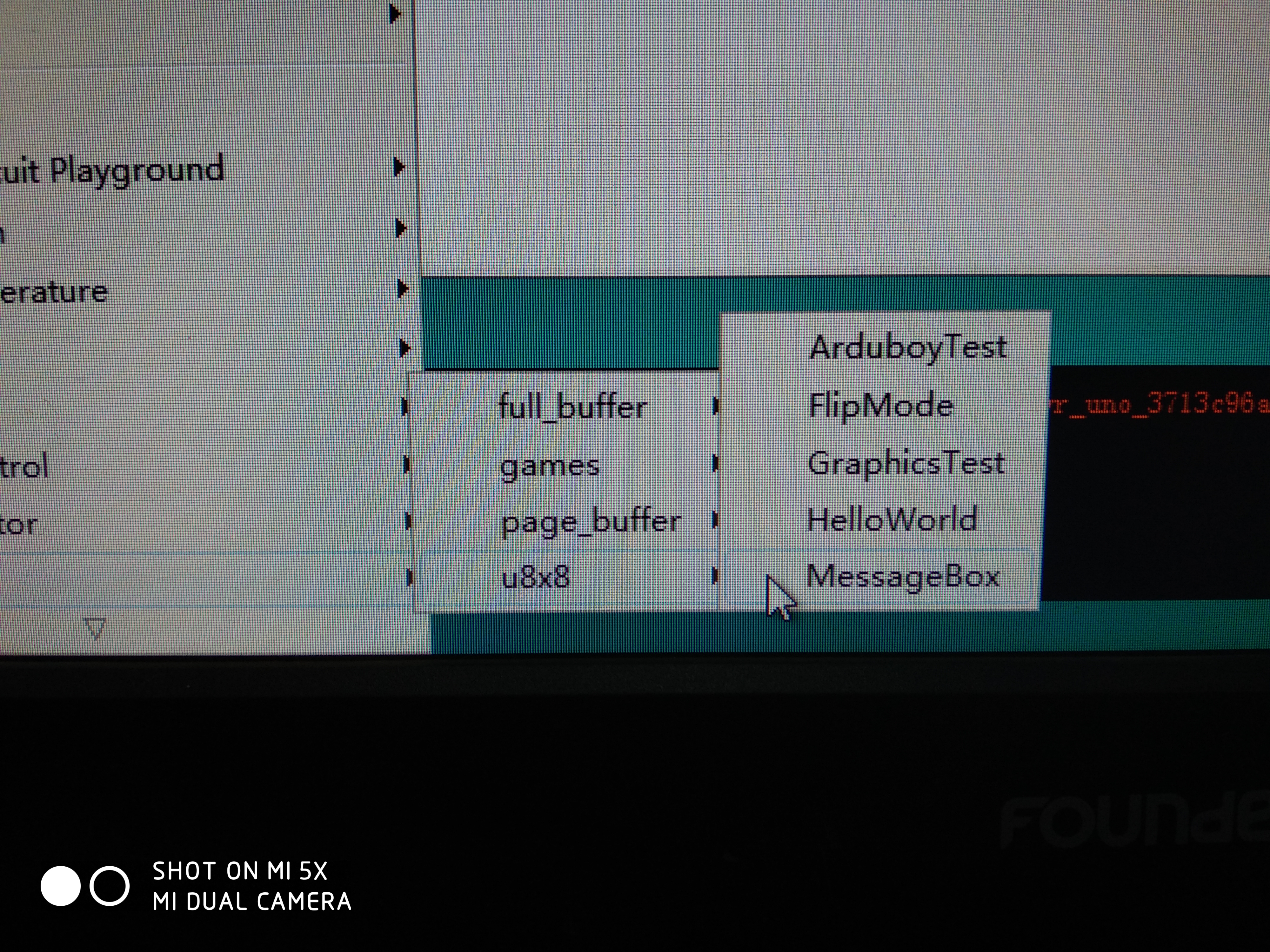

同時u8g2庫文件的示例代碼也是很牛逼的,

裏面還有message box 非常的可愛運行效果也非常棒!

代碼如下

再也沒有出現之前的動不動就報內存不足的問題。

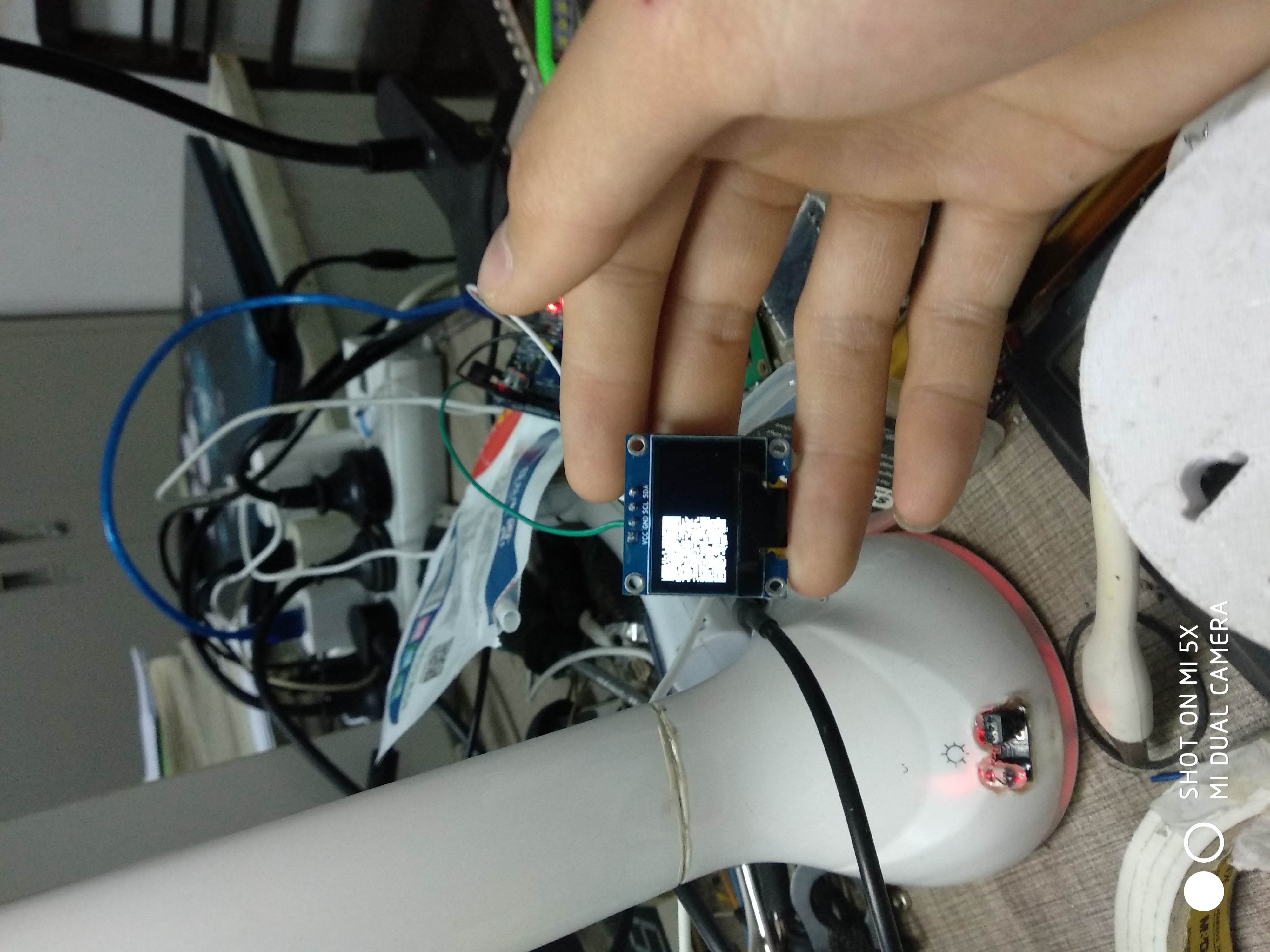

同時還可以自己生成位圖進行顯示,比如二維碼,不過,識別起來很吃力

U8g2庫I2C總線再次突破性調試成功

相關推薦

U8g2庫I2C總線再次突破性調試成功

bsp 示例代碼 logs 分享圖片 二維 圖片 images pos 效果 這次采用U8X8的方式,不再采用u8g2,因為後者一直報內存問題。所以采用了不占內存的u8x8模式 同時u8g2庫文件的示例代碼也是很牛逼的, 裏面還有message box 非常的可愛運行效果

51單片機基於I2C總線的秒表模擬應用

ons 解決 char s oid 保存數據 con 標誌位 周期 顯示 ———————————————————————————————————————————— 參考地址: http://blog.csdn.net/junyeer/article/details/46

I2C總線之(三)---以C語言理解IIC

接收 朋友 blog 初始化 停止 數據傳輸 date reg alt I2C總線之(三)---以C語言理解IIC為了加深對I2C總線的理解,用C語言模擬IIC總線,邊看源代碼邊讀波形:如下圖所示的寫操作的時序圖: 讀時序的理解同理。對於時序不理解的朋友請參考“I2C總線之

EEPROM讀寫學習筆記與I2C總線(二)

一點 後來 並不是 完數 cal 效應 計算 spi 速度慢 無論任何電子產品都會涉及到數據的產生與數據的保存,這個數據可能並不是用來長久保存,只是在運行程序才會用到,有些數據體量較大對於獲取時效性並不太強,各種各樣的數據也就有不同的存儲載體,這次在EEPR

【轉】I2C總線協議

和數 編號 智能 file bit adc 共存 忽略 targe I2C總線(Inter Integrated-Circuit)是由PHILIPS公司在上世紀80年代發明的一種電路板級串行總線標準,通過兩根信號線——時鐘線SCL和數據線SDA——即可完成主從機的單工通信。

SylixOS 基於STM32平臺的GPIO模仿I2C總線的驅動開發流程

STM32 GPIO模仿I2C 1.概述 本文檔以STM32F767平臺為例,詳細介紹SylixOS上GPIO模仿I2C總線的驅動開發流程。 2.初始化 GPIO模仿的I2C總線的初始化,實際上是I2C總線的SDA和SCL的GPIO管腳初始化。初始化流程如圖 2.1所示。 圖 2.1 I2C初始化流程

ESP32學習筆記(四)之I2C總線

oid 操作系統 parameter ica basis condition 技術分享 col rto 上一篇帖子我們了解了一下ESP32運行多任務的操作以及現象,其實也就是一個實時操作系統。那麽,這篇帖子我們就結合“LM75a”溫度傳感器來學習一下ESP32的IIC總線吧

I2C總線

div reg 函數 style i2c splay lB 定義變量 按鍵 1. 定義方法 a.定義起始信號 b.定義終止信號 c.定義單片機寫入函數 d.定義單片機讀出函數 e.寫入到指定元器件 f.從指定元器件讀出 g.寫一個頭文件作為中轉

關於具有I2C總線的TEA6320的使用

關閉 發送數據 alt 延時 初始化 spa 查找 地址 數據位 現在先了解一下TEA6320,TEA6320是一個I2C總線控制音響應用的立體聲放大器,,它的I2C協議和音量控制如下: 它的主要代碼: void delay1ms(unsig

I2C 總線原理與架構

alt har probe 調用 module 核心 enter 寄存器 target 一、I2C總線原理 I2C是一種常用的串行總線,由串行數據線SDA 和串行時鐘線SCL組成。I2C是一種多主機控制總線,它和USB總線不同,USB是基於master

一個判斷I2C總線通信異常原因的方法

png com 原因 處理器 用處 定位 處理 一個 info 此問題由某客戶提出,應用處理器 AP與 MCU進行 I2C通信,通信會經常發生異常,需要定位原因. 首先需要定位的是因為哪個器件發的波形不正確導致通信異常,所以我們在 I2C 線路上增加了以下處理,增加 2

i2c總線註意事項和在linux下使用實戰

linux下 訪問 參考 協議 new com data transfer driver i2c總線註意事項和在linux下使用實戰 仔細閱讀上圖中的下部分文字。 註意你的i2c_msg發送方式,決定了是否有pause。 註意圖中,什麽叫sr。 註意圖上說的什麽樣

調試成功的簡單異步FIFO--verilog實現+testbench

opened dom 成功 ini num 註意 wire sign 類型 最近在寫一個異步FIFO的時候,從網上找了許多資料,文章都寫的相當不錯,只是附在後面的代碼都多多少少有些小錯誤。 於是自己寫了一個調試成功的代碼,放上來供大家參考。 非原創 原理參考下面: 原文 h

I2C和SPI總線對比

clas 結束 相對 比較 scl 只有一個 shee 鎖定 因此 1 iic總線不是全雙工,2根線SCL SDA。spi總線實現全雙工,4根線SCK CS MOSI MISO 2 iic總線是多主機總線,通過SDA上的地址信息來鎖定從設備。spi總線只有一個主設備,主設

利刃 MVVMLight 8:DispatchHelper在多線程和調度中的使用

isf ref ping 輔助 比例 修改 brush ner aac 在應用程序中,線程可以被看做是應用程序的一個較小的執行單位。每個應用程序都至少擁有一個線程,我們稱為主線程,這是在啟動時調用應用程序的主方法時由操作系統分配啟動的線程。 當調用和操

exit庫函數和_exit系統調用對標準輸出的影響

eno 標準 代碼 for sizeof pan type lob int #include <stdio.h> #include <unistd.h> #include <sys/types.h> #include <stdli

linux設備驅動之platform平臺總線工作原理(三)

linux設備和驅動設備為數據,驅動為加工著1、以led-s3c24xx.c為例來分析platform設備和驅動的註冊過程其中關於led的驅動數據結構為:static struct platform_driver s3c24xx_led_driver = { .probe = s3c24xx_led_pr

【CAN總線】概述

容錯能力 概述 時間 反射 bench 並不會 color 溫度 之前 前言:公司做的是汽車電子,所以產品都是用CAN總線。然而作為硬件工程師我不畫板,作為軟件工程師我不編程,作為FPGA工程師我也並不會用IP核。之前做過CAN總線的物理層測試,最近被派遣去用FPGA實現C

【CAN總線】CAN代碼相關問題和註釋(1) ------------4.6更新

配置 註釋 一次 保護 tex 擴展 控制 xca 比較 前言: 在看如何用FPGA實現can_controller ,本來想把代碼上傳上來的,結果沒成功。如果有意向研究的,可以自己去下載 pudn就有。can tb有點問題,我也只是在剛剛研究,如果有意向可以和我交流

【CAN總線】CAN代碼相關問題和註釋(2)

讀取數據 文件 觸發 == mod tpc term urn i++ 本節內容提要: 根據SJA1000的初始化程序,了解CAN的初始化過程以及對象。本來是想整理的,後來發現一整篇都很有用就直接轉載了。 不過我在想,如果是直接用verilog實現can 是否有另外的方法來對