【轉】SPI總線協議

SPI總線協議

概述

SPI(Serial Peripheral Interface)總線是主要應用於嵌入式系統內部通信的串行同步傳輸總線協議。通常為四線制的SPI總線支持全雙工通信。SPI最初由Motorola在2000年提出,Motorola所定義的SPI標準為業界廣泛引用,但不同半導體公司的實施細節可能有所不同,這些區別體現在寄存器設置、信號定義、數據格式等。業界沒有統一的SPI標準,具體應用需要參考特定器件手冊。

SPI協議特點包括主從模式、全雙工通信、片選功能、模式錯誤標識及CPU中斷、緩沖數據寄存器和可配置時鐘相位極性等。SPI允許數據一位一位的傳送,甚至允許暫停,因為SCK時鐘線由主控設備控制,當沒有時鐘跳變時,從設備不采集或傳送數據。也就是說,主設備通過對SCK時鐘線的控制可以完成對通訊的控制。

應用

SPI以其簡單高效應用於絕大多數SoC系統上,這些SoC通常同時支持作為主模式或從模式(二選一)。

FPGAs和其它專用芯片也廣泛使用SPI傳輸數據。比如:

- 傳感器:溫度、壓力傳感器等

- 控制設備:音頻編解碼器等

- 通信設備:USB、以太網設備等

- 存儲器:Flash、EEPROM等

- RTC時鐘

- LCD設備

- MMC和SD卡

在高性能系統中,FPGAs通常使用SPI連接主從設備,比如連接外部傳感器,和應用SPI加載配置。相比於JTAG,SPI定位用於高速配置(初始化)板上設備;而JTAG的初衷是為控制設備以相對低的準確度掃描和檢測板上IO,在嚴格要求的場合,JTAG協議支持改變時鐘占空比以滿足建立和保持時間的要求。因此,JTAG並不定位於高速數據傳輸的場合。

優點和缺點

優點

- 支持全雙工通信

- Push-Pull驅動性能相比Open Drain信號完整性更好,支持高速應用(100MHz以上)

- 協議支持字長不限於8bits,可根據應用特點靈活選擇消息字長

- 硬件連接簡單

- 只需要四根信號線(部分應用可以縮減到三根)

- 相比I2C和SMbus節省上拉電阻

- 相比I2C和SMbus不需要仲裁機制

- 從設備使用主設備時鐘,節約時鐘要求

- 從設備無需地址尋址

- 無需收發器

缺點

- 相比I2C兩根線,SPI四根線更多

- 沒有尋址機制,只能靠設備片選(chip select)選擇不同從設備

- 沒有數據流控制(但主設備可以通過延緩時鐘邊緣降低傳輸速度)

- 沒有從設備接收數據ACK,主設備對於發送成功與否不得而知

- 典型應用只支持單主控

- 沒有定義數據校驗機制

- 沒有統一的國際組織維護,變種多不利於不同廠商設備的互操作性(interoperability)

- 相比於RS232、RS422、RS485和CAN,SPI傳輸距離短

- 不支持熱插拔

- 中斷操作只能通過額外的信號線,或類似USB 1.1 and 2.0的Periodic Polling實現

內部框圖

本文主要參考三家公司SPI協議手冊,其原理大同小異:

- SPI Block Guide V04.01 -Motorola

- KeyStone Architecture Serial Peripheral Interface (SPI) User Guide -Texas Instruments

- TN0897: ST SPI protocol -STMicroelectronics

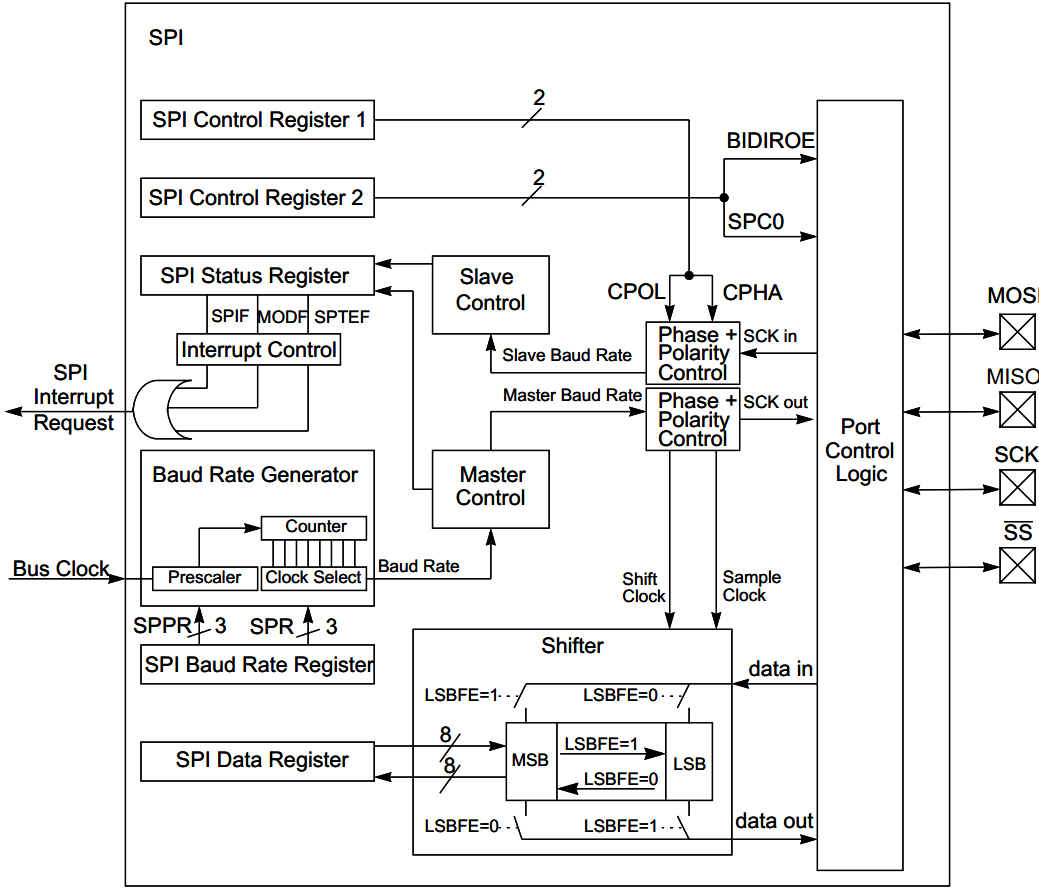

圖1表示Motorola定義SPI模塊的內部框圖,其主要構成包括狀態/控制/數據寄存器(Status,Control and Data Registers)、移位寄存器(Shifter Logic)、波特率發生器(Baud Rate Generator)、主從控制邏輯(Master/Slave Control Logic)和端口控制邏輯(Port Control Logic)。

圖1. SPI模塊框圖(Motorola)

硬件基礎

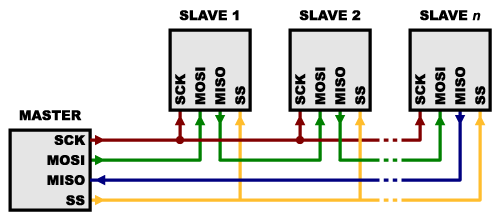

SPI總線定義兩個及以上設備間的數據傳輸,提供時鐘的設備為主設備(Master),接收時鐘的設備為從設備(Slave)。

信號定義

SPI協議定義四根信號線,分別為:

- SCK : Serial Clock 串行時鐘

- MOSI : Master Output, Slave Input 主發從收信號

- MISO : Master Input, Slave Output 主收從發信號

- SS : Slave Select 片選信號

其中MISO方向為從設備到主設備,其余三個信號均為主設備到從設備。

說明:

- 對於主設備,如果設置SS作為從設備的片選信號(最常用的場合),則它就不能用於多主設備應用的模式錯誤檢測(參考SSOE和MODFEN寄存器設置,表1)

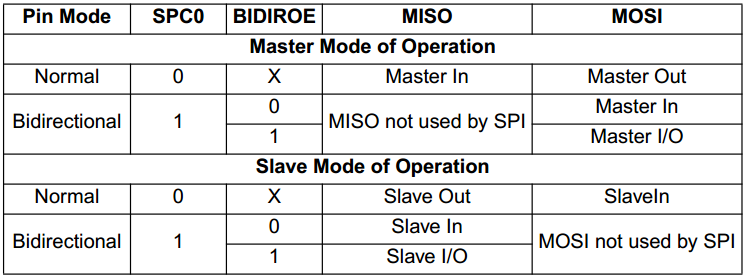

- SPI單個數據管腳支持雙向模式。在雙向模式下,主設備的MOSI,從設備的MISO作為雙向IO(參考SPC0和BIDIROE寄存器設置,表2)

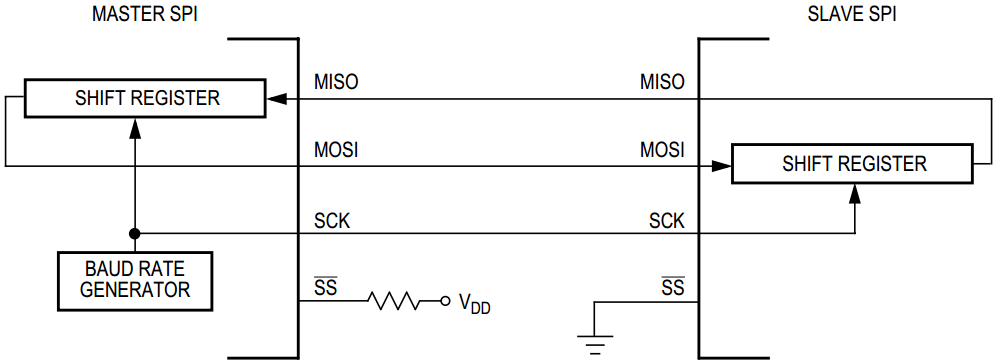

電路連接

圖2表示基本的SPI設備連接示意圖。片選信號SS通常低電平有效。SPI數據傳輸原理是基於主從設備內部移位寄存器的數據交換。在主設備SCK的控制下,待傳數據由各自設備的數據寄存器(Data Register)傳輸到移位寄存器(Shift Register),再通過MOSI和MISO信號線完成主從設備間的數據交換。

圖2. SPI主從模式傳輸示意圖(電路)

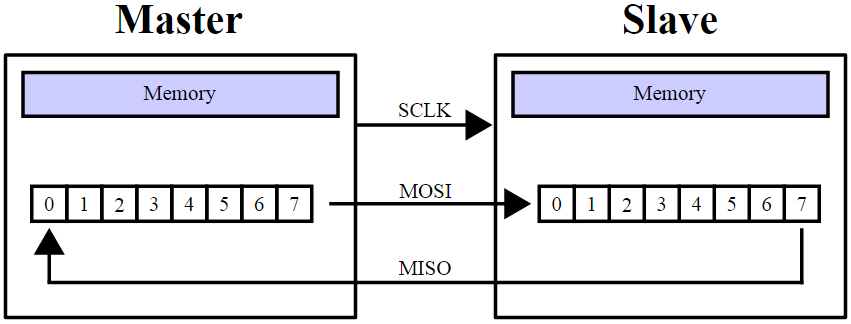

主從設備間數據交換邏輯示意圖如下圖3所示:

圖3. SPI主從模式傳輸示意圖(邏輯)

硬件拓撲

單個主設備和單個從設備的SPI連接比較簡單,以上圖2和圖3表示的就是這種拓撲結構。

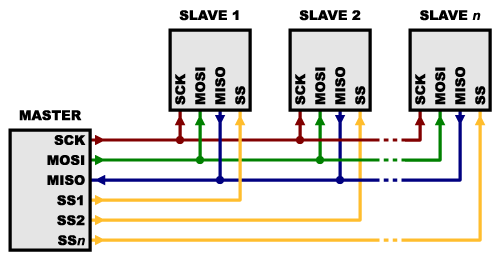

通過多個片選信號(SS)或菊花鏈方式(Daisy Chain Configuration),單個主設備可以同時控制多個不同從設備。

- 片選方式

如圖4示,每個從設備都需要單獨的片選信號,主設備每次只能選擇其中一個從設備進行通信。因為所有從設備的SCK、MOSI、MISO都是連在一起的,未被選中從設備的MISO要表現為高阻狀態(Hi-Z)以避免數據傳輸錯誤。由於每個設備都需要單獨的片選信號,如果需要的片選信號過多,可以使用譯碼器產生所有的片選信號。

圖4. 主設備以片選方式控制多個從設備

- 菊花鏈方式

如圖5示,數據信號經過主從設備所有的移位寄存器構成閉環。數據通過主設備發送(綠色線)經過從設備返回(藍色線)到主設備。在這種方式下,片選和時鐘同時接到所有從設備,通常用於移位寄存器和LED驅動器。註意,菊花鏈方式的主設備需要發送足夠長的數據以確保數據送達到所有從設備。切記主設備所發送的第一個數據需(移位)到達菊花鏈中最後一個從設備。

菊花鏈式連接常用於僅需主設備發送數據而不需要接收返回數據的場合,如LED驅動器。在這種應用下,主設備MISO可以不連。如果需要接收從設備的返回數據,則需要連接主設備的MISO形成閉環。同樣地,切記要發送足夠多的接收指令以確保數據(移位)送達主設備。

圖5. 主設備以菊花鏈方式控制多個從設備

電源管理

Motorola在SPI Block Guide中定義以下三種SPI電源模式:

- 運行模式 Run Mode

- 等待模式 Wait Mode

- 停止模式 Stop Mode

在運行模式下,SPI工作處於正常工作狀態。通過修改SPICR1寄存器的SPE位更改此模式:

0: 禁用SPI模塊(進入低功耗狀態)

1: 使能SPI模塊

在等待模式下,修改SPICR2寄存器的SPISWAI位:

0: 運行模式

1: 低功耗模式 SPI時鐘停止運作

對於主設備,進入等待模式意味終止SPI總線上所有數據傳輸,唯有將SPISWAI 重新置為0方可恢復通信;對於從設備,進入等待模式後仍將與主設備保持同步,從設備數據的接收和發送還是正常的。

在停止模式下,對於主設備,進入停止模式意味著所有總線上通信的終止;對於從設備,進入停止模式後數據的發送和接收還是正常的,仍然與主設備保持同步狀態。

TI在SPI User Guide定義兩種低功耗狀態:

- 全局低功耗模式 Global Low-Power Mode

- 局部低功耗模式 Local Low-Power Mode

全局低功耗模式受系統控制,此模式下SPI時鐘停止,處於完全不作為狀態。

通過寫SPI全局寄存器(SPIGCR1)可以是SPI模塊進入局部低功耗模式。此模式下,所有寄存器可以正常訪問,但SPI的狀態機處於停擺狀態,數據收發可能異常。軟件設置時需要註意不要在收發數據時讓SPI進入低功耗模式。

寄存器說明

Motorola定義的SPI寄存器包括:

- SPI Control Register 1 (SPICR1)

- SPI Control Register 2 (SPICR2)

- SPI Baud Rate Register (SPIBR)

- SPI Status Register (SPISR)

- SPI Data Register (SPIDR)

其中除了狀態寄存器SPISR為只讀(Read-only),其它寄存器都是可讀寫的。通過往寄存器中寫入不同的值,設置SPI模塊的不同屬性。

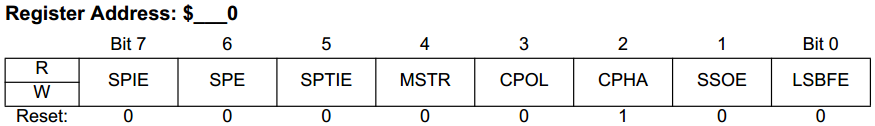

1. 控制寄存器1 SPICR1

圖6. 控制寄存器1 SPICR1

SPIE — SPI Interrupt Enable Bit

1 = SPI interrupts enabled

0 = SPI interrupts disabled

SPE — SPI System Enable Bit

1 = SPI enabled, port pins are dedicated to SPI functions

0 = SPI disabled (lower power consumption)

SPTIE — SPI Transmit Interrupt Enable

1 = SPTEF interrupt enabled

0 = SPTEF interrupt disabled

MSTR — SPI Master/Slave Mode Select Bit

1 = SPI is in Master mode

0 = SPI is in Slave mode

CPOL — SPI Clock Polarity Bit

1 = Active-low clocks selected. In idle state SCK is high

0 = Active-high clocks selected. In idle state SCK is low

CPHA — SPI Clock Phase Bit

1 = Sampling of data occurs at even edges (2,4,6,...,16) of the SCK clock

0 = Sampling of data occurs at odd edges (1,3,5,...,15) of the SCK clock

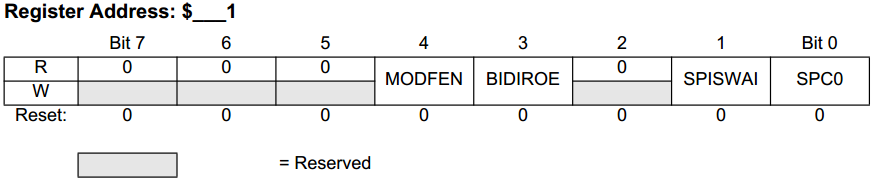

SSOE — Slave Select Output Enable

SSOE 用於主設備設置SS管腳功能,它和MODFEN組合決定主設備SS管腳功能。如表1所示其功能組合:

表1. SS輸入/輸出選擇

LSBFE — LSB-First Enable

1 = Data is transferred least significant bit first

0 = Data is transferred most significant bit first

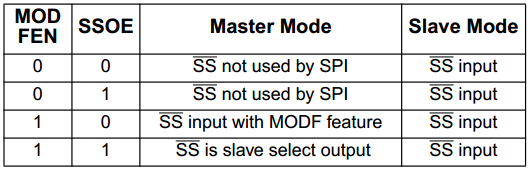

2. 控制寄存器2 SPICR2

圖7. 控制寄存器1 SPICR2

圖7. 控制寄存器1 SPICR2

MODFEN — Mode Fault Enable Bit

1 = SS port pin with MODF feature

0 = SS port pin is not used by the SPI

BIDIROE — Output enable in the Bidirectional mode of operation

控制雙向模式(Bidirectional Mode)下主設備的MOSI和從設備MISO的輸出緩沖器

1 = Output buffer enabled

0 = Output buffer disabled

SPISWAI — SPI Stop in Wait Mode Bit

1 = Stop SPI clock generation when in wait mode

0 = SPI clock operates normally in wait mode

SPC0 — Serial Pin Control Bit 0

控制(單個)數據管腳是否配置為雙向模式,與BIDIROE組合控制(單個)數據管腳同時支持收發功能(如下表2)

表2. MOSI/MISO雙向管腳配置

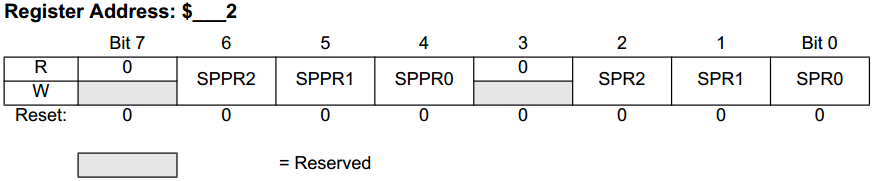

3. 波特率寄存器 SPIBR

圖8. 波特率寄存器 SPIBR

圖8. 波特率寄存器 SPIBR

SPPR2–SPPR0 — SPI Baud Rate Preselection Bits

SPR2–SPR0 — SPI Baud Rate Selection Bits

以上五個寄存器通過下面公式決定波特率除數因子(BaudRateDivisor),進而決定SCK時鐘頻率。

除數因子:(通過五個參數計算出來的除數因子不僅包括2^N,還包括4/6/10等總計64個組合)

![]()

計算波特率:

![]()

舉例,SPPR[2:0]設為101,SPR[2:0]設為000,計算得除數因子(5+1) * (2^1) = 12。如果系統時鐘速率為25MHz,則SCK時鐘速率 = 25MHz/12 = 2.0833MHz.

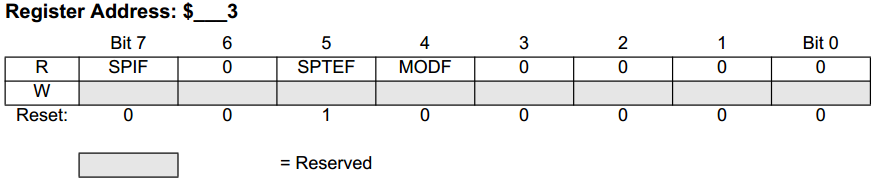

4. 狀態寄存器 SPISR

圖9. 狀態寄存器 SPISR

SPISR表征SPI傳輸狀態,只可讀,不可寫。

SPIF — SPIF Interrupt Flag

數據byte寫入SPI數據寄存器後,此位被置為1。讀取數據寄存器後,此位清零。

1 = New data copied to SPIDR

0 = Transfer not yet complete

SPTEF — SPI Transmit Empty Interrupt Flag

1 = SPI Data register empty 表示發送數據寄存器為空,可以接收待發送數據

0 = SPI Data register not empty 此時忽略任何寫入數據寄存器的指令

MODF — Mode Fault Flag

如表1,錯誤檢測功能使能後,MODF表示檢測到SPI模式錯誤。

1 = Mode fault has occurred.

0 = Mode fault has not occurred

根據Motorola的定義,SPI僅提供一種錯誤——即模式錯誤(Mode Fault Error)——的檢測機制,通過SS管腳狀態判斷SPI總線上是否存在兩個及以上的設備同時驅動SCK和MOSI。模式錯誤檢測僅適用於主設備(前提是在寄存器中激活此功能)。對於從設備,SS總是作為片選信號的。

在發生模式錯誤後(MODF = 1),系統通過寫入控制寄存器SPICR1(使設備由Master改為Slave模式,SCK、MISO和MOSI表現為高阻態以避免與總線上其它驅動設備沖突),隨後系統自動將此bit置為零(MODF = 0)。

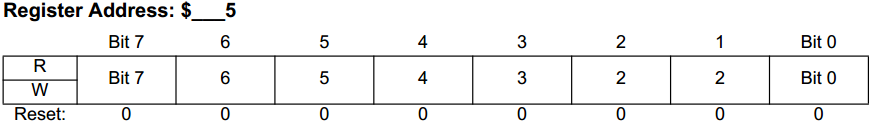

5. 數據寄存器 SPIDR

圖10. 數據寄存器 SPIDR

SPIDR作為SPI收發兩用的寄存器,數據在寫入SPIDR後進入待傳輸隊列,隊列中的數據字節在前面數據傳輸結束後立即進行傳輸。狀態寄存器SPISR的SPTEF位表示數據寄存器可以接收新數據。數據寄存器接收數據完畢後將SPIF置為1。

如果SPIF已經置為1,但服務並未運行(not serviced),則下一個(第二個)接收的數據字節將暫存在移位寄存器中直到下次傳輸。數據寄存器中的數據字節不變。

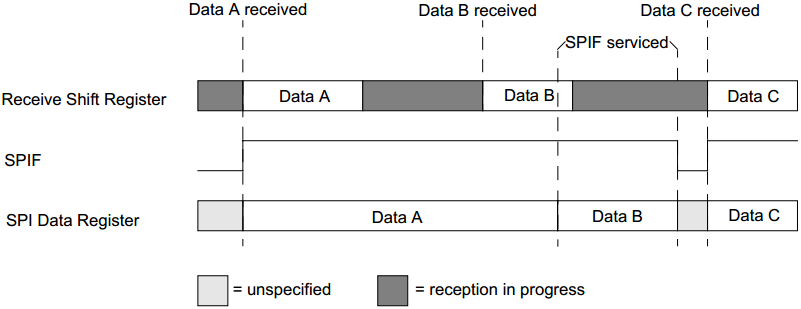

如果SPIF已經置為1,並且移位寄存器中已經暫存數據(即第二個數據字節),並且SPIF服務在第三個數據字節傳輸前完成,則移位寄存器中的數據(即第二個數據字節 )正常寫入數據寄存器,SPIF仍保持置位狀態(高),如圖11所示;

圖11. SPIF服務及時完成

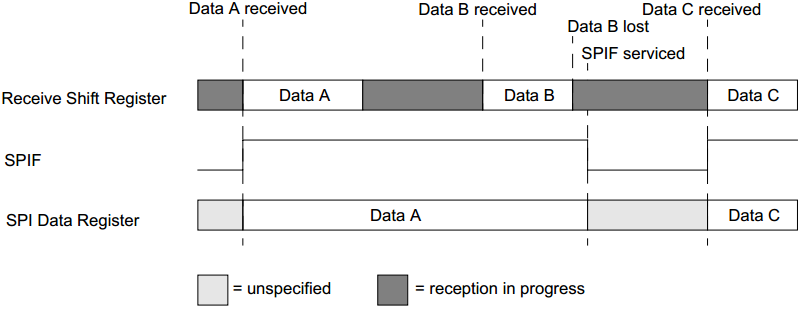

如果SPIF已經置為1,並且移位寄存器中已經暫存數據(即第二個數據字節),並且SPIF服務在第三個數據字節傳輸後完成,則移位寄存器中的數據(即第二個數據字節 )遭破壞,不能正常寫入到數據寄存器,SPIF仍保持置位狀態(高),如圖12所示 。

圖12. SPIF服務未及時完成

SPI傳輸模式

通過設置控制寄存器SPICR1中的CPOL和CPHA位,將SPI可以分成四種傳輸模式。

CPOL,即Clock Polarity,決定時鐘空閑時的電平為高或低。對於SPI數據傳輸格式沒有顯著影響。

1 = 時鐘低電平時有效,空閑時為高

0 = 時鐘高電平時有效,空閑時為低

CPHA,即Clock Phase,定義SPI數據傳輸的兩種基本模式。

1 = 數據采樣發生在時鐘(SCK)偶數(2,4,6,...,16)邊沿(包括上下邊沿)

0 = 數據采樣發生在時鐘(SCK)奇數(1,3,5,...,15)邊沿(包括上下邊沿)

四種模式如下圖13所示。先看第一列兩張圖(CPHA = 0),采樣發生在第一個時鐘跳變沿,即數據采樣發生在SCK奇數邊沿;再看第二列(CPHA =1),采樣發生在第二個時鐘跳變沿,即數據采樣發生在SCK偶數邊沿。第一行兩張圖(CPOL = 0),SCK空閑狀態為低電平,第二行兩張圖(CPOL = 1),SCK空閑狀態為高電平。

主從設備進行SPI通訊時,要確保它們的傳輸模式設置相同。對於某些場合,可能需要調整CPOL/CPHA設置以滿足設備特定要求。

圖13. SPI四種傳輸模式

時序要求

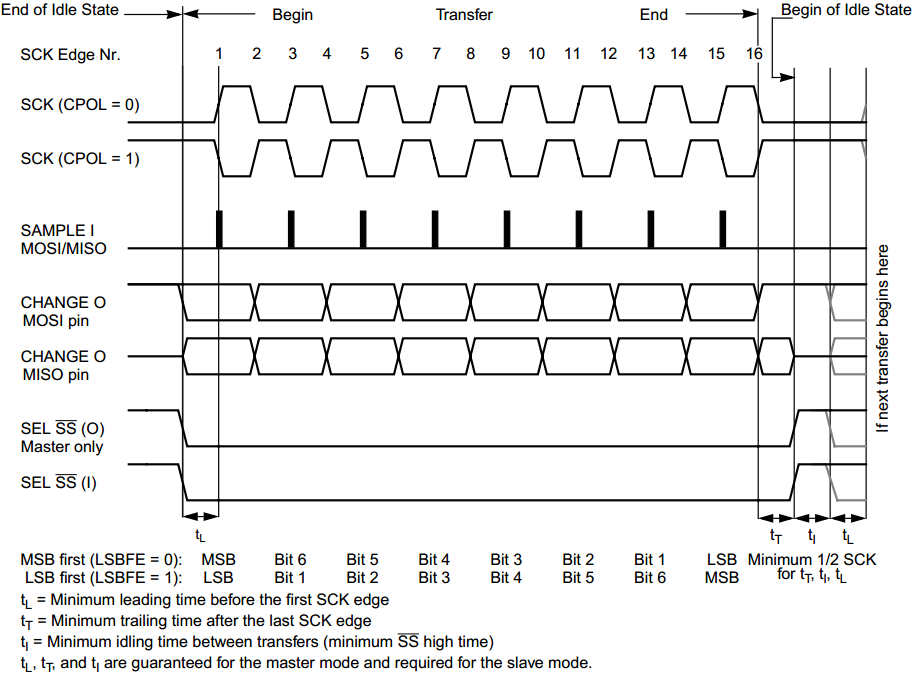

具體時序要求參考器件手冊。以下Motorola標準對CPHA = 0(圖14)和CPHA =1(圖15)不同設置時序的簡要說明:

CPHA = 0

- 有些器件在片選後數據立即出現在MOSI/MISO管腳,數據鎖存於第一個時鐘邊沿

- 片選SS先於SCK半個時鐘有效

- 在SCK的第二個時鐘邊沿,上個時鐘邊沿鎖存的數據寫入移位寄存器(MSB或LSB)

- 以此類推,數據在奇數邊沿鎖存,在偶數邊沿寫入移位寄存器

- 經過16個時鐘邊沿後,串行傳輸的數據全部寫入(並行的)移位寄存器,完成主從設備的數據交換

圖14. SPI時鐘模式(CPHA = 0)

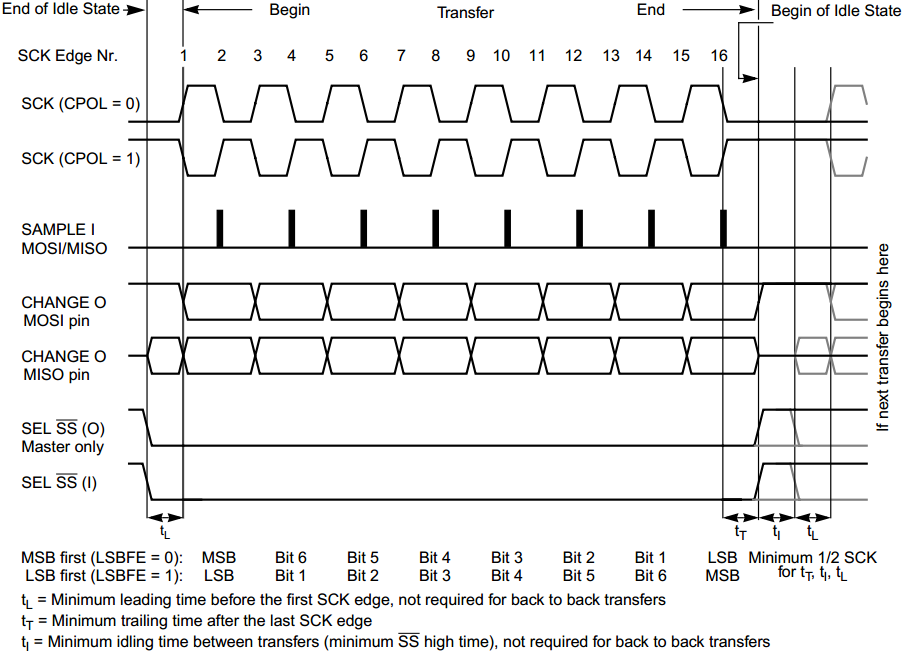

CPHA = 1

- 有些設備要求數據輸出在SCK第一個時鐘邊沿之後,數據鎖存於第二個時鐘邊沿

- 片選SS先於SCK半個時鐘有效

- 在SCK的第三個時鐘邊沿,上個時鐘邊沿鎖存的數據寫入移位寄存器(MSB或LSB)

- 以此類推,數據在偶數邊沿鎖存,在奇數邊沿寫入移位寄存器

- 經過16個時鐘邊沿後,串行傳輸的數據全部寫入(並行的)移位寄存器,完成主從設備的數據交換

圖15. SPI時鐘模式(CPHA = 1)

SPI通信過程

簡要說明ST和Spansion器件的SPI通訊過程。

1. STMicroelectronics

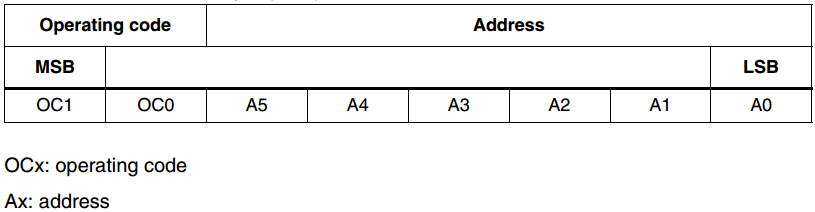

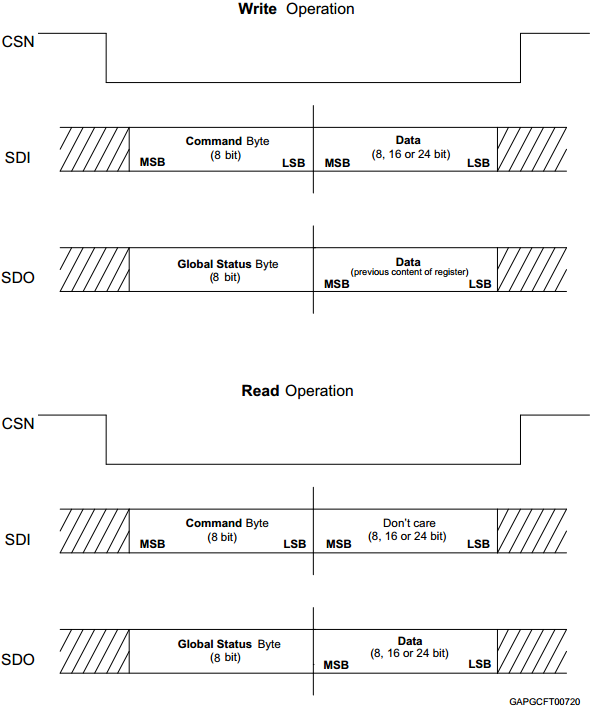

ST SPI規範定義,在系統啟動後,主設備讀取從設備8位SPI寄存器以確定從設備字長(16,24或32bit)及其它特性。每個幀(讀/寫)包括1個操作字節(Instruction Byte)和緊接著的1-3個數據字節(Data Byte)。

操作字節可能是指令字節或全局狀態字節。記住指令字節總是出現在(主從)設備的輸入管腳(SDI),全局狀態字節總是出現在(主從)設備的輸出管腳(SDO)。

- Command Byte 指令字節

圖16. 指令字節格式

指令字節前2位OC0/OC1指定SPI操作的四種類型,包括寫操作、讀操作、讀和復位狀態操作、讀取設備信息操作;

指令字節後6位Ax指定操作對象(RAM/ROM)的地址。

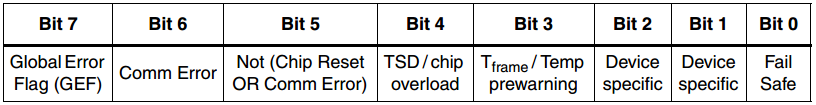

- Global Byte 全局狀態字節

圖17. 全局狀態字節格式

指示設備狀態信息,如工作模式、通訊錯誤等。

如下圖18讀寫操作數據幀格式。對於寫操作,SDO輸出全局變量字節之後緊接著地址寄存器中先前緩存的數據;對於讀操作,全局變量字節後緊接著尋址待取的數據。

圖18. SPI讀寫操作(ST)

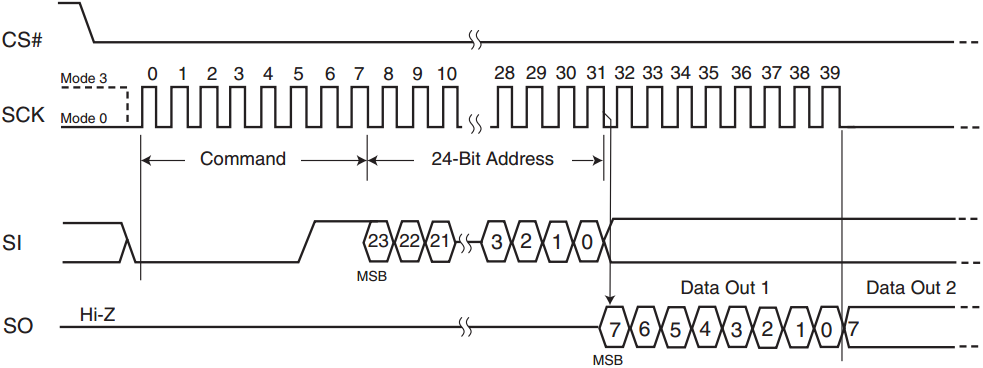

2. Spansion

以常見的SPI接口Flash為例。如圖19所示,在CS#低有效後,基於操作模式,決定在SCK的上升或下降沿觸發采樣數據。8位指令字節後緊接著24位地址,尋址Flash內部存儲塊。隨著Flash容量增大,可能需要更多的尋址位。比如Micron的N25Q等器件,需要使能4 Byte地址模式以支持容量在128Mbit以上的器件。(單個地址尋址對應1 Byte數據,則24位地址尋址最大2^24 = 16 M Byte = 128Mbit)。

圖19. SPI讀操作(Spansion Flash)

復位和中斷

復位後,寄存器值恢復初始狀態(以上寄存器表下方所列出)。對於從設備,如果復位後不對SPIDR寫入數據,它將輸出隨機數據或復位前從主設備接收到的數據;復位後SPIDR的數據全部清零。

SPI的中斷向量和優先級因設備而異。中斷請求由狀態寄存器SPISR中MODF、SPIF和SPTEF位邏輯或產生。

協議分析

利用示波器或邏輯分析儀的SPI協議分析功能(電氣特性 & 譯碼),可以快速定位通信鏈路上出現的問題。示波器支持不同的觸發方式,以Tektronix示波器為例,其支持SPI的觸發方式包括:

- SS觸發,基於片選信號狀態變化觸發

- SOF觸發,根據時鐘空閑時間確定Start Of a Frame觸發

- MOSI觸發,基於MOSI上特定的數據格式觸發

- MISO觸發,基於MISO上特定數據格式觸發

- MOSI/MISO觸發,基於MOSI和MISO上特定數據格式觸發

I2C & JTAG

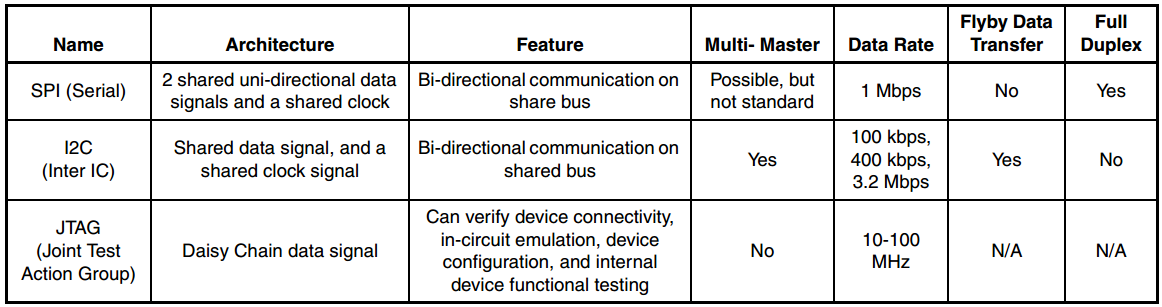

SPI和I2C,JTAG對比參考表3:

表3. SPI, I2C和JTAG協議概覽

參考資料

1. Serial Peripheral Interface Bus -Wikipedia

2. SPI Block Guide V04.01 -Motorola

3. KeyStone Architecture User Guide: Serial Peripheral Interface, Literature Number: SPRUGP2A -Texas Instruments

4. TN0897: ST SPI Protocol -STMicroelectronics

5. Comparing Serial Interfaces -Spansion

6. Serial Peripheral Interface Tutorial -Sparkfun

7. Debugging Serial Buses in Embedded System Designs -Tektronix

來源【轉】SPI總線協議