PowerPC中斷系統簡介(一)

PowerPC處理器的中斷系統由兩部分組成,一是內核的中斷及異常的處理;二是中斷控制器。以P2020處理器為例,包括E500內核中斷及異常處理系統和OpenPIC中斷控制器。在E500內核中,包含兩種可以暫時中止處理器運行當前指令的事件、中斷和異常。其中,異常是由E500內核產生的,如出現非法指令,訪問存儲器時出現TLB Miss等情況;而中斷通過處理器內核的外部引腳,如int,cint和mcp信號有效時產生的事件。

1.1 內核中斷向量

中斷向量是指中斷或者異常程序的入口地址。基於603E內核的PowerPC處理器,中斷向量為一個固定的物理地址。在這些處理器進入中斷和異常處理程序時,

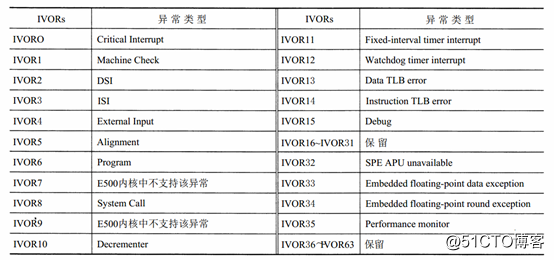

在E500內核中,使用IVPR和IVORx寄存器共同確定中斷或者異常程序的入口地址。其中,IVPR寄存器提供中斷程序入口地址的第0~15位,IVORx提供中斷程序入口地址的第16~27位,而中斷程序的入口地址的第28~31位為0。IVORx與異常的對應關系如圖 1.1所示:

圖 1.1 E500內核中斷向量表

1.1 外部中斷處理流程

E500內核的外部中斷由三部分組成,分別為Machine Check

在PIC中,P2020處理器設置了一些寄存器位,將中斷映射為電平或者邊沿觸發,但這些中斷觸發條件需要以電平的形式傳遞給E500內核。E500內核在進入中斷和中斷返回時都

要進行程序上下文的切換。頻繁的中斷將會極大影響處理器的效率。在E500內核中,一個完整的中斷處理流程如下:

1. E500內核捕捉到硬件中斷信號

2. E500內核在捕捉到硬件中斷信號後,需要做一些必要的準備,之後才可以進入外部中斷處理程序。這些準備帶來了一些外部中斷處理的延時,這些延時不可避免。首先E500內核清除在指令完成隊列CQ中的所有指令,除了以下三種指令:

1) 在CQ0中的對保護區域(Guarded)的讀操作指令。

2) 對禁止Cache內存區域操作的指令。

3) stwcx.指令。

這些指令執行完畢後,E500內核才可以進入中斷模式。在清除CQ後,E500中斷處理模塊從相應的中斷向量處預取指令到IQ中。這些中斷的預處理過程,其主要目的是為中斷處理程序準備一個“幹凈”的空間,保證中斷處理程序與被中斷程序之間不相互幹擾。由此可見,E500內核進入中斷處理程序之前,隱式地進行了指令同步操作。

3. E500內核將中斷程序的返回地址保存在SRR0中;將程序的MSR寄存器保存在SRR1中。對於一些特殊的異常,如DSI、ISI和TLB Miss等,E500內核還會自動保留E500內核的其他一些寄存器。

4. E500內核將MSR寄存器的CE、ME、DE位保留,其他位全部清零。因此E500內核在進行外部中斷處理程序時,仍然可以被Critical中斷,Machine check中斷和調試中斷程序重入,但是不能被外部中斷立即重入。在Linux PowerPC中,外部中斷處理程序會選擇合適時機使能MSR寄存器的EE位,以支持外部中斷的重人。

5. MSR中的PR、EE、IS和DS位將被清除,因此E500內核在超級用戶模式中,運行中斷處理程序時,對程序空間和數據空間的訪問都要在地址空間0上進行。

6. E500內核將根據IVPR,IVOR4寄存器確定中斷向量,進行中斷程序的執行。

7. 在中斷處理程序執行完畢後,使用rfi指令進行中斷返回。rfi指令將從SRR1寄存器中恢復MSR寄存器的值,並從SRR0寄存器中獲得程序返回地址。rfi指令在進行程序正文切換之前還會進行指令和數據的同步,還給被中斷的程序一個“幹凈”的空間,之後E500內核進行中斷返回。

PowerPC中斷系統簡介(一)