PCIE協議解析 synopsys IP loopback 讀書筆記(1)

1 Overview

Core支持單個Pcie內核的Loopback功能,該功能主要為了做芯片驗證,以及在沒有遠程接收器件的情況下完成自己的回環。同時,Core也支持有遠程接收器件的loopback,在該中情況下,遠程接收器件稱為loopback slave。該種模式可以用來完成板級的debug,BER測試,系統調試。

在做Loopback的時候需要註意將“Link up”強制寫成1(根據specification該位應該是0),造成系統處於L0狀態的假象,以便系統完成link的initialize。

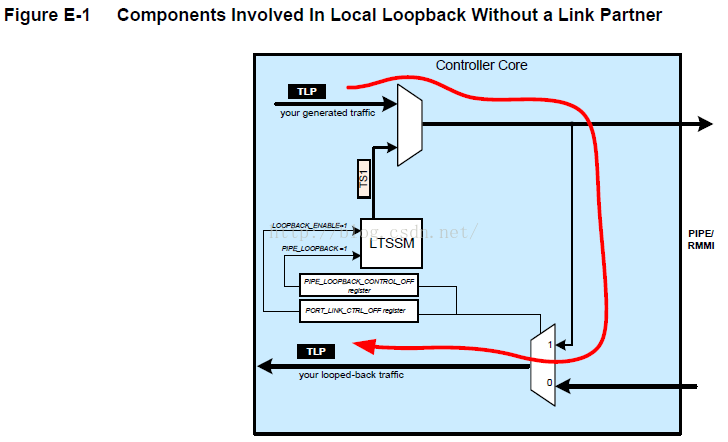

1.1 Local Digital Loopback (PIPE/RMMI)

本地的Loopback分為3個階段:Entering Local Loopback、In PIPE Loopback、Exiting Local Loopback

1.1.1 Entering Local Loopback

Loopback將PIPE/RMMI RX 與自身的PIPE/RMMI TX相連,在該種Loopback模式下,只能運行LTSSM(link training and statues statemachine),而且在該狀態下無法進行自身的training和進入到L0狀態。進入local loopback的流程如下:

? 先要disable“Gen3 Control Register GEN3_RELATED_OFF.

? Set the PIPE_LOOPBACK bit in the PIPE_LOOPBACK_CONTROL_OFFregister.

? Set the LOOPBACK_ENABLE bit in the PORT_LINK_CTRL_OFF register.

1.1.2 In PIPE Loopback

在該Loopback 模式下,通過虛擬系統進入L0狀態,可以進行link initialize。在進入了Loopback mode以後,Core會為VC0(??)的flow control進行初始化。當該初始化完成後,application就可以通過XALI0/1/2接口發送TLP。當TLP包 loopback回來後,application 需要發送complete以響應自身發的TLP包。當TLP和DLLP被發出同時被收回時,接口將對自身啟動flow control。在L0階段,當TLP因為link 錯誤而沒有被接收到時,TLP包將會被重新發送。TLP的發送將會像正常的link一樣進行credit 檢測,而接收,也會在L0階段進行正常的error check和filter check。

MessageConsiderations

當接口是一個上行接口(USP),你必須保證沒有使能生成的error message。當有錯誤發生在PCIelink時,同時你使能了error message的生成,那麽USP將會生成一個 Error Message。有接口生成的數據包將會loopback到他自身,而USP不期望接收message,他將會生成一個附加的message。(是說系統會被阻塞麽??)

在進入L0階段時,DSP接口必須自動的發送Set_Slot_Power_Limitmessage,而該message將會被自身發送並且接收回來。但是DSP接口是不期望接收到Set_Slot_Power_Limit message的,所有該message將會被作為無效的message,同時Device Status 中的unsupported requestdetected bit將會被置位。

在DSP接口中,Core內部生成的message 將會與application通過XALI0/1/2生成的TLP混合在一起發送。

Enumeration and BAR Setup

你必須配置BARS(USP),memory/IO rangs(DSP),將memoryspace 和 bus master 置位,以便可以接收filter accepts TLP。或者,可以將filter rules關掉,以便一些本該被濾掉的TLP能夠被接收。

在Loopback 模式下,可以通過DBI 初始化BAR。

Gen3 Operation

Youmust set the Gen3 Equalization Disable bit in the “Gen3 Control Register” GEN3_RELATED_OFF, as the PHY has no role in local loopback.

1.1.3 Exiting Local Loopback

Toexit loopback mode:

■ Clear the PIPE_LOOPBACK bit in the PIPE_LOOPBACK_CONTROL_OFF register.

■ Clear the LOOPBACK_ENABLE bit in the PORT_LINK_CTRL_OFF register.

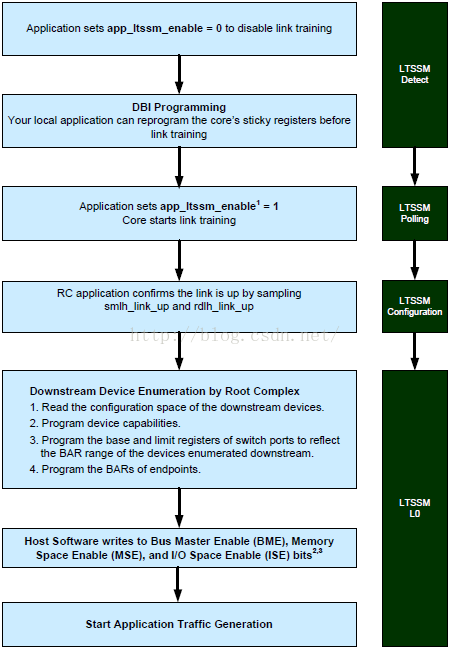

1.2 配置流程

在loopback模式下,好像沒有提到角色為RC或EP,而稱為Loopback master 和salve,所以我認為loopback的時候不區分RC和EP的,但是有USP和DSP的區別,不知道怎麽設置???

這個流程是我自己根據手冊推敲的,不知道對不對:

1、 SII app_ltssm_enable = 0 disablelink training;

2、 DBI 配置系統基本信息

3、 SII app_ltssm_enable = 1 enable link training(這裏應該配置不會成功);

4、 DBI “Link up”強制寫成1(具體是哪個寄存器需要找一下),讓系統認為link training 已經完成,並且進入了LTSSM L0階段

5、 DBI 進入loopback

? 先要disable“Gen3 Control Register GEN3_RELATED_OFF.

? Set the PIPE_LOOPBACK bit in the PIPE_LOOPBACK_CONTROL_OFFregister.

? Set the LOOPBACK_ENABLE bit in the PORT_LINK_CTRL_OFF register.

6、設置BAR(USP),而如果是DSP,設置memory/IO ranges,在前期可以turn off the filter rules。

7、 開始傳輸TLP。

轉載:https://blog.csdn.net/yijingjijng/article/details/48028695

PCIE協議解析 synopsys IP loopback 讀書筆記(1)