[轉]Vivado IP核生成設置

vivado中design with ip相比於ise感覺還是改進了。

首先我們簡單介紹一下vivado中design with ip的設計過程:

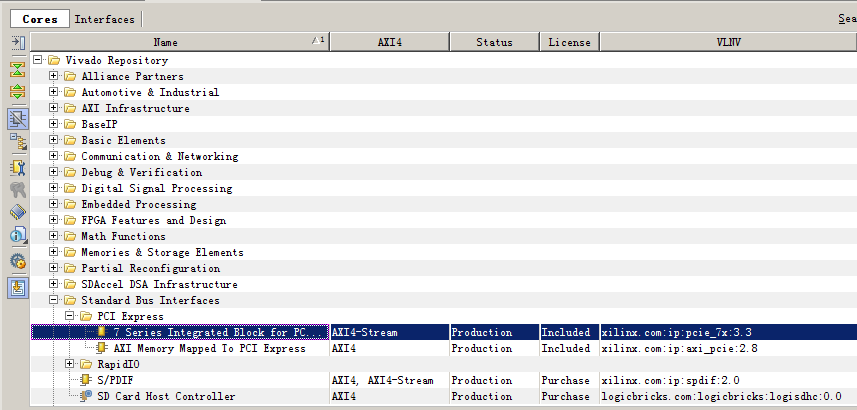

(1)打開IP Catlog定制自己的IP設計,比如這裏我們選擇Standard Bus Interface-PCI Express-7 Series Integrated Block for PCIE,然後右鍵Customize IP,就會出現一個定制IP的界面:

我們根據需要配置就行,接著我們就要產生對應IP的輸出文件了,這裏輸出文件這有很多值得註意的地方。

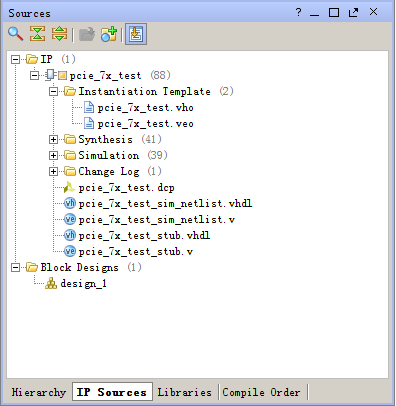

首先,選擇是否Using Core Container,這個設置是在Tool-Project Settings-IP裏,Core Container作用是把IP生成的各種文件打包成一個文件存儲,等到使用使用IP模塊的時候再從.xcix中解析出來就行;如果不使用Core Container,那麽最後IP的輸出文件各個獨立出來,存儲也是分開存儲。但是不論是不是用Core Container,vivado工程中顯示的IP核的結構都是沒有什麽區別的:

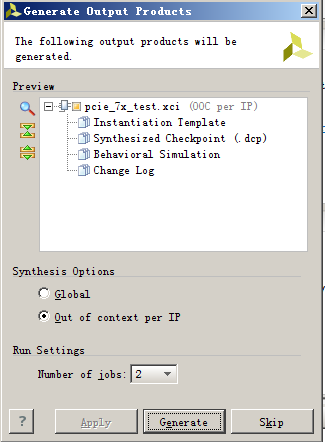

然後,就是生成IP輸出文件註意的地方,是選擇Global還是Out of context per IP:

vivado默認是第二種,Out of context per IP是指讓vivado在綜合的時候對IP進行單獨綜合,生成.dcp文件,然後再工程要用到IP的時候,只需從.dcp文件中解析出對應IP的網表文件即可,而不需對IP進行重新綜合,這樣的方式可以加快綜合的速度;而Gobal選擇則是每次工程綜合的時候,IP核都會和工程一起綜合,這樣綜合的時間就很長,而且Global選項不會產生.dcp文件,因為工程綜合的時候是對IP核的源碼進行綜合的。

(2)把IP加到自己的工程中,這裏假設綜合是采用Out of context per IP進行,如果要把IP和加到自己工程中,我們就需要IP核的頂層設計模塊,而由於采用Out of context per IP的時候只會輸出包含網表的.dcp文件,所以工程用到IP的時候是不會直接調用源碼模塊的。而是會調用一個*stub.v的Black Box模塊,這個模塊值包含IP和頂層模塊的輸入輸出定義,工程表面上是調用這個模塊,實際上是解析.dcp文件中的網表,這樣工程就可以進行綜合了。

以上就是design with IP的大致的過程,關於design with IP的仿真,這裏暫且不說,以後會總結。

[轉]Vivado IP核生成設置