異步fifo設計(2)

詳見https://www.cnblogs.com/aslmer/p/6114216.html

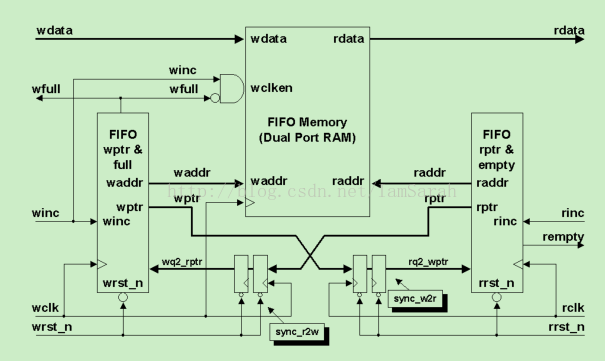

首先看一下異步fifo設計的整體框圖:

在該設計中會有6個小模塊:

1、fifo.v這個模塊是頂層模塊;

2、fifomem.v:這個模塊是fifo的內存緩沖器,該內存屬於雙端RAM

3、sync_r2w.v:這個模塊是將讀指針rd_ptr同步化到寫的時鐘域;

4、sync_w2r.v:這個模塊是將寫指針wr_ptr同步化到讀的時鐘域;

5、rd_ptr_empty:這個模塊是判斷fifo是否處於空狀態;

6、wr_ptr_full:這個模塊主要是判斷fifo是否處於滿狀態;

異步fifo設計(2)

相關推薦

異步fifo設計(2)

.cn htm html 模塊 iss 技術分享 .html font ext 詳見https://www.cnblogs.com/aslmer/p/6114216.html 首先看一下異步fifo設計的整體框圖: 在該設計中會有6個小模塊: 1、fifo.

JavaScript高級程序設計(2)在HTML中使用JavaScript

有效 頁面 itl 延遲腳本 文件包含 其他 amp 體驗 url 本章內容:使用<script>元素、嵌入腳本與外部腳本、文檔模式對JavaScript的影響、考慮禁用JavaScript的場景。 1.<script>元素 向HTML頁面中

賬戶體系的設計(2)

體系 一個 生成 成功 機器人 讓我 人工客服 是什麽 存在 上次說到我們已經有一個最基本的賬戶體系了,他由什麽組成呢? 其實就幾個玩意。 賬戶 賬戶的余額 賬戶的流水 交易 沒了。 但是交易可能是一個虛一點的東西。 為什麽說他虛呢? 舉個例子,你在京東上買了一個東西,京東

Ajax——異步基礎知識(一)

計算 註冊事件 nbsp ajax 傳遞 ica 默認 tput response 基礎概念 1、異步請求可以做到偷偷向服務器發送請求,而頁面卻不刷新 2、get異步請求傳遞參數是通過url追加鍵值對的方式 3、post異步請求比較特殊,需要設置請求的類型 User-Ag

面向對象程序設計(2)

names 模擬 AD str 第二次作業 獲取 ace 技術 當前 第二次作業 c語言流程圖 c++類圖 二者對比 面向過程的時候,所寫的程序需要思考好每一個步驟,設定好電梯以及請求的各個變量,然後用不同的函數一步步依次調用去執行,更多的感覺是依照運行的步驟去設

C#異步編程(一)線程及異步編程基礎

public 訪問 疊加 ade 上下 closed clear stat sum 最近試著做了幾個.NET CORE的demo,看了些源碼,感覺異步編程在Core裏面已經成為主流,而對這塊我還沒有一個系統的總結,所以就出現了這篇文字,接下來幾篇文章,我會總結下異步編程

異步編程(二)用戶模式線程同步

new 如何 int32 style type mem windows 模式 內存 基元線程同步構造 多個線程同時訪問共享數據時,線程同步能防止數據損壞。不需要線程同步是最理想的情況,因為線程同步存在許多問題。 第一個問題就是它比較繁瑣,而且很容易寫錯。 第二個問

C#異步編程(五)異步的同步構造

內容 cto lease amp 並發 異步編程 分析 lis ++ 異步的同步構造 任何使用了內核模式的線程同步構造,我都不是特別喜歡。因為所有這些基元都會阻塞一個線程的運行。創建線程的代價很大。創建了不用,這於情於理說不通。 創建了reader-writer

[C++]類的設計(2)——拷貝控制(拷貝控制和資源管理)

1、類的行為分類:看起來像一個值;看起來想一個指標。 1)類的行為像一個值,意味著他應該有自己的狀態。當我們拷貝一個像值的物件時,副本和原物件是完全獨立的。改變副本不會對原有物件有任何影響,反之亦然。

【Altera SoC】基於SOPC的單通道TDC設計(2)

.debug_reset_request (cpu_debug_reset_request_reset), // debug_reset_request.reset

FPGA之FIFO設計(二)

非同步FIFO在ISE下有兩種生成方法: 法一:使用CORE Generator生成的DPRAM和自己設計的FIFO控制邏輯,將兩者連在一起就構成了FIFO。 法二:直接使用FIFO的IP核。 現在我們來做一件事情:非同步時鐘域的晶片A和

C++/C課程設計(2)工資管理系統功能說明

工資管理系統 一, 基本功能要求: 1)以密碼登入系統 密碼登入時讀取檔案info.txt(儲存員工資訊)和Admin.txt(儲存管理員息) 如果密碼錯誤或者使用者賬號不存在,會給出相應提示 二, 主功能介面 選單佈

濾波器設計(2):經典FIR數字濾波器的設計

引言以前有一篇IIR濾波器設計的文章。與IIR相對應,這篇文章主要講FIR濾波器的設計。以下一段摘自百度百科。FIR(Finite Impulse Response)濾波器:有限長單位衝激響應濾波器,又稱為非遞迴型濾波器,是數字訊號處理系統中最基本的元件,它可以在保證任意幅頻

架構設計(2)---分散式架構的演進過程

一.分散式架構的發展歷史1946年,世界上第一臺電子計算機在美國的賓夕法尼亞大學誕生,它的名字是:ENICAC ,這臺計算機的體重比較大,計算速度也不快,但是而代表了計算機時代的到來,再以後的網際網路的發展中也有基礎性的意義。計算機的組成是有五部分完成的,分別是:輸入裝置,輸出裝置,儲存器,儲存器裡面由運算器

GIS+=地理資訊+雲端計算技術——私有云架構設計(2)網路資源規劃

-------------------------------------------------------------------------------------- 宗旨:專注於"G

第十一週上機實踐專案4——類族的設計(2)

(2)以Point為基類,派生出一個Circle(圓)類,增加資料成員r(半徑),以及求面積的成員函式area,實現其他需要的成員函式,設計main函式完成測試; 程式碼 #include<i

運放穩定性連載9:單電源緩衝器電路的實際設計(2)

在圖5.16中,我們分析了緩衝器電路拓撲w/o補償原理,並給出了採用兩條反饋路徑的解決方案。我們的Aol曲線是取自廠商的資料資料(見圖5.15)。標為“緩衝器拓撲w/o 補償”的曲線是我們的直流Beta 分析結果,我們用Tina SPICE 模擬來找出高頻極點。現在我們利用十倍頻程經驗法則來調整FB#1,這是

一步一步寫Makefile(2):shell命令,萬用字元*和%區別,檔案路徑搜尋vpath VPATH

#################6:Makefile中也可以插入shell命令################ variable=main.o test1.o test2.o main:$(variable) cc -o main $(variable)

邏輯式程式設計還有用嗎?--“三維度”邏輯程式語言的設計(2)

1,邏輯程式語言能做什麼 這兩天正在構思這個“三維度”邏輯程式語言的設計系列的下一篇該怎麼寫,正好在上一篇《用寫文章的方式寫程式--“三維度”邏輯程式語言的設計(1)》有位叫做 dwcz

【轉】Verilog學習筆記簡單功能實現(八)...............異步FIFO

另一個 gif 多個 可靠 基本原理 drs bar next 不同 基本原理: 1.讀寫指針的工作原理 寫指針:總是指向下一個將要被寫入的單元,復位時,指向第1個單元(編號為0)。 讀指針:總是指向當前要被讀出的數據,復位時,指向第1個單元(編號為0)