創龍基於C66x平臺DSP與FPGA通信測試

阿新 • • 發佈:2018-11-02

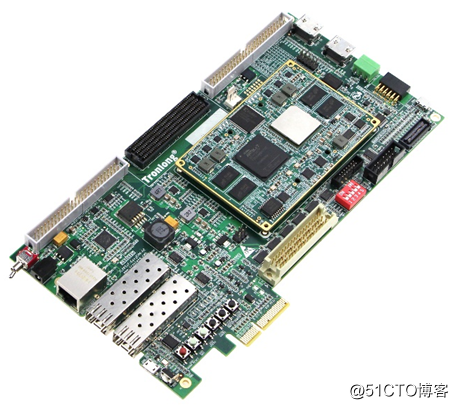

roc 步驟 pcie 進入 完成後 圖片 process afa 打開 本文為基於創龍TL665xF-EasyEVM開發板的DSP與FPGA通信測試。TL665xF-EasyEV開發板的簡介紹如下:由核心板+底板構成。

核心板DSP端采用單核TMS320C6655或雙核TMS320C6657處理器,FPGA端采用Xilinx Artix-7處理器,實現異構多核處理器架構,DSP與FPGA內部通過uPP、EMIF16、SRIO連接;

底板接口資源豐富,支持uPP、EMIF16、SRIO、千兆以太網口等多種高速接口,引出PCIe接口,單端口雙通道,每通道最高通信速率5GBaud;

SFP接口,傳輸速率可高達5Gbit/s,可接SFP光口模塊或SFP電口模塊;

雙通道XADC接口,可實現模擬到數字轉換,可靈活配置邏輯輸入;

TL665xF-EasyEVM開發板應用領域十分廣泛,可用於機器視覺、軟件無線電、雷達/聲吶、醫用儀器、光纜普查儀等。

下面進入正題:

DSP與FPGA通信需要把開發板的撥碼開關第5位撥到1,按照IBL NOR模式啟動開發板。

測試說明:DSP端通過TFTP服務器加載FPGA所需的.bit文件,並在DSP端執行命令進行測試。

(1) 測試步驟

? 部署TFTP服務器

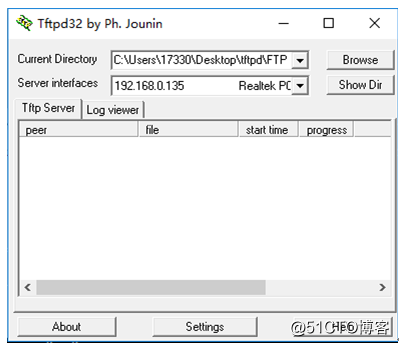

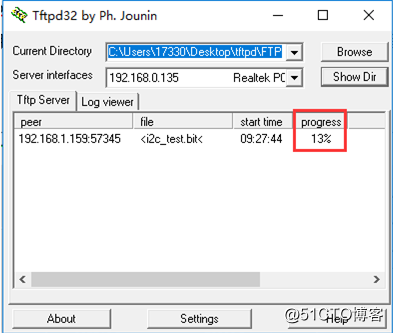

打開TFTP服務器,路徑:"光盤資料/Demo/Hostapp/tftpd32.exe",Current Directory選擇.bit文件所在路徑(非中文),Server interfaces選擇電腦終端的IP地址,如下圖所示:

核心板DSP端采用單核TMS320C6655或雙核TMS320C6657處理器,FPGA端采用Xilinx Artix-7處理器,實現異構多核處理器架構,DSP與FPGA內部通過uPP、EMIF16、SRIO連接;

底板接口資源豐富,支持uPP、EMIF16、SRIO、千兆以太網口等多種高速接口,引出PCIe接口,單端口雙通道,每通道最高通信速率5GBaud;

SFP接口,傳輸速率可高達5Gbit/s,可接SFP光口模塊或SFP電口模塊;

雙通道XADC接口,可實現模擬到數字轉換,可靈活配置邏輯輸入;

TL665xF-EasyEVM開發板應用領域十分廣泛,可用於機器視覺、軟件無線電、雷達/聲吶、醫用儀器、光纜普查儀等。

下面進入正題:

DSP與FPGA通信需要把開發板的撥碼開關第5位撥到1,按照IBL NOR模式啟動開發板。

測試說明:DSP端通過TFTP服務器加載FPGA所需的.bit文件,並在DSP端執行命令進行測試。

(1) 測試步驟

? 部署TFTP服務器

打開TFTP服務器,路徑:"光盤資料/Demo/Hostapp/tftpd32.exe",Current Directory選擇.bit文件所在路徑(非中文),Server interfaces選擇電腦終端的IP地址,如下圖所示:

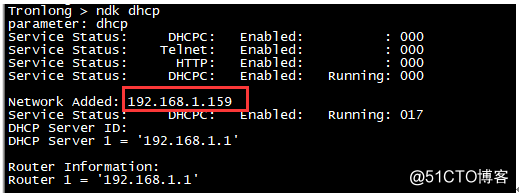

? 啟動網絡支持

在串口調試終端執行ndkdhcp命令啟動網絡支持。

? 通過TFPT加載FPGA鏡像

在串口調試終端執行命令加載FPGA鏡像,命令格式如下:

Tronlong> fpgaprogtftp[電腦終端IP][FPGA鏡像文件名]

以I2C鏡像為例:

Tronlong> fpgaprogtftp192.168.0.135i2c_test.bit

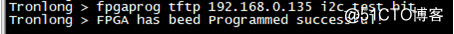

可以在tftpd服務器端看到文件傳輸進度,文件傳輸完成後開始編程FPGA,如下圖所示:

編程完成後會提示編程結果,如下圖所示:

? DSP端執行測試命令

在串口調試終端執行命令測試FPGA鏡像,以I2C為例,執行以下命令:

以下測試DSP與FPGA通過I2C、EMIF、SRIO以及文件系統方式通信,FPGA鏡像可在FPGA端光盤資料Demo中獲取。

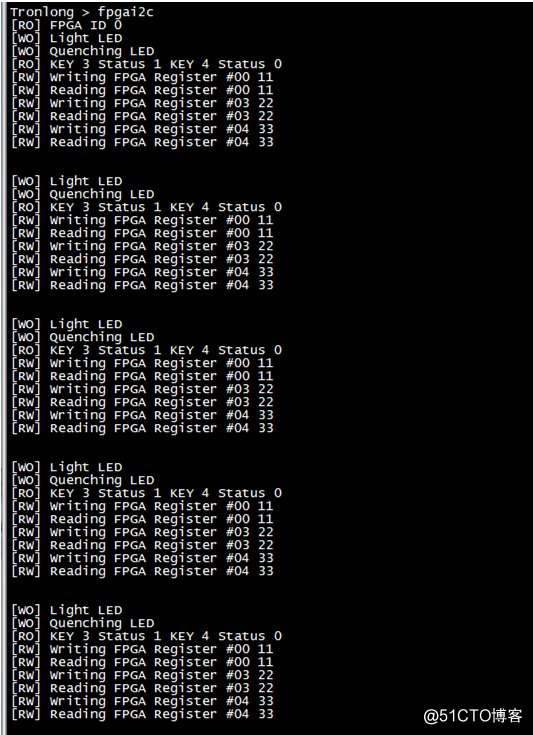

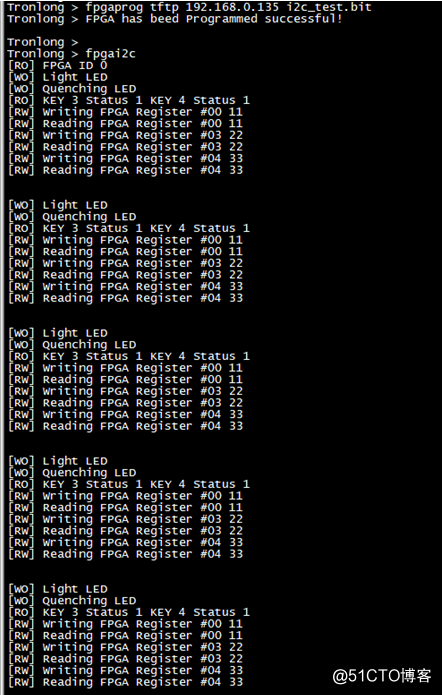

(2) DSP與FPGA I2C通信測試

按照上述測試步驟加載I2C鏡像,如下圖所示:

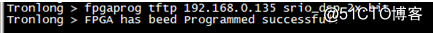

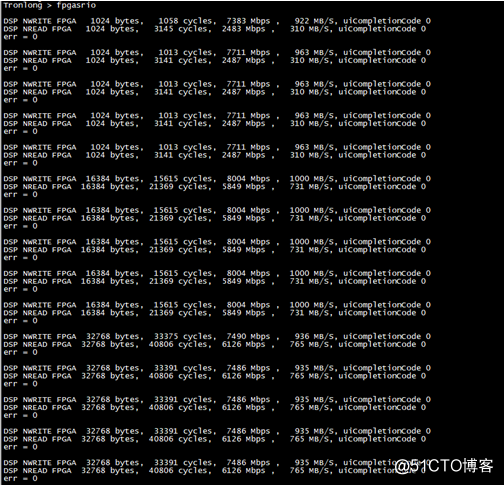

(3) DSP與FPGA SRIO通信測試

執行以下命令進行SRIO通信測試:

Tronlong> fpgaprogtftp192.168.0.135srio_dsp_2x.bit //IP以實際電腦終端IP為準

Tronlong> fpgasrio

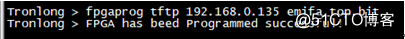

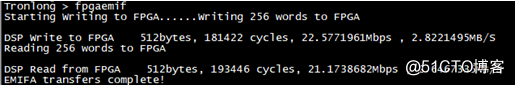

(4) DSP與FPGA EMIF16通信測試

執行以下命令進行EMIF16通信測試:

Tronlong> fpgaprogtftp192.168.0.135emifa_top.bit

Tronlong> fpgaemif

創龍基於C66x平臺DSP與FPGA通信測試