verilog學習(一)概述

PS:本系列參考夏宇聞老師的Verilog數字系統設計jiao教程,意在對verilog形成基礎的體系,留作將來查詢參考,請大家多指教。

硬體描述語言(HDL,hardware description language)是一種形式化方法來描述數位電路和系統的語言。數位電路系統的設計者利用這種語言可以從上層到下層(從抽象到具體)逐層描述自己的設計思想用一系列分層次的模組來表示極其複雜的數字系統。然後利用EDA工具逐層進行模擬驗證,再把其中需要變為具體物理電路的模組組合經由自動綜合工具轉換到門級電路網表。接下去再用專用積體電路(ASIC)或現場可程式設計門陣列(FPGA)自動佈局佈線把網錶轉換為具體電路佈線結構的實現。在製成物理器件之前,還可以用Verilog的門級模型來代替具體基本元件。

verilog HDL

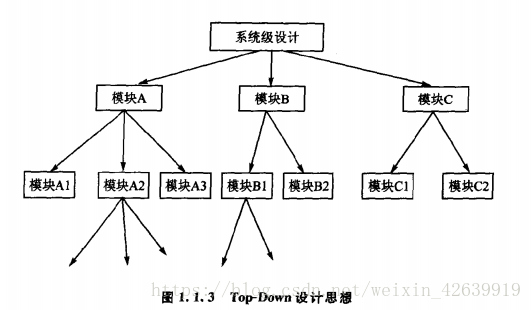

自頂向下設計的基本概念

自頂向下的設計是從系統級開始 ,把系統劃分為若干個基本單元,然後再把每個基本單元劃分為下一層次 的基本單元,一直這樣做下去 ,直到可以直接用 EDA 元件庫中的基本元件來實現為止 。

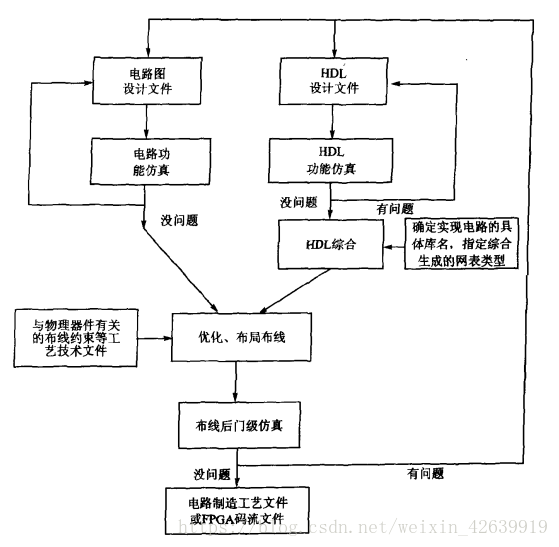

HDL設計流程圖

電路設計步驟

1、設計輸入:原理圖輸入或者硬體描述語言輸入

2、綜合:將行為級或者RTL級等設計輸入 轉化成 由基本邏輯單元組成的邏輯連線,並將RTL級檔案對映到FPGA的原語,生成綜合的網表文件。(RTL級,描述資料在暫存器之間的流動和如何處理、控制這些資料流動的模型)。

3、實現:將綜合產生的網表文件 轉化成 所選器件的底層模組和硬體原語。

C語言與verilog的比較

1、C 程 序 是 一 行接 一 行依次執行 的,屬 於順 序 結構 ,而 Veri log 描述 的硬體 是 可 以在 同 一 時 間 同 時執行的 ,屬 於並行結構 。

2、Verilog 可 用 的輸 出 輸入 函式很少 ,C 語 言 的花 樣則很 多

3、C 程 序 調 用 函 數 是 沒 有延 時特性 的 ,一 個 函式是惟 一 確 定 的 ,對 同一 個 函 數 的 不 同調 用 是 一 樣 的 。而 Verilog 中對模 塊 的不 同調 用 是不 同 的 ,即使調 用 的是 同一 個模組 ,必 須 用 不 同 的名 字 來指定 。

4、Ver ilog 的語 法 規則很死 ,限 制 很 多 ,能 用 的判 斷語 句 有 限 。仿 真速度較 慢 ,查錯 功 能 差 ,錯 誤信 息 不 完 整 。仿 真 軟 件 通 常 也很 昂貴 ,而 且 不 一 定可 靠 。C 語 言沒 有 時 間 關 系 ,轉 換後 的 Verilog 程 序 必須做到 沒 有任 何 外加 的人工延 時信 號 ,也 就 是 必須表達 為 有 限狀 態 機 ,即 RTL 級 的 Verilog,否 則將 無 法 使用 綜 合 工具把 Verilog 源 代 碼 轉 化 為 門級邏輯 。

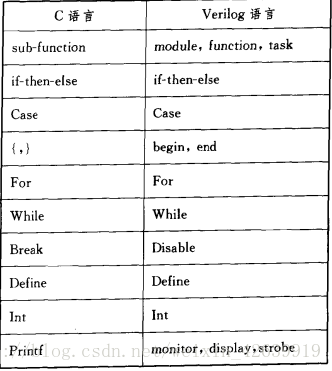

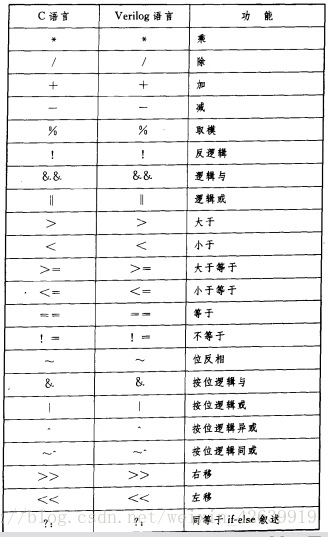

5、關鍵字和運算子比較

verilog HDL 與VDHL的比較

VHDL 的英文全名 為 VHSIC Hardware Description Language ,而 VHSIC 則是 Very High Speed lntegerated Circuit 的縮寫詞,意為甚高速整合 電路,故 VHDL 其準確的中文譯名 為甚高速整合 電路的硬體描述 語言。

Verilog HDL 和 VHDL 作為描述硬體 電路設計的語言,其共同的特點在於:

1、 能形式化地抽象表示電路的行為和結掏;

2、支援邏輯設計中層次與範圄的描述;

3、可借用高階語言的精巧結掏 來簡化電路行為的描述 ;

4、具有電路模擬與驗證機制以保證設計的正確性 ;

5、 支援電路描述由高層 到低層的綜合轉換;

6、 硬體描述與實現工藝無 關(有關工藝引數可 通過語言提供的 屬性包括進去);

7、便於文件管理;易於理解和設計重用。

但是 Verilog HDL 和 VHDL 又各有其 自己的特點。

與 VHDL相比 ,Verilog HDL 的最大優點為 :它是一種非常容易掌握的硬體描述語言 ,只要有 C 語言的程式設計基礎 ,通過 20 學時的學習,再經過一段時間的實際操作 , 一般可在 2、3個月內掌握這種設計技術。而掌握 VHDL 設計技術就比較困難 。

一般認為 Verilog HDL 在系統級抽象方面比VHDL 略差些 ,而在門級開關電路描述方面比VHDL 強得多。

verilog語法的基本概念

Verilog HDL 是一種用於數字系統設計的語言。用其描述的電路設計就是該電路的 Verilog HDL 模型,也稱為模組 。Verilog HDL 既是一種行為描述的語言也是一種結構描述的語言。這就是說 ,無論描述電路功能行為 的模組或描述元器件或較大部件互連 的 模組都可以用 Verilog 語言來建立電路模型。

Verilog 模型可以是實際電路的不同級 別的抽象。這些抽象的級別和它們所對應的模型類 型共有以下5種,現分別給以簡述 。

( 1) 系統級( system-level) :用語言提供的高階結構能夠實現所設計模組的外部效能的模型。

( 2) 演算法級( algorithm level) :用語言提供的高階結構能夠實現演算法運 行的模型 。

( 3 ) RTL 級(register transfer level) :描述資料在暫存器之間 的流動和如何處理 、控制這 些資料流動的模型 。

以上三種都屬於行為描述 ,只有 RTL 級才與邏輯 電路有明確的對應關係 。

( 4 ) 門 級( gate-level ) :描述邏輯閘以及邏輯閘之間連線的模型 。

與邏輯電路有確定的連線關係 ,以上四種數字系統設計工程師必須掌握。

( 5) 開關級( switch-level ):描述器件中三極體和儲存節點以及它們之間連線的模型 。

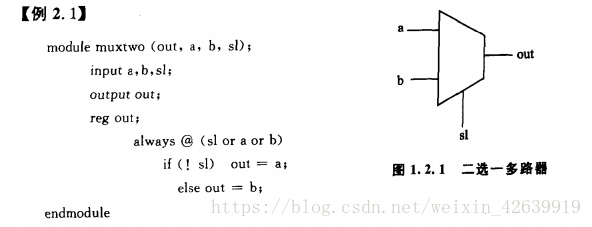

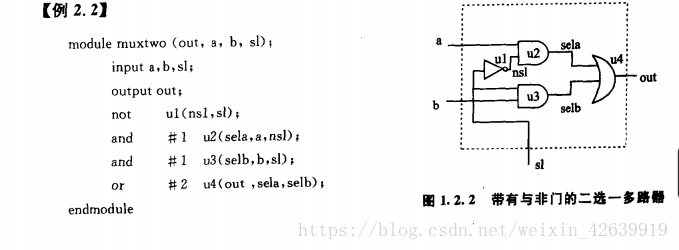

通過計算機上執行的工具進行從例2.1轉換為例2.2形式的模組,這個過程就是綜合

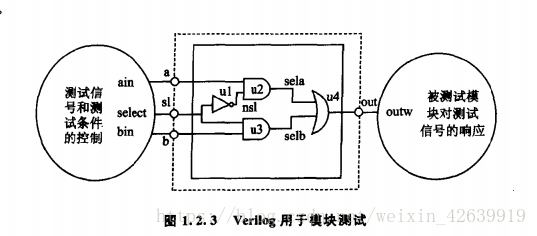

verilog用於模組的測試

Verilog 還可以用來描述變化的測試訊號 。描述測試訊號的變化和測試過 程的模組叫做 測試平臺(testbench 或 testfixture),它可以對上面介紹的電路模組 (無論是行為的或 結構 的〉進行動態的全面測試 。

下面是對例2.1多路選擇器的全面測試

'include "muxtwo.v"

module t;

reg ain,bin,select;

reg clock;

wire outw;

initial //把暫存器變數初始化為一確定的值

begin

ain=0;

bin=0;

select=0;

clock=0;

end

always #50 clock=~clock ;//產生一個不斷重複的週期為100個的時鐘訊號clock

[email protected](posedge clock)

begin

#1 ain={$ random}%2;//{$ random}為系統任務,會產生一個隨機數

#3 bin={$ random}%2;//分別延遲1和3個時間單位後產生隨機的位訊號流ain和bin

end

always #10000 select=! select;//產生週期為10000個單位時間的選通訊號變化

muxtwo m(

.out(outw),

.a(ain),

.b(bin),

.sl(select)

);

/*“.”表示埠;後面緊跟埠名,其名稱必須與muxtwo模組定義的埠名一致;

小括號內的訊號名為與該埠連線的訊號線名,可以用別的名,但必須在本模組中定義,說明其型別。*/

endmodule