Quartus II Shift Register (RAM-based) 詳解

阿新 • • 發佈:2018-11-11

1.建立

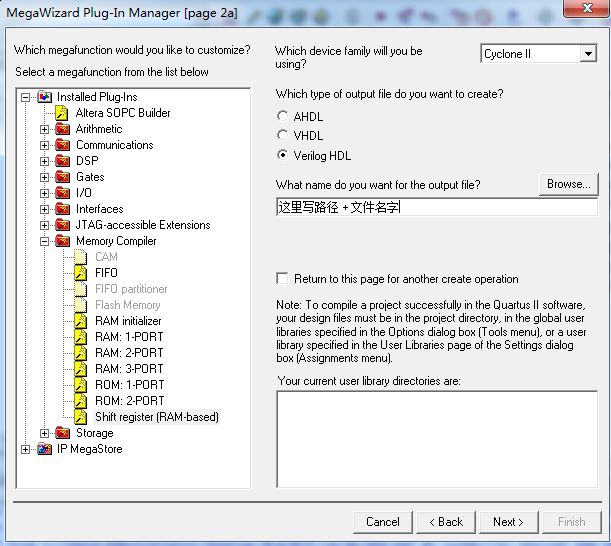

左邊選擇Shift Register 使用什麼晶片 右上就選什麼 選擇語言 還有工程路徑和名字

2.配置

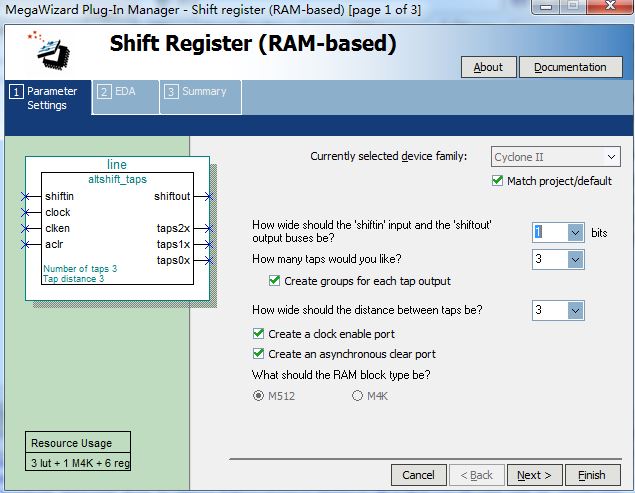

埠 1bit 三個tap 抽頭 每個獨立分組 每個間距是3 即3X3的一位暫存器

建立時鐘使能埠 和 非同步清零埠

配置完直接finish就可以

3.模擬除錯

1.程式碼

module cs( input clock, input aclr, input clken, input shiftin, output shiftout, output taps0x, output taps1x, output taps2x ); line l( .clken(clken), .clock(clock), .aclr(aclr), .shiftin(shiftin), .shiftout(shiftout), .taps0x(taps0x), .taps1x(taps1x), .taps2x(taps2x) ); endmodule

2.波形圖模擬

aclr是非同步復位,只要其為高電平 即復位 如果不需要復位在配置的時候可以不選create這個

clken是使能 其為高電平且 在alcr為低電平的情況下 在clk時鐘的上升沿 暫存器移位 不需要也可以不create這個

shifitin 移位暫存器 的輸入端 shiftout最終輸出端

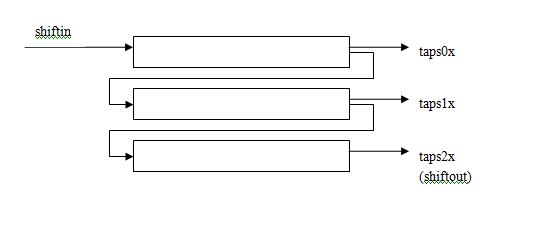

過程: shiftin -> taps0x -> taps1x -> taps2x(shiftout)