Allegro PCB簡單操作(一)

Setup-User Preference-Path-Library設定路徑主要設定psmpath和padpath

Psmpath設定不正確將導致載入器件失敗

File-Import-Logic匯入網表

若用Capture軟體生成的選擇Designentry CIS

勾選Create user-defined properties

單擊Import Cadence

成功則匯入了網表

PCB Designer:

畫外框 Class Geometry SubClass Outline

X 0 0;選取一個點

Ix 5000;在x軸上增加5000;

Iy 5000;在y軸上增加5000;

Ix 5000 5000:在x軸上增加5000並且在y軸上增加5000;

用線畫可以用Chafmer修改導角

若用矩形畫則不能用。

Setup-Area可以設定哪些地方可繪製,哪些地方不可繪製。

放置元件 Place-Manually,或單擊第二個-more options。

彈出匯入的網表文件裡的元件。

右端可以選擇元件,根據不同的方式查詢。

高階設定 選上Library。

中間是自動擺放軟體。AutoHide是擺放元件時對話方塊自動隱藏。

Place-Quickplace開啟快速放置功能

根據實際需求選擇

Place by room 使用恰當可極大地節省精力。

Room 編輯:在capture中進行在資料夾右擊可更改一個資料夾所有元件的ROOM,單擊Edit ObjectProperties。

Filter by選擇Cadence-Allegro

找到ROOM,右擊,輸入隨意字串,如ep3c25。

同樣,在原理圖雙擊元件也可找到ROOM欄編輯。注意:同一元件如U6A,U6B ROOM值需一樣。

編輯好以後 單擊dsn檔案Tools-create Netlist生成網表文件。關閉Capture

PCB Designed重新匯入網表,便能在Place by room中看到剛才設定的ROOM。

先畫RoomOutline,SetUp-OutLIne-Room OutLine,最上面為模式,Room Name選擇為哪個Roon畫區域。

選Edit可重新編輯

畫完後,Quickplace進行放置元件。

Capture 和 allegro互動佈局,Options-Preferences-Miscellaneous 選擇EnableIntertool Communication 便可以使能互動佈局工具,allegro選擇palce-manually 在capture中選中要擺放的元件,allegro中選中的元件會掛在滑鼠上。Capture選中元件,allegro中將元件高亮,在allegro 中選擇高亮命令,選中元件,capture會將原理圖中所有相關部分高亮。在allegro選擇高亮命令,capture和allegro將互相高亮網路。以上操作對兩屏及以上使用者相當方便

注意:工程不能有中文名!

AllegroPlace-Manually ,單擊capture上的元件,滑鼠移到allegro介面中,便有Footprint出現

在allegro中Display-HighLight,單擊capture或allegro上的原件,便可定位到對方元件並高亮。Net高亮同理。

使用allegro進行電氣約束,SetUp-Constraints-ConstraintManager或

左側分別為電氣約束,物理約束,間距約束,同網路間距約束等

選擇部分Net 右鍵-Create-Bus可設定匯流排,同樣可以設定差分對。

上部分是設定約束,下部分是應用設定

約束可以設定單端線阻抗,最大過孔數量,匹配過孔,最大最小延時,總長約束,差分對的約束等。在Electrical Constraint Set中右鍵->Create_>electricCSet可設定約束。然後在Net Routing中便可設定。

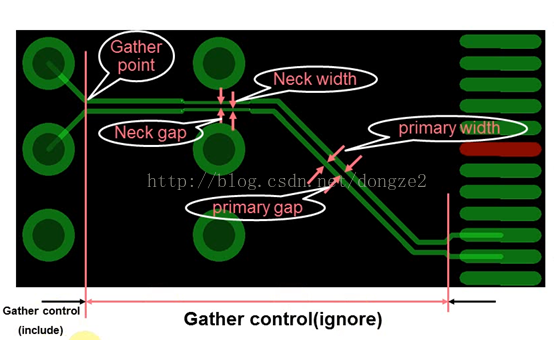

下圖是差分對示意圖

物理約束同理。