fpga復位的幾種方法

FPGA的復位方法幾種方法

構建最理想的復位結構有助於改善設計的密度、效能和功耗

作者: E.Srikanth

解決方案開發工程師

賽靈思公司

[email protected]

在 FPGA 設計中,復位起到的是同步訊號的作用,能夠將所有的儲存元件設定成已知狀態。在數位電路設計中,設計人員一般把全域性復位作為一個外部引腳來實現,在加電的時候初始化設計。全域性復位引腳與任何其它輸入引腳類似,對 FPGA 來說往往是非同步的。設計人員可以使用這個訊號在 FPGA 內部對自己的設計進行非同步或者同步復位。

不過在一些提示和技巧的幫助下,設計人員可以找到更加合適的復位結構。理想的復位結構可以改善 FPGA 中器件的利用率、時序和功耗水平。

瞭解觸發器復位行為

在深入探討復位技術之前,有必要了解 FPGA Slice 內觸發器行為。基於賽靈思 7 系列架構的 FPGA 器件的每個Slice中含有 8 個暫存器,所有這些暫存器都是 D 類觸發器。這些觸發器共享一個通用的控制集。

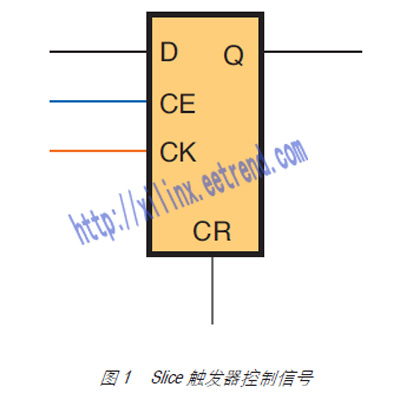

觸發器控制集的組成包括時鐘輸入(CLK)、高電平有效晶片使能端 (CE) 和高電平有效 SR 埠。觸發器中的 SR 埠既可用作同步置位/復位埠,也可用作非同步預設/清除埠(見圖1)。

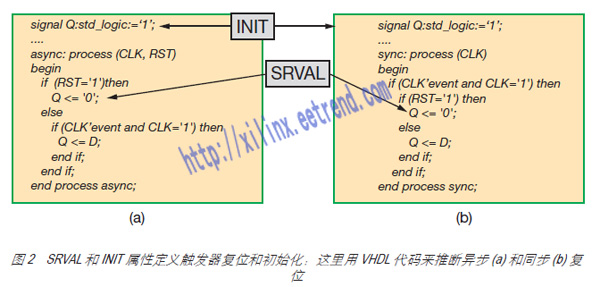

推斷觸發器的 RTL 程式碼也能推斷觸發器準備使用的復位型別。當復位訊號出現在 RTL 過程的敏感列表中時,該程式碼就會推斷非同步復位(如圖 2a所示)。隨後綜合工具將推斷出一個觸發器,該觸發器的 SR 埠被配置為預設或清除埠(用 FDCE 或者 FDPE 觸發器原語來表示)。在 SR 埠被斷言後,觸發器的輸出會被立即強制賦予給觸發器的 SRVAL 屬性。

在同步復位的情況下,綜合工具推斷出的觸發器,其 SR 埠被配置為置位或復位埠(用FDSE 或 FDRE 觸發器原語來表示)。SR 埠被斷言後,觸發器的輸出將在時鐘週期的下一個上升沿被強制賦予給觸發器的 SRVAL 屬性。

此外,還可以把觸發器的輸出初始化為 INIT 屬性規定的值。在配置過程中,當全域性置位/復位 (GSR) 訊號被斷言時,INIT 值就會被載入到觸發器。

賽靈思 FPGA 中的觸發器能夠同時支援非同步的和同步的復位與置位控制。但是,底層觸發器每次只能實現一個設定/重設/預設/清除。如果為 RTL 程式碼中的多個設定/重設/預設/清除狀況進行編碼,那麼其中一種狀況的實現將使用觸發器的 SR埠,其餘的狀況則使用架構邏輯,因而會佔用更多的 FPGA 資源。

如果其中一個狀況是同步的,另一個狀況是非同步的,非同步狀況的實現將使用 SR 埠,同步狀況的實現則使用架構邏輯。一般來說,應儘量避免出現一個以上的設定/重設/預設/清除狀況的出現。另外,對於 Slice 中的每個觸發器組(4 個觸發器為一組),只有一個屬性可以確定觸發器的 SR 埠是同步的還是非同步的。

復位方法

不管使用哪種復位型別( 同步或是非同步),一般都需要讓復位與時鐘同步。只要全域性復位脈衝的持續時間足夠長,器件上所有的觸發器都會進入復位狀態。但是,取消復位訊號的斷言必須滿足觸發器的時序要求,才能保證觸發器順利地從復位狀態轉換到正常狀態。如果不能滿足時序要求,觸發器就會進入亞穩定狀態。

另外, 為了某些子系統的正常執行,比如狀態機和計數器,所有的觸發器必須在同一個時鐘邊沿退出復位。如果狀態機的不同部分在不同的時鐘週期退出復位狀態,狀態機可能會進入非法狀態。這就要求取消復位斷言必須與時鐘同步。

對在給定時鐘域中使用同步復位方法的設計來說,使用標準的亞穩態解決電路(兩個背對背觸發器)就足以把全域性復位引腳同步到特定的時鐘域。這個同步復位訊號可以利用觸發器上的同步SR 埠初始化該時鐘域內的所有儲存元件。由於待復位的同步器和觸發器都處於同一時鐘域,因此該時鐘域的標準PERIOD 約束的包括同步器與觸發器之間的路徑時序。器件中的每個時鐘域都需要使用單獨的同步器為該時鐘域生成一個同步的全域性復位。

現在進入實質部分。下面是一些具體的提示和技巧,有助於您找到最佳的設計復位策略。

技巧 1:當驅動觸發器的同步 SR埠時,每個時鐘域都需要全域性復位的區域性版本, 並與該時鐘域同步。

有時候不能保證設計的某個部分具備有效的時鐘。這種情況通常發生在這樣的系統中,即系統使用的時鐘為恢復時鐘,或者系統使用的時鐘源於熱拔插模組。在這種情況下,可能需要使用觸發器上的非同步 SR 埠,通過非同步復位的方法對設計中的儲存元件進行初始化。即便儲存元件使用的是非同步 SR 埠,取消復位沿斷言仍然必須與時鐘同步。這項要求主要體現為觸發器的復位恢復時序弧,這類似於要求將非同步 SR的取消斷言沿設定為與時鐘的上升沿同步。如果不能滿足這個時序弧的要求,就會導致觸發器進入亞穩態,同步子系統也會進入異常狀態。

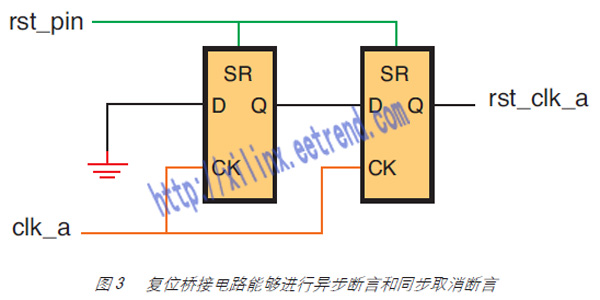

圖 3 所示的復位橋接電路提供了一種機制,可以對復位進行非同步斷言(故在無有效時鐘的情況下也可以進行)以及對復位進行同步取消斷言。在這個電路中,假定兩個觸發器的 SR埠具有非同步置位功能 (SRVAL=1)。

可以使用該復位橋的輸出來驅動給定時鐘域的非同步復位。這種經過同步的復位能夠使用觸發器的非同步 SR 埠對該時鐘域中的所有儲存元件進行初始化。器件中的每個時鐘域仍需要一個單獨的、經過同步的、由單獨復位橋生成的全域性復位。

技巧 2:復位橋接電路實現了一種安全的機制,可以同步地對非同步復位取消斷言。使用復位橋接電路,每個時鐘域都需要全域性復位的區域性版本。

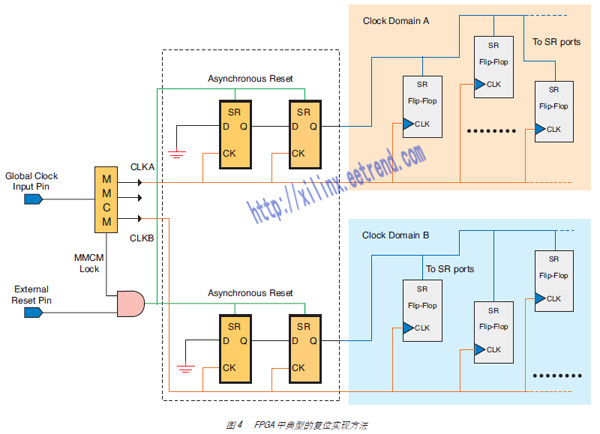

在圖 3 所示的電路中,假定為復位橋和相關邏輯提供時鐘訊號的時鐘 (clk_a) 是穩定且無誤的。在 FPGA 中,時鐘訊號可以直接來自片外的時鐘源(理想的情況下是通過有時鐘功能的引腳獲得),或者可以用 MMCM 或者鎖相環(PLL) 在內部生成。任何用於生成時鐘的MMCM 或者 PLL 在復位之後都需要進行校準。因此,可能需要在全域性復位路徑中插入額外的邏輯來穩定時鐘。

技巧3:在對 FPGA 的全域性復位取消斷言之前,確保由 MMCM 或PLL 生成的時鐘是穩定且被鎖定的

圖 4 是 FPGA 中典型的復位實現方法。

賽靈思暫存器的 SR 控制埠屬於高電平有效。如果 RTL 程式碼描述的是低電平有效的設定/重設/預設/清除功能,那麼綜合工具在驅動暫存器的控制埠之前,必須首先推斷出一個反相器。由於必須使用查詢表來完成反相操作,所以需要一個 LUT 輸入。這個因使用低電平有效的控制訊號而增加的邏輯可能導致執行時間延長,器件利用率下降。而且它還會給時序和功耗造成不利影響。

那麼底線是什麼呢?在 HDL 程式碼或者例項化元件中儘量使用高電平有效的控制訊號。在無法控制設計中控制訊號的極性的時候,應在程式碼的最頂層對訊號進行反相操作。用這種方法進行描述,推斷出的反相器可以併入 I/O 邏輯中,無需佔用額外的 FPGA 邏輯或者佈線。

技巧 4:高電平有效復位能夠實現更高的器件利用率,並可改善效能

值得注意的是,FPGA 不是一定需要全域性復位。全域性復位和設計中的其它線路一樣,要爭用相同的佈線資源。全域性復位一般具有高扇出,因為它需要擴充套件到設計中的每一個觸發器。這樣會消耗大量的佈線資源,對器件的利用率和時序效能造成不利影響。由此,有必要探索出不是建立在完整的全域性復位基礎之上的其它復位機制。

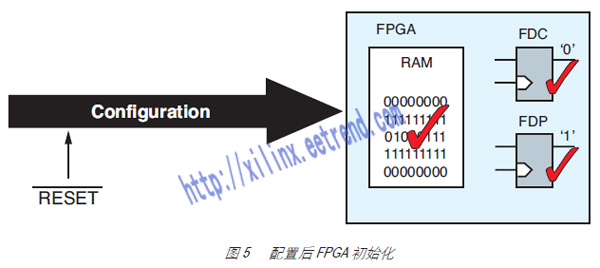

在配置或重配置賽靈思 FPGA時,每一個單元(包括觸發器和 block RAM)都需要進行初始化,如圖 5 所示。因此,FPGA 配置具有與全域性復位一樣的效果,因為它能將 FPGA中的每一個儲存元件的初始狀態都設定為已知狀態。

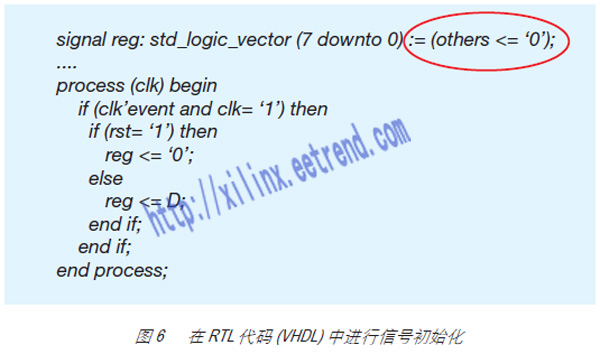

可以從 RTL 程式碼中推斷觸發器初始化值。圖 6 的示例說明了如何對 RTL中暫存器的初始化進行編碼。FPGA 工具能夠綜合這些訊號的初始化,儘管通常會誤以為做不到。底層 VHDL 訊號或者 Verilog 暫存器的初始化值會成為推斷出的觸發器的 INIT 值,這個值會在配置的過程中被載入到觸發器中。

使用暫存器還可以在配置過程中初始化 block RAM。隨著基於處理器的系統中嵌入式 RAM 數量的增多,BRAM初始化已經成為一項有用的功能。這是因為預先定義的 RAM 能夠簡化模擬設定,並且無需使用引導順序為嵌入式設計清空記憶體。

全域性置位/復位 (GSR) 訊號是一種特殊的預佈線復位訊號,能夠在 FPGA配置的過程中讓設計保持初始狀態。在配置完成後,GSR 會被釋放,所有的觸發器及其它資源都載入的是 INIT 值。除了在配置程序中執行 GSR,使用者設計還可以通過例項化 STARTUPE2 模組並連線到 GSR 埠的方法來訪問 GSR 網。使用該埠,設計可以重新斷言 GSR網,相應地 FPGA 中的所有儲存元件將返回到它們的 INIT 屬性所規定的狀態。

取消斷言 GSR 是非同步的,需要使用多個時鐘才能影響到設計中的所有觸發器。對於狀態機、計數器或者其它能夠自動改變狀態的邏輯,需要一個顯示的復位,用於同步取消使用者時鐘斷言。因次,使用 GSR 作為唯一的復位機制可能導致系統不可靠。

因此,最好是綜合採用多種方法來有效地管理啟動。

技巧 5:依靠 GSR 提供的內建初始化功能,同時對設計中能夠自動啟動的部分進行顯式復位,這種綜合法能夠帶來更高的利用率和效能。

在使用 GSR 設定整個設計的初始狀態之後,對需要同步復位的邏輯單元(比如狀態機)使用顯式復位。可使用標準的亞穩態解決電路或者復位橋來生成同步的顯式復位。

使用恰當的復位實現利用率的最大化

RTL 程式碼中使用的復位型別對工具將設計對映到 FPGA 底層資源的能力有重大影響。在編寫 RTL 程式碼的時候,設計人員應根據情況定製子設計的復位方式,以便工具能夠把設計對映到這些資源。

應注意的是,SRL、LUTRAM 和BRAM 中內容的初始化,只能用 GSR方法來完成,不能使用顯式復位。因此,在為以上這些資源編寫程式碼時,應注意避免在編碼中使用復位。例如,如果一段 RTL 程式碼描述的是一個 32 位移位暫存器,而且對移位暫存器的 32 個階進行顯式復位,那麼綜合工具將無法將這段 RTL 程式碼直接對映到 SRL32E上, 因為它無法滿足該資源的編碼復位要求。作為替代,該程式碼將圍繞SRL32E 推斷出 32 個觸發器,或推斷出一些其它電路,用以實現要求的復位功能。相對於不使用復位的 RTL 程式碼,這兩種解決方案都會佔用更多資源。

技巧 6:在對映到 SRL、LUTRAM或者 BRAM 時,不要為 SRL 或者RAM 陣列的復位進行編碼

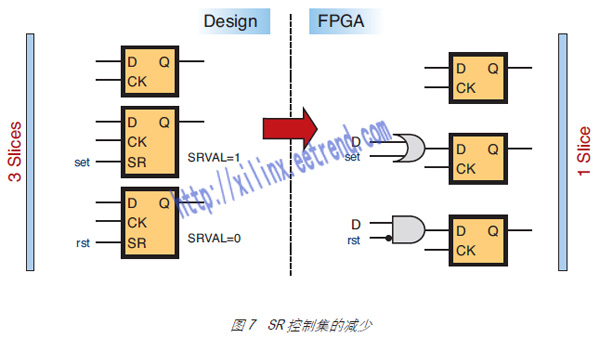

在 7 系列器件中,不能把具有不同控制訊號的觸發器打包到同一個 Slice中。對於低扇出復位,這樣會給 Slice的總體利用率造成不利影響。在同步復位的情況下,綜合工具可以使用 LUT(如圖 7 所示)來實現復位功能,而不是使用觸發器的控制埠,故而可將復位當作控制埠移除。這樣就可以把得到的 LUT/觸發器對與其它不使用其 SR埠的觸發器打包。這樣做的結果是LUT 使用率雖然會上升,但 Slice 的使用率可以得到改善。

技巧 7:同步復位能夠增強 FPGA利用率。在設計中應使用同步復位,而不是非同步復位

一些較大的專用資源(即 BRAM和 DSP48E1 單元)內含的暫存器可以被推斷為專用資源功能的組成部分。BRAM 包含可選的輸出暫存器,可利用該暫存器以及附加的時延時鐘來改善時鐘頻率。DSP48E1 有許多暫存器,既可以作為流水線來增加最大時鐘速度,也可作為週期時延 (Z-1)。但是這些暫存器只具備同步置位/復位功能。

技巧 8: 使用同步復位可以允許綜合工具使用 DSP48E1 Slice 或BRAM等專用資源內部的暫存器。這樣能夠改善設計中相應部分的器件總體使用率和效能,同時降低總體功耗。

如果 RTL 程式碼描述的是非同步置位/復位,那麼綜合工具就無法使用這些內部暫存器。作為替代,它將使用 Slice觸發器,因為它們能夠實現要求的非同步置位/復位功能。這樣不僅會導致器件利用率降低,還會給效能和功耗造成不利影響。

多種選擇

有多種復位方法可供 FPGA 選擇,每種都有自身的優勢和不足。這裡提出的建議有助於設計人員為自己的設計選擇最適合的復位結構。理想的復位結構能夠改善 FPGA 的器件使用率、時序和功耗。