《微機原理與介面技術》第二章——微機原理(8088)

雖然寫這個部落格主要目的是為了給我自己做一個思路記憶錄,但是如果你恰好點了進來,那麼先對你說一聲歡迎。我並不是什麼大觸,只是一個菜菜的學生,如果您發現了什麼錯誤或者您對於某些地方有更好的意見,非常歡迎您的斧正!

目錄

第一章重點回顧:

MOV AX,2000H; 將16位資料2000H傳送到AX暫存器

MOV AL,20H; 將8位資料20H傳送到AL暫存器

MOV AX,BX; 將BX暫存器的16位資料傳送到AX暫存器

MOV AL,[2000H]; 將2000H單元的內容傳送到AL暫存器

需要注意的是:

(1)兩個儲存單元之間不能直接傳送資料,即:MOV指令只允許一個運算元在儲存器中。MOV [SI],[2000H];這是錯誤的

(2)MOV指令中立即數不能直接傳送給段暫存器(CS、DS、SS、ES)和IP;段暫存器之間不能直接傳送。MOV IP,2000 H ;這是錯誤的

(3)CS和IP不能作為目的運算元。MOV CS,AX ;這是錯誤的

(4)MOV指令中立即數不能作目標運算元。MOV 2000H,[SI] ;這是錯誤的

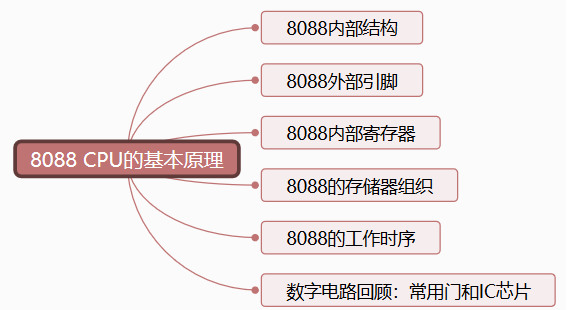

第一節 8088 CPU的基本原理

8086/8088 CPU的特點

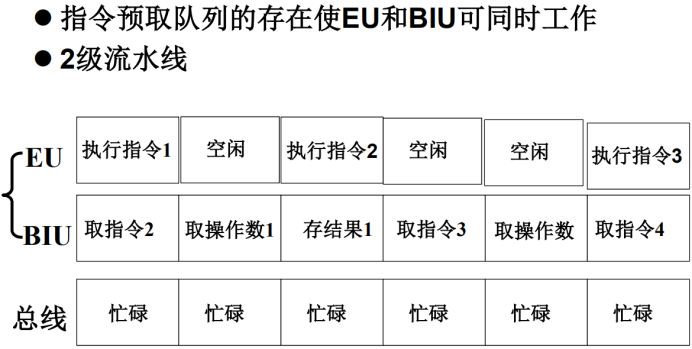

①採用並行流水線工作方式

②支援多處理器系統

③片內無浮點運算部件,浮點運算由數學協處理器8087支援

④對記憶體空間實行分段管理

|

|

|

8086 |

8088 |

| 相同點 |

暫存器 |

16位 |

|

|

|

地址線 |

20根,1MB記憶體 |

|

| 差異 |

資料匯流排 |

16根 |

8根 |

|

|

指令佇列 |

6位元組 |

4位元組 |

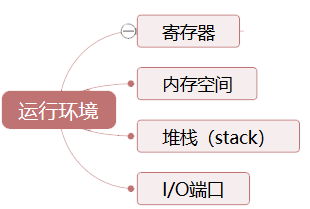

第二節 8088的執行(執行)環境

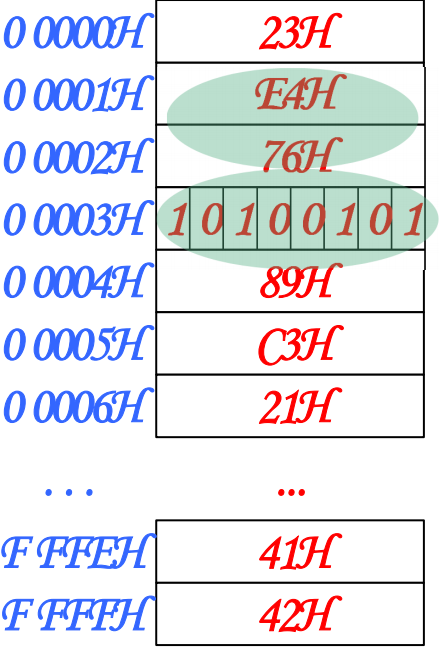

資料存放規律

①位元組資料

一單元存放一個數:E4H存放在00001H單元

②字資料:2單元

2單元:“低對低,高對高”

字的地址:2個單元中的低地址

例:76E4H存放在00001H中

③機器指令(機器碼):多個位元組

按位元組順序地址遞增存放

如:MOV BX,AX;89C3H ,4H單元

④字串:多個位元組

按位元組順序地址遞增存放,同機器指令

例題:00002H存放的位元組/字指令為多少?

位元組:E476H

字:76H

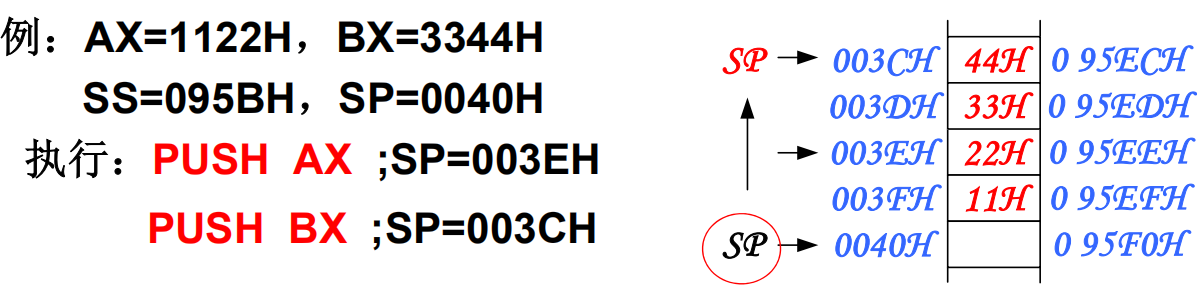

堆疊

呼叫發生後,主程式在CPU中的執行環境被破壞

呼叫返回時,必須恢復主程式之前的執行環境

在子程式呼叫和中斷服務時儲存引數和現場資料。

堆疊的伸展方向:棧底的地址大,棧頂的地址小。

棧的操作(PC):

入棧:將一個數存入棧頂,並改變SP(變小)

PUSH SRC;SRC代表暫存器或儲存單元地址

功能:將暫存器或儲存單元的一個字壓入堆疊

操作:“先減後入”:SP-1,字高位->[SP]

SP-1,字低位->[SP]

結果:SP-2,資料高對高,低對低存放。

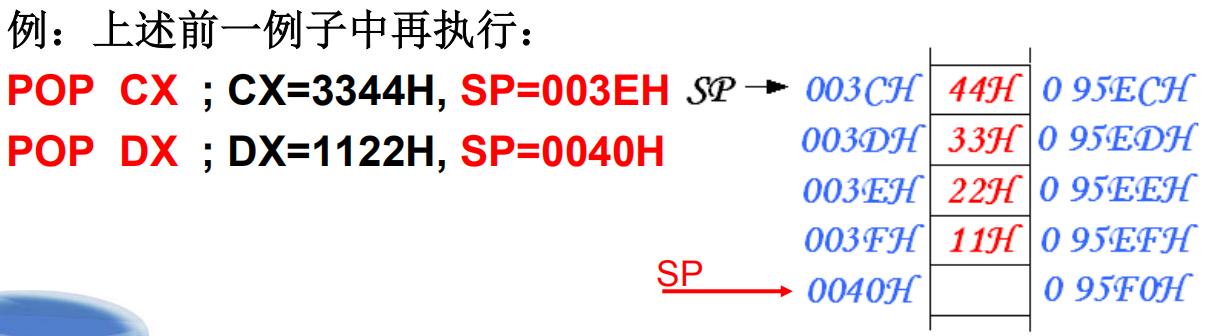

出棧:從棧頂讀出一個數據,並改變SP(變大)

POP DST;DST代表暫存器或儲存單元地址

功能:將棧頂的一個字傳送到暫存器或儲存單元地址中

操作:“先出後加”:[SP]->字低位,SP+1->SP

[SP]->字高位,SP+1->SP

結果:SP+2,資料低對低,高對高存放

Flag暫存器出/入棧

命令格式:

PUSH F;F入棧,SP-2 -> SP

POP F;F出棧,SP+2 -> SP

功能:保護和恢復狀態標誌暫存器Flag

注意:

①棧操作均以字為單位,如PUSH AL,POP DH 均錯。

②PUSH與POP成對,避免堆疊溢位或程式出錯。

③堆疊實為記憶體區,還可按資料區的方法對其操作。

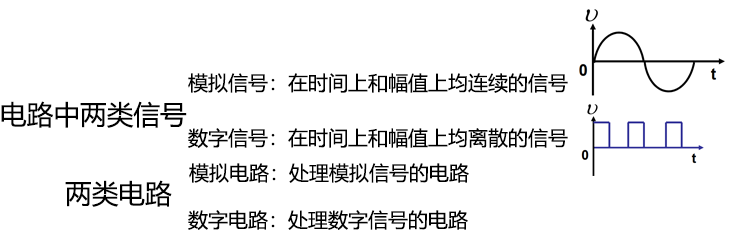

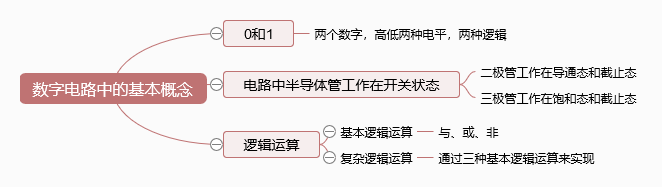

第3節 數位電路、常用門和IC晶片

複合邏輯運算:基本邏輯運算的複合

複合邏輯閘:實現複合邏輯運算的電路

與非門 或非門 異或門 同或門

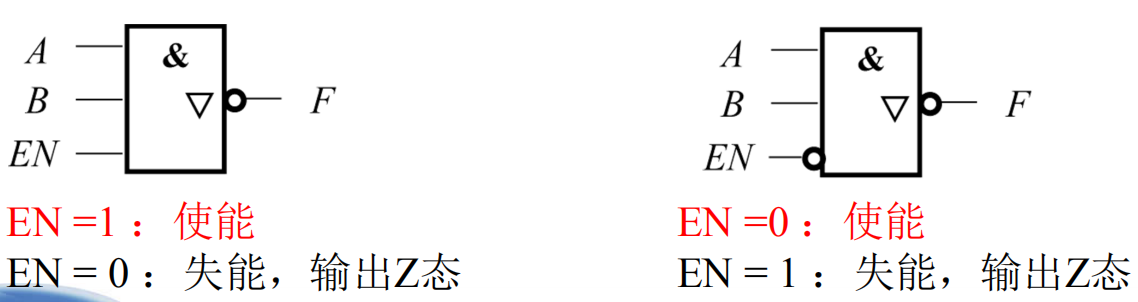

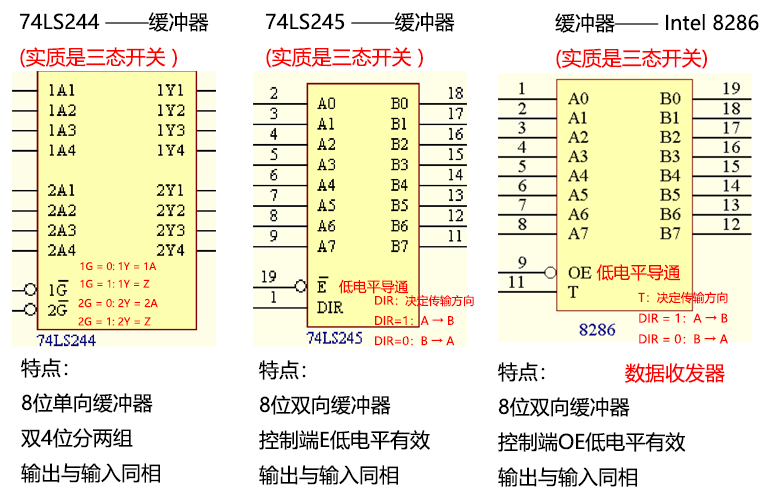

三態門(TS門,有▽符號):0、1、Z(高阻狀態或禁止態)

在普通門增加一個使能端(EN)

EN有效:門按原邏輯工作,輸出0或1

EN無效:門輸出Z(高阻態)

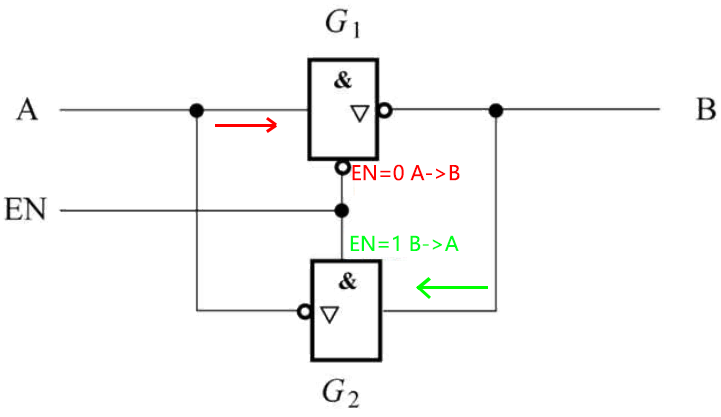

三態門的典型應用:

資料傳輸方向控制

匯流排存取控制

模擬開關

匯流排存取控制:多個裝置在資料匯流排上,必須控制存取許可權,任何時候只能讓最多1個裝置邏輯連線(佔用)匯流排。

| 觸發器 |

D觸發器 |

| 功能和特點 |

能儲存一位二進位制資訊的單元電路 |

|

|

用於訊號保持 |

|

|

用於導通開關 |

|

|

特點:0-1雙穩態電路 |

| 觸發器與門的聯絡 |

聯絡:觸發器是在閘電路的基礎上引入反饋構成的 |

|

|

門是組合電路,觸發器是時序電路 |

| 觸發器的種類 |

基本RS觸發器 |

|

|

同步RS觸發器 |

|

|

主從型JK觸發器 |

|

|

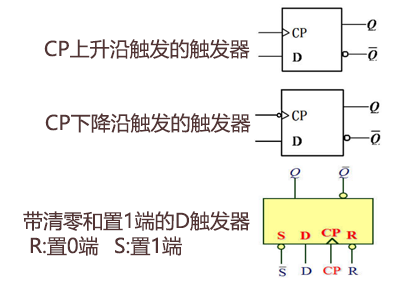

維持阻塞型D觸發器 |

|

|

T和T’觸發器 |

工作方式

CP上升沿 鎖存D(阻塞D),上升沿後Q端保持不變。

觸發器在CP脈衝的上升沿產生狀態變化:Q=D,而在上升沿後,D端訊號變化對觸發器輸出狀態沒有影響。觸發器的次態取決於CP脈衝上升沿時的D訊號。

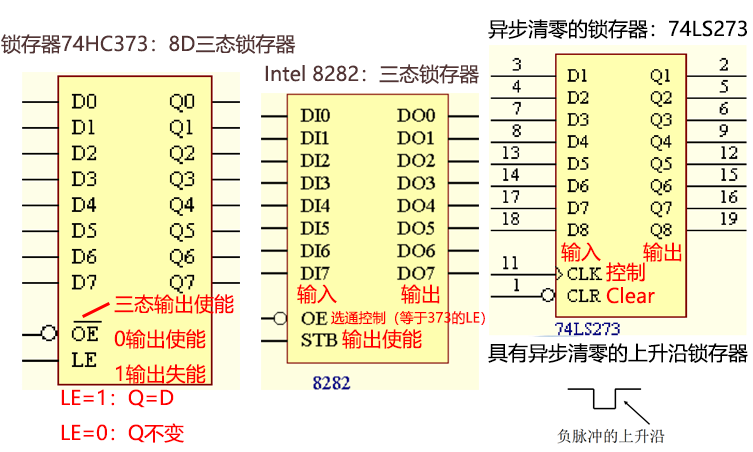

鎖存器

鎖存器和觸發器有類似的功能:

①具有0和1兩個穩狀,能自行保持

②能儲存一位二進位制碼

區別:鎖存器對電平敏感,觸發器對邊沿敏感。

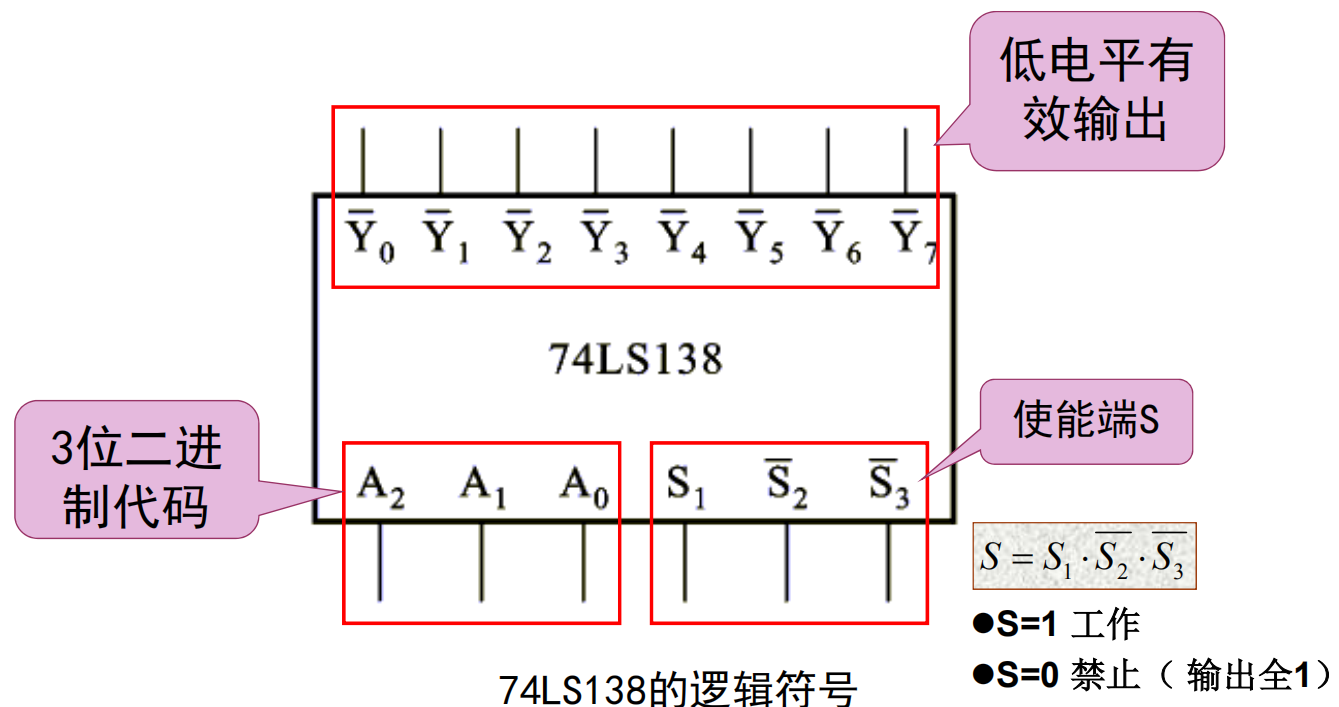

基本晶片——譯碼器

功能:將某個二進位制資料的含義“翻譯”出來,指示唯一的某1個事件有效。

結構:n位輸入腳,2^n個輸出腳(每腳對應1個事件)

特點:每次譯碼,僅唯一的1個輸出引腳為有效電平

3-8譯碼器

結構:3個輸入引腳,8個輸出引腳

功能:輸入3位二進位制程式碼A2A1A0(000~111),在唯一的某個輸出引腳上出現有效電平(低)

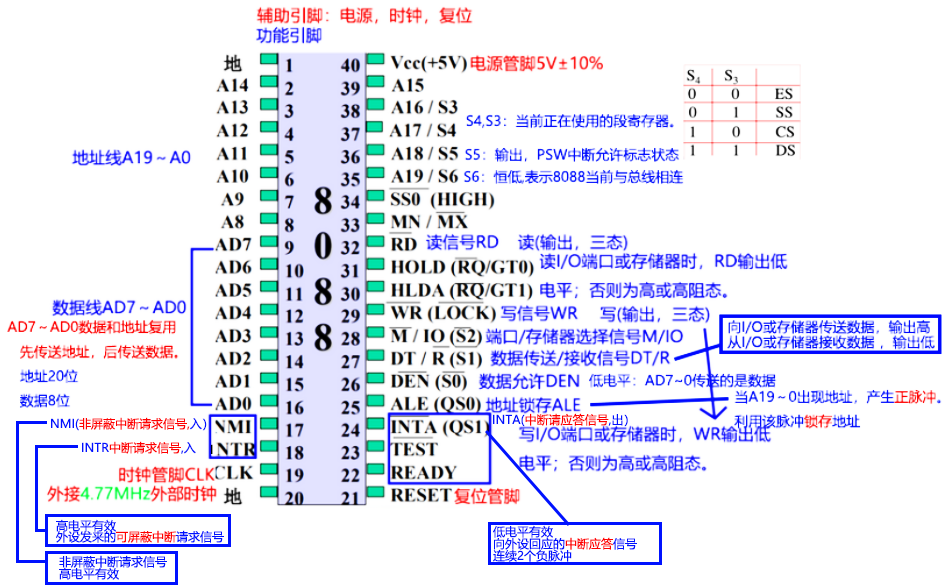

第4節 8088微處理的外部結構

(廢話:感覺學微機這門課真的很雲裡霧裡,唉。)

8088的電氣特性

電源:5V±10%的條件下能夠工作

輸入特性:

低電平:0.8V(0)

高電平:2.0V(1)

輸出特性:

低電平:0.45V(0)

高電平:2.4V(1)

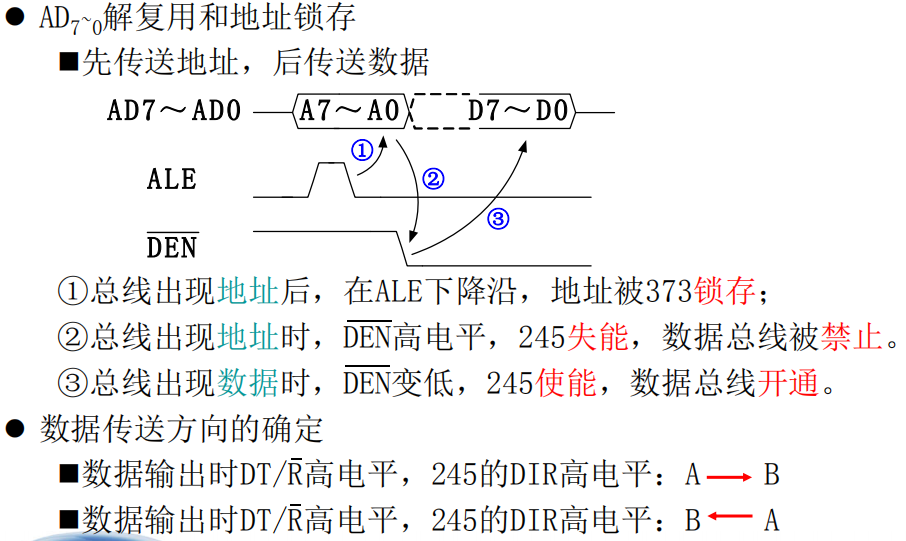

8088系統匯流排的形成

主要解決:

實現地址匯流排(AB),資料匯流排(DB)和控制匯流排(CB)

地址與資料的分離

地址鎖存

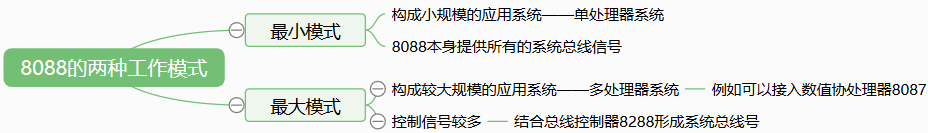

這兩種模式利用MN/MX(33號)引腳區別:

·MN/MX接高電平為最小模式

·MN/MX接低電平為最大模式

第5節 8088處理器時序和匯流排週期

時序(概念):訊號隨時間和事件變化的順序或規律

可用時序描述CPU通過匯流排對外實施的各種操作(匯流排操作):

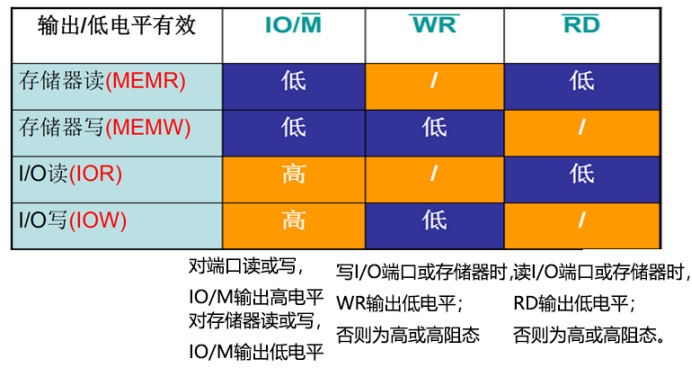

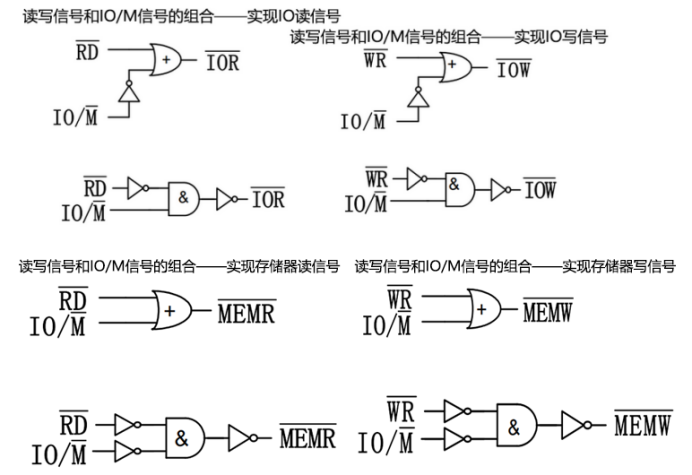

儲存器讀操作 I/O讀操作

儲存器寫操作 I/O寫操作

中斷響應操作 匯流排請求及響應操作

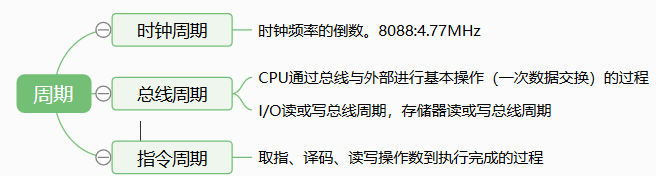

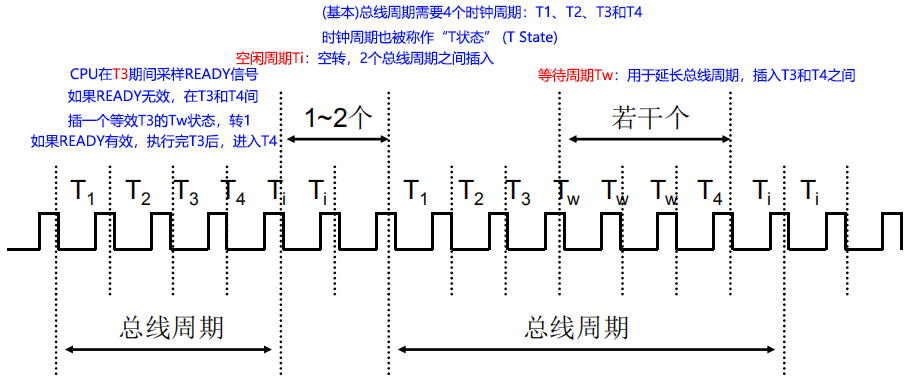

指令週期 > 匯流排週期 > 時鐘週期

匯流排週期(即匯流排操作)產生的例子

指令取指階段:儲存器讀匯流排週期(讀取指令程式碼)

源運算元是儲存單元的指令:儲存器讀匯流排週期

目的運算元是儲存單元的指令:儲存器寫匯流排週期

執行IN指令:I/O讀匯流排週期

執行OUT指令:I/O寫匯流排週期

CPU響應可遮蔽中斷:中斷響應匯流排週期

空閒匯流排週期

CPU不執行任何儲存單元或I/O操作,則執行空閒周Ti(Idle)

基本的匯流排週期:

儲存器讀 儲存器寫 I/O埠讀 I/O埠寫 中斷響應

第6節 IA-32發展歷史

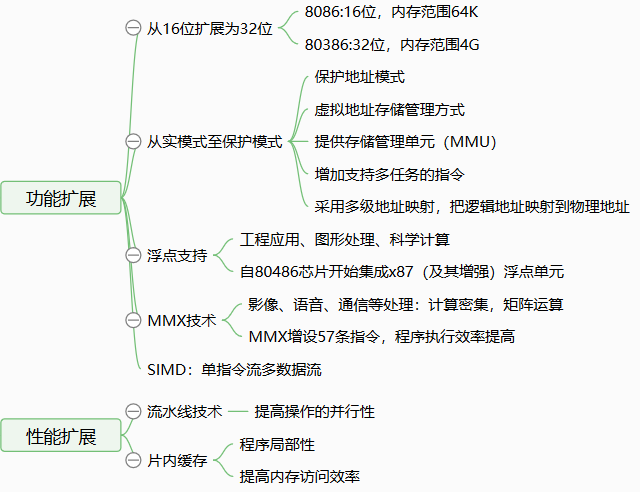

IA-32微處理器是8086/8088的延伸