第四章 分頁儲存管理方式

一,儲存管理的離散分配方式

基本分頁儲存管理

基本分段儲存管理

段頁式儲存管理

二,基本分頁儲存管理

離散分配記憶體:

作業規定大小劃分成小份;記憶體也按同樣大小劃分成小份 作業的任一小份可分散放入記憶體任意未使用的小份

1)頁面的概念

記憶體劃分成多個小單元,每個單元K大小,稱(物理)塊。作業也按K單位大小劃分成片,稱為頁面。

物理劃分塊的大小 = 邏輯劃分的頁的大小

頁面大小要適中。 太大,(最後一頁)內碎片增大,類似連續分配的問題。 太小的話,頁面碎片總空間雖然小,提高了利用率,但每個程序的頁面數量較多,頁表過長,反而又增加了空間使用。

2)頁表的概念

為了找到被離散分配到記憶體中的作業,記錄每個作業各頁對映到哪個物理塊,形成的頁面對映表,簡稱頁表。

每個作業有自己的頁表

頁表的作用:頁號到物理塊號的地址對映 要找到作業A 關鍵是找到頁表(頁表地址儲存在PCB,頁表儲存在記憶體) 根據頁表找物理塊

3)地址的處理

連續方式下,每條指令用基地址+偏移量即可找到其物理存放的地址。

規律:

作業相對地址在分頁下不同位置的數有一定的意義結構:

頁號+頁內地址(即頁內偏移)

關鍵的計算是:根據系統頁面大小找到不同意義二進位制位的分界線。

從地址中分析出頁號後,地址對映只需要把頁號改為對應物理塊號,偏移不變,即可找到記憶體中實際位置。

4)地址變換機構

地址變換過程

分頁系統中,程序建立,放入記憶體,構建頁表,在PCB中記錄頁表存放在記憶體的首地址及頁表長度。 執行某程序A時,將A程序PCB中的頁表資訊寫入PTR中; 每執行一條指令時,根據分頁計算原理,得到指令頁號X和內部偏移量Y; CPU高速訪問PTR找到頁表在哪裡; 查頁表資料,得到X實際對應存放的物理塊,完成地址對映計算,最終在記憶體找到該指令。

5)快表

問題:基本分頁機制下,一次指令需兩次記憶體訪問,處理機速度降低1/2,分頁空間效率的提高以如此的速度為代價,得不償失。 改進:減少第1步訪問記憶體的時間。增設一個具有“並行查詢”能力的高速緩衝暫存器,稱為“快表”,也稱“聯想暫存器”(Associative memory),IBM系統稱為TLB(Translation Look aside Buffer)。

快表放什麼?: 正在執行程序的頁表的資料項。

快表的暫存器單元數量是有限的,不能裝下一個程序的所有頁表項。雖不能完全避免兩次訪問記憶體,但如果命中率a高還是能大幅度提高速度。

設一次查詢訪問快表時間為t' ,則 EAT= a*t' + (1-a)(t'+t) + t

= 2t +t' -t*a

6)兩級、多級頁表

引入原因:程序分頁離散存放,但頁表的資料是連續在存放記憶體的。而頁表可能很大

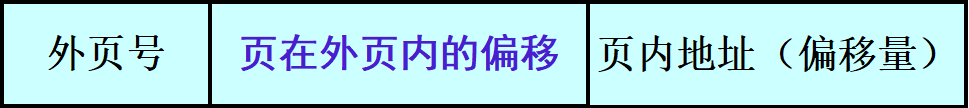

①兩級頁表

將頁表分頁,並離散地將頁表的各個頁面分別存放在不同的物理塊中

為離散分配的頁表再建立一張頁表,稱為“外層頁表”,其每個表項記錄了頁表頁面所在的物理塊號。

②多級頁表

64位作業系統下,兩級仍然不足以解決頁表過大問題時,可按同樣道理繼續分頁下去形成多級頁表。

三.基本分段儲存管理方式

1)分段系統的基本原理

程式通過分段(segmentation)劃分為多個模組,每個段定義一組邏輯資訊。如程式碼段(主程式段main,子程式段X)、資料段D、棧段S等。

段的特點:

每段有自己的名字(一般用段號做名),都從0編址,可分別編寫和編譯。裝入記憶體時,每段賦予各段一個段號。

每段佔據一塊連續的記憶體。(即有離散的分段,又有連續的記憶體使用)

各段大小不等。

地址結構:段號 + 段內地址

2)段表與地址變換機構

段是連續存放在記憶體中。段表中針對每個“段編號”記錄:“記憶體首地址”和“段長”

3)分頁和分段的主要區別

(1)需求:分頁是出於系統管理的需要,是一種資訊的物理劃分單位,分段是出於使用者應用的需要,是一種邏輯單位,通常包含一組意義相對完整的資訊。

(2)大小:頁大小是系統固定的,而段大小則通常不固定。分段沒有內碎片,但連續存放段產生外碎片,可以通過記憶體緊縮來消除。相對而言分頁空間利用率高。

(3)邏輯地址:

分頁是一維的,各個模組在連結時必須組織成同一個地址空間;

分段是二維的,各個模組在連結時可以每個段組織成一個地址空間。

(4)其他:通常段比頁大,因而段表比頁表短,可以縮短查詢時間,提高訪問速度。分段模式下,還可針對不同型別採取不同的保護;按段為單位來進行共享

4)資訊共享

分段系統的突出優點:

(1)易於實現共享 :在分段系統中,實現共享十分容易,只需在每個程序的段表中為共享程式設定一個段表項。 比較課本圖。對同樣的共享內容的管理上,很明顯分段的空間管理更簡單。分頁的圖涉及太多的頁面劃分和地址記錄的管理。

(2)易於實現保護: 程式碼的保護和其邏輯意義有關,分頁的機械式劃分不容易實現。