【高速介面-RapidIO】3、RapidIO序列物理層的包傳輸過程

一、引言

前幾篇文章已經談到RapidIO的協議,序列物理層與控制符號。

RapidIO協議包括都事務(NREAD),寫事務(NWRITE),流寫事務(SWRITE),有響應的寫事務(NWRITE_R),原子操作(ATOMIC),維護操作(MAINTENANCE),門鈴事務(DOORBELL)和訊息(MESSAGE)這幾種。

RapidIO的序列物理層是基於SERDES的,關於SERDES涉及的一些相關技術請閱讀《SERDES關鍵技術總結》(連結:https://www.cnblogs.com/liujinggang/p/9998234.html)這篇文章。SERDES分為PCS(物理編碼子層)和PMA(物理媒介附屬子層)兩層,其中PCS是由純數位電路組成,可以用軟邏輯來實現,而PMA則既包括了數位電路,也包括了類比電路,不能用純邏輯實現。

控制符號是被序列鏈路埠所使用的訊息單元,它用來管理序列鏈路操作的各個功能,包括鏈路維護,包界定,包應答,錯誤報告和錯誤恢復等。

有了前面的基礎以後,接下來就談一談RapidIO序列物理層包的傳輸過程。

二、序列物理層的PCS層與PMA層

物理編碼子層(PCS)與物理媒介附屬子層(PMA)提供SERDES能夠進行高速序列資料傳輸的基本功能(術語PCS和PMA出自IEEE 802.3 )。主要包括8B/10B編碼、字元表示法、資料流的分段、碼組(Code Group)、縱列(Column)、鏈路傳輸規則、空閒序列(Idle Sequence)和鏈路初始化。

通道的概念用於描述序列RapidIO端點的寬度。通道定義為每個方向上的單向差分對。目前序列RapidIO規定了兩種鏈路寬度: 1x鏈路為1通道鏈路, 4x鏈路為4通道鏈路。更寬的鏈路也是可能的, 但是目前還沒有知定。

下圖展示了一個典型的RapidIO端點的結構。框圖的上部是負責產生大量RapidIO包的邏輯層和傳輸層。在這些層下面緊接著的是序列協議層,該層負責產生和處理控制符號並通過鏈路管理協議管理鏈路。序列協議層下面是PCS層。鏈路協議管理層和PCS層之間的邊界通常也是時鐘從器件內部時鐘轉變為 RapidIO端點本身時鐘的轉變邊界。PCS層負責通道分段(Striping),產生空閒序列並把字元轉換為相應的8B/10B編碼的K碼和D碼。PCS層下面是PMA層,該層負責與電氣層的銜接。PMA層還負責確保不同通道間彼此正確對齊。電氣層代表不同器件、接收器及其之間的電氣連線。

2.1 PCS層的功能

物理編碼子層(PCS)的功能是負責產生空閒序列、通道分段、傳送編碼、解碼、通道對齊和在接收時將分段合併。PCS使用8B/10B編碼在整個鏈路上傳送資料。8B/10B編碼方案最初由IBM開發,並在工業界廣泛用於將資料和時鐘資訊合併為一個單獨的訊號。

PCS層還提供了判定埠的操作模式是4通道還是1通道的機制和檢驗鏈路狀態的方法。該層容許在傳送者和接收者之間存在時鐘差異而無需流量控制。

PCS層執行下列傳送功能:

1、 將在佇列中等待發送的包和定界控制符號提取出來組成字元流。

2、 在可用通道上分段傳送字元流。

3、 當沒有待發送的包和定界控制符號時,產生空閒序列並將其插入到每個通道傳送的字元流中。

4、 將每個通道的字元流獨立編碼為10位並行碼組。

5、 將形成的10位並行碼組傳遞給PMA層。

PCS層執行下列接收功能:

1、 解碼10位並行碼組的接收流為各通道獨立的符號。

2、 將從無效碼組解碼得到的字元標記為無效。

3、 如果鏈路使用多於一個的通道,對齊字元流來消除通道間的偏移並將每個通道上的字元流重新組裝為一個單獨的字元流。

4、 將解碼字元流得到的包和定界控制符號遞送到更高層。

2.2 PMA層的功能

物理介質附屬層(PMA)的功能是逐通道將10位並行碼組序列化為序列位元流,或將序列位元流轉換為10位並行碼組。在接收資料時, PMA層的功能是將接收到的位元流逐通道分別對齊到10位碼組邊界。接著該層向PCS層的每個通道提供一個連續的碼組流。10位碼組對PCS層以上的各層是不可見的。

2.3 術語定義

在討論PCS和PMA層時使用的術語定義如下:

1、位元組(Byte): 一個8位資訊単元,位元組中每位的值為0或1。

2、字元(Character):由資訊位元組和一個控制位組成的9位實體。控制位指示資訊位元組包含的是資料還是控制資訊。控制位的值為D或K,分別指示資訊位元組包含資料或控制資訊。

3、D字元(D- Character):控制位為D的字元,也稱為資料字元。

4、K字元(K- Character):控制位為K的字元,也稱為特殊字元。

5、碼組(Code-group):對字元進行8B/10B編碼得到的10位實體。

6、縱列(Column):同時在4x(4通道)鏈路上傳送的由4個字元組成的組群。

7、Comma:8B/10B特殊碼組中唯一的只包含7個位元的字元,接收者用它來判定碼組邊界。

8、空閒序列(Idle Sequence):當不傳送包或者控制符號時傳送的字元(編碼後的碼組) 序列,空閒序列允許收發雙方保持同步,並保證在包之間、控制符號之間以及包與控制符號之間的碼組對齊。

9、通道對齊(Lane Alignment):消除4通道序列鏈路通道間偏移的過程。由傳送者以縱列(Column)傳送的字行由接收者的對齊過程以縱列輸出。若無通道對齊,以縱列傳送的字元可能會被分散到由接收者輸出的若干縱列上。對齊過程使用作為空閒序列的一部分傳送的特殊對齊字元。

10、分段(Striping): 4x鏈路上使用的在4個通道上同時傳送資料的方法。它將字元流逐字元分散到多個通道上。第1到第4個字元經分段處理後被分別分配到通道0到通道3上,第5個字元被迴圈分配到通道0上,以此類推。

2.3 8B/10B傳輸碼

PCS在傳送資料時使用8B/10B傳送碼將9位字元(8位資訊和1位控制位)編碼為10位碼組,接收資料時則進行相反的操作。256個數據字元和12個特殊(控制)字元被定義了編碼。

8B/10B碼使用的碼組中,“0”和“1”的個數相等(平衡)或相差2(不平衡)。如此選擇碼組保證了在每一碼組中至少存在兩次跳變,即0到1或1到0,使維持平衡的任務變得簡單。字元被編碼為一個單獨的平衡碼組或一對不平衡碼組。碼組對的成員在邏輯上與對方互補。這允許編碼器在選擇非平衡碼組時,根據維持編碼器輸出碼組流的0/1平衡所需的碼組選擇一個含“1”較多或含“0”較多的非平衡碼組。

8B/10B編碼有如下特性:

1、充足的位跳變密度(每個碼組有3~8個跳變),以允許接收端進行時鐘恢復。

2、使用特殊碼組建立接收者對10位碼組邊界的同步,定界控制符號並維持接收者位和碼組的邊界同步。

3、直流平衡(“0”和“1”的個數基本相同)。

4、可檢測某些單位元或多位元錯誤。

2.4 字元和碼組記號

8B/10B編碼和解碼使用下列記號描述字元、碼組和它們的位。

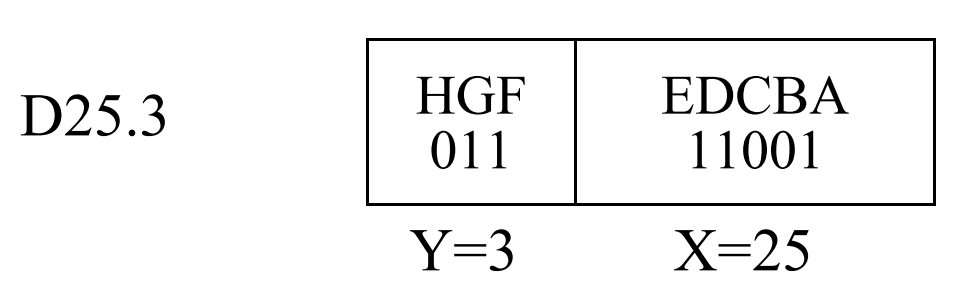

未編碼字元的資訊位[0-7]由字母A到H標記,H標記的是最高資訊位(RapidIO第0位),A標記的是最低資訊位(RapidIO第7位)。如下圖所示

每個資料字元都有一個Dx.y格式的表示法,其中x是最低5個資訊位EDCBA的十進位制值,y是最高3個資訊位HGF的十進位制值。同時,每個特殊字元也都有一個與之類似的Kx.y格式的表示法。

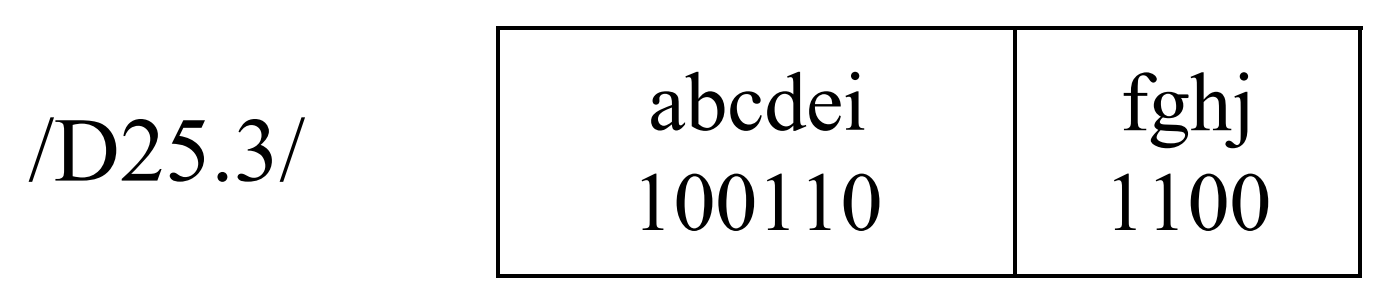

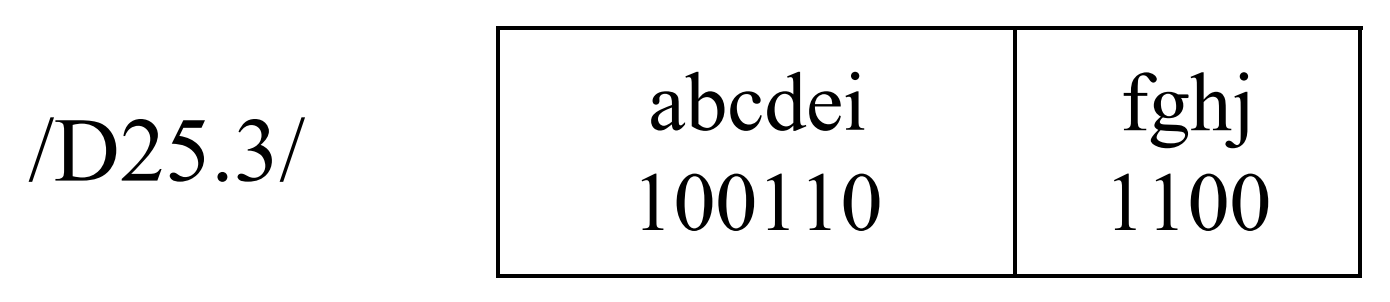

8B/10B編碼過程輸出的是10位碼組,用字母a到j標記碼組的位。碼組的位具有相等的重要性,沒有最高位或最低位。碼組位的次序如下圖所示

與資料字元Dx.y(8-bit)對應的碼組由/Dx.y/(10-bit)表示,與特殊字元Kx.y(8-bit)對應的碼組由/Kx.y/(10-bit)表示。

2.5 執行不一致(Running Disparity)

8B/10B編碼和解碼功能使用一個稱為執行不一致的二進位制變數。該變數值可為正(RD+)或負(RD-)。每個通道的編碼器和解碼器都有一個執行不一致變數。對於4x鏈路,各通道執行不一致的值相互獨立。

在編碼過程中執行不一致的主要用途是跟蹤解碼器是否輸出了較多的1或較多的0。當字元編碼需要從兩個不平衡的碼組中選擇一個碼組時,使用編輯器當前的執行不一致選擇採用哪一個不平衡碼組。

在上電後和埠可操作前,傳送者(編碼器)和接收者(解碼器)都必須建立執行不一致的當前值。傳送者使用負值作為每個通道執行不一致的初始值。接收者可能使用負值或正值作為每個通道的執行不一致變數的初始值。

使用下列演算法計算各通道的執行不一致值。在編碼器中,該演算法對由編碼器產生的新碼組進行操作。在接收方,該演算法對接收到的由解碼器解碼的新碼組進行操作。

每個碼組被分為兩個子塊,如下圖所示,前6位(abcdei)形成一個子塊(6位子塊),其餘4位(fghi)形成另一個子塊(4位子塊)。6位子塊頭部的執行不一致值是前一個碼組尾部的執行不一致值。4位子塊頭部的執行不一致值是6位子塊尾部的執行不一致值。碼組末尾的執行不一致值是4位子塊尾部的執行不一致值。

子塊執行不一致值的計算方法如下:

1、如果子塊包含“1”的個數多於“0”的個數,那麼任何子塊尾部的執行不一致值都是正的。如果4位子塊值為0b0011,其尾部的執行不一致值也是正的。如果6位子塊值為0b000111,其尾部的執行不一致值也是正的。

2、如果子塊包含“0”的個數多於“1”的個數,那麼在任何子塊尾部的執行不一致值都是負的。如果4位子塊值為0b1100。其尾部的執行不一致值也是負的。如果6位子塊值為0b111000,其尾部的執行不一致值也是負的。

3、在其他任何情況下,子塊尾部的執行不一致值總是與子塊頭部的執行不一致值相同。

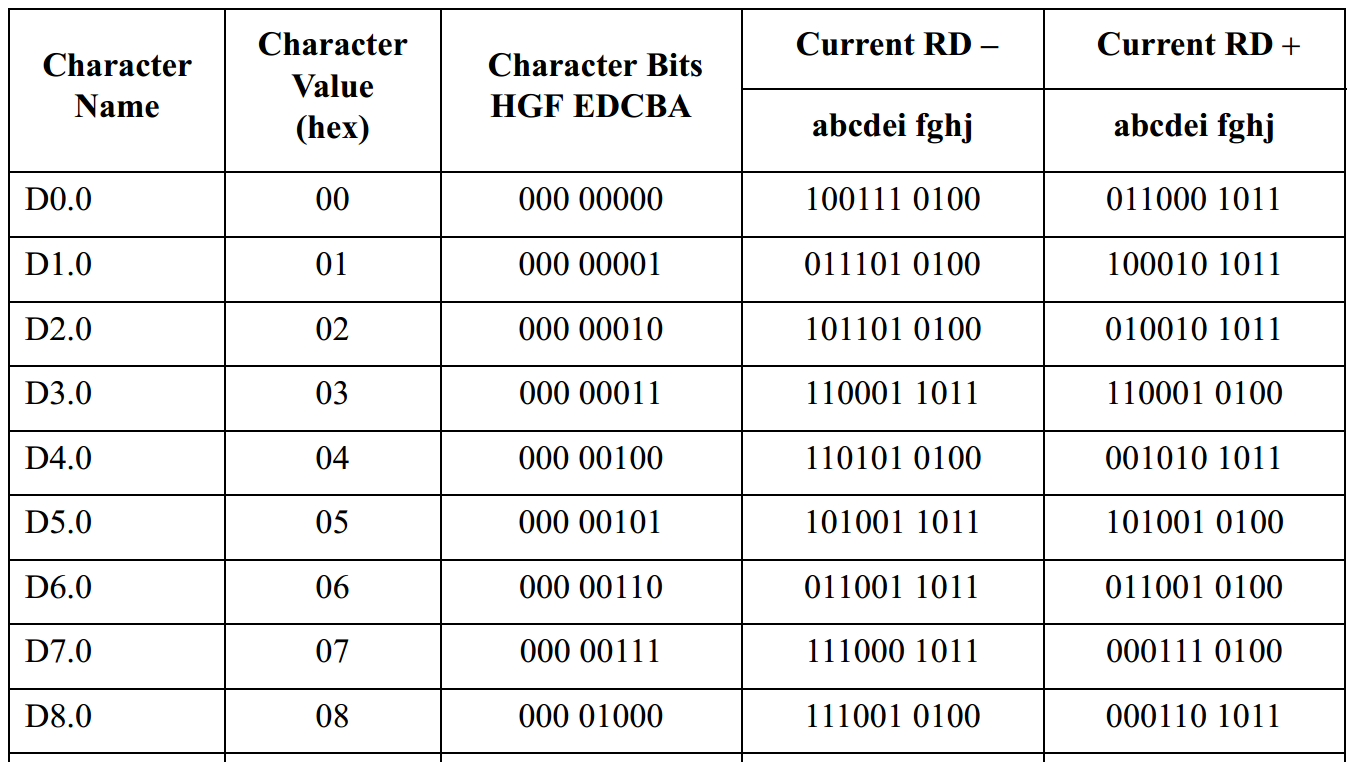

2.6 8B/10B編碼

8B/10B編碼功能將9位字元編碼為10位碼組。RapidIO規範包含256個數據字元(Dx.y)和12個特殊字特(Kx.y)的編碼。這些編碼幾乎完全基於IEEE 802.3工作組在10G位乙太網(XAUI)適配介面標準中定義的編碼。對任意給定的一個9位字元,有兩列編碼,一列記為RD-(負執行不一致),另一列記為RD+(正執行不一致)。對字元編碼時,如果當前編碼器的執行不一致值為負,就選擇RD-列中的碼組作為編碼結果;如果當前編碼器的執行不一致值為正,就選擇RD+列中的碼組作為編碼結果。在每個字元經編碼後,編碼器應當跟據執行不一致規則使用編碼得到的新碼組更新執行不一致值。 .

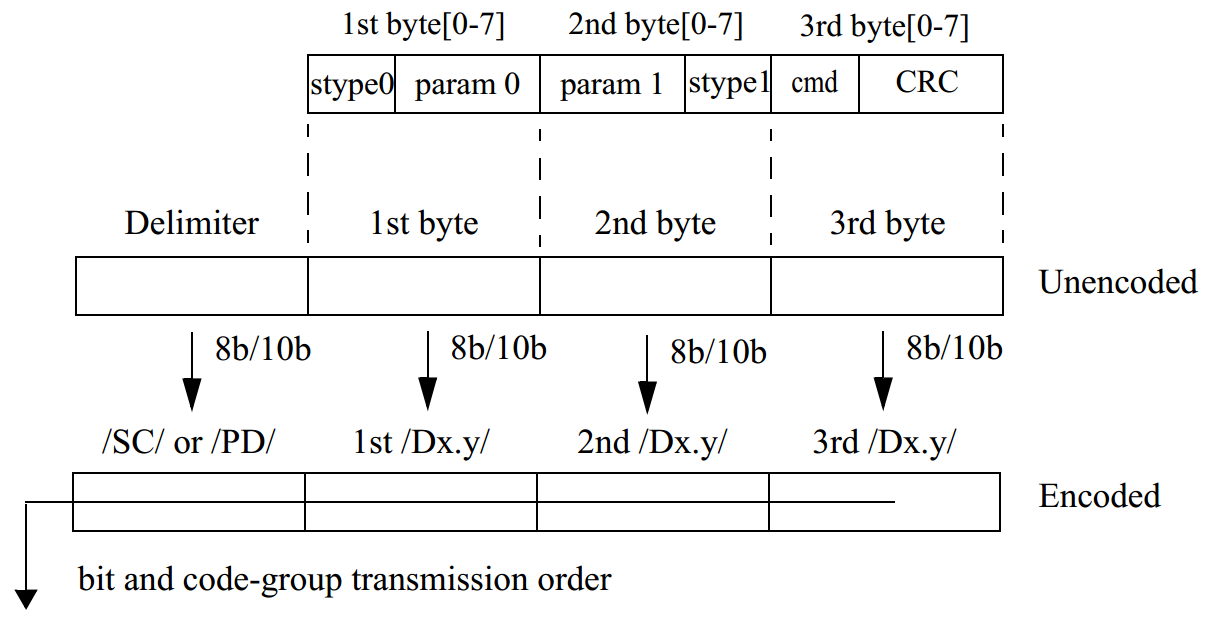

2.7 傳送順序

編碼器輸出的10位並行碼組經序列化,以“abcdeifghj”的位次序傳送,其中“a”位首先發送。如下圖所示,該圖給出了一個字元經過編碼、並串轉換、傳送、串並轉換和解碼的完整過程。圖的左邊顯示的傳送過程是使用8B/10B編碼對字元流編碼和10位並串轉換過程。右邊顯示的是接收者對接收到的碼組進行串並轉換和8B/10B解碼的過程。點劃線是產生10位碼組的PCS層和序列化碼組的PMA層的功能分界線。

下圖還顯示了在接收方接收者使用包含Comma序列的特殊字元來建立10位碼組的邊界對齊。

2.8 8B/10B解碼

8B/10B解碼功能將接收到的10位碼組解碼為9位字元,檢測接收到的未定義解碼的碼組並標記解碼輸出流中得到的相應字元為無效字元(INVALID)。

解碼功能使用與8B/10B編碼相反的解碼錶和解碼器當前的執行不一致值。解碼器將接收到的碼組與兩個表選擇的列中的碼組做比較。如果找到匹配,碼組就被解碼為相應字元;如果找不到匹配,碼組就被解碼為一個以某種方式標記為無效的字元。在解碼每個碼組後,解碼器接著應根據執行不一致規則使用解碼得到的新碼組更新解碼器的執行不一致值。

下表是一部分資料字元(Dx.y)的解碼錶,完整的解碼錶請檢視參考文獻1的492頁到499頁

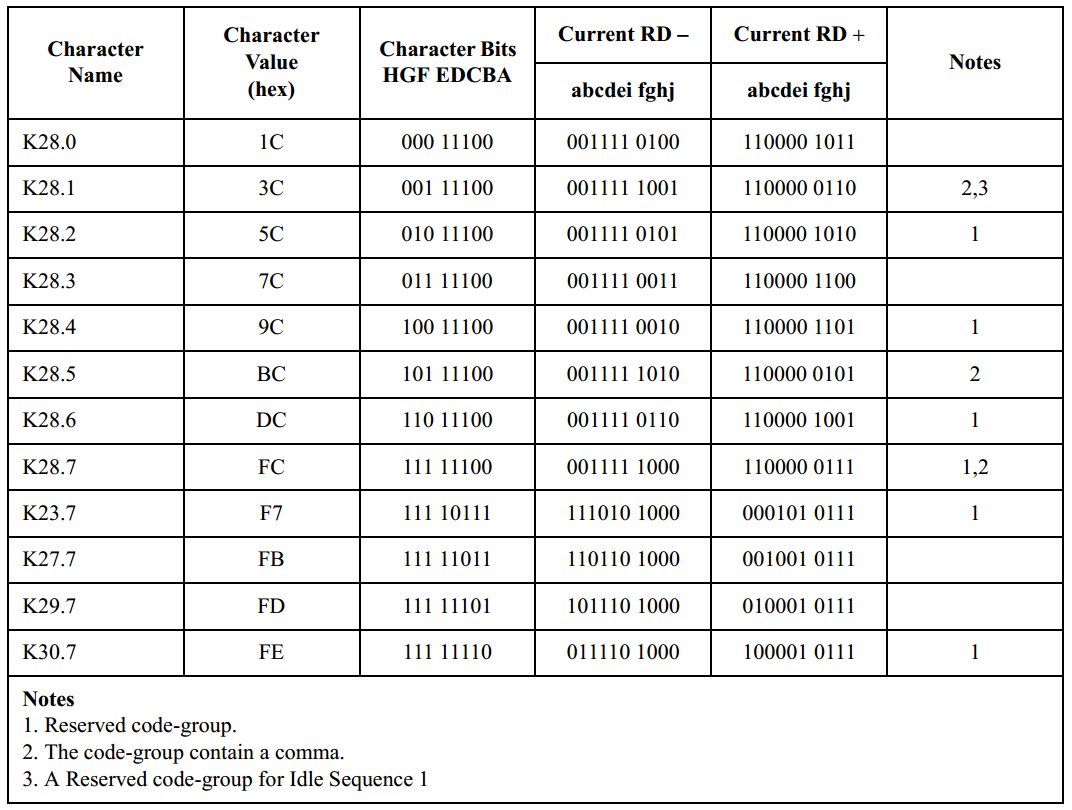

下表是12個特殊字元(Kx.y)的解碼錶

Comma是8B/10B編解碼中非常重要的一個單元,它只有7個bit,接收鏈路可以利用Comma實現碼組的邊界對齊。8B/10B中一共定義了兩種Comma,分別為0b0011111(Comma+)和0b1100000(Comma-)。這兩組Comma分別對應特殊碼組/K28.1/,/K28.5/和/K28.7/的abcdeif位。當碼組轉化完畢以後,在沒有傳輸錯誤發生的情況下,Comma不可能出現在碼組中的任何位置,也不可能在兩個相鄰碼組的邊界產生,但下面一種情況例外:

當特殊碼組/K28.7/後面傳輸的資料碼組是/D3.y/,/D11.y/,/D12.y/,/D19.y/,/D20.y/,/D28.y/和/K28.y/(y的取值範圍是0~7的整數)中的任意一個時,有可能導致comma在兩個碼組的邊界產生(取決於執行不一致的值)。如果在兩個碼組的邊界產生了comma,那麼接收鏈路就有可能改變10-bit碼組的對齊位置。因此,特殊碼組/K28.7/僅僅用作測試或者診斷的目的。

2.9 特殊字元與縱列

下表定義了RapidIO序列物理層中的特殊字元與縱列,使用特殊字元可以完成以下功能:

1、 逐通道對齊碼組(10位)邊界。

2、 對齊通過四個通道的接收資料流

3、 標記IDLE2 Sequence 中CS域的起始位置(CS = Command and Status)

4、 接收者和傳送者間的時鐘速率補償

5、 控制符號界定

下面對上表中的各個特殊字元與碼組的功能進行分別說明:

包分界控制符號(/PD/):

PD和/PD/分別是K28.3字元和/K28.3/碼組的別名,用於定界包含包定界符的控制符號的開始

控制符號的開始(/SC/):

SC和/SC/分別是K28.0字元和/K28.0/碼組的別名,用於定界不包含包定界符的控制符號的開始

同步(/K/):

K和/K/分別是K28.5字元和/K28.5/碼組的別名,空閒序列使用該字元或碼組向接收者提供接收者需要獲得並維持的位和10位碼組的邊界同步資訊。選用/K28.5/碼組作為同步字元的原因如下:

1、 該碼組的“abcdeif”位中包含Comma序列。Comma序列可在碼組位元流中輕易找到並標記碼組邊界

2、 “ghj”位提供了最大數量的位跳變(即101或010)

略過(/R/)

R和/R/分別是K29.7字元和/K29.7/碼組的別名。它們在空閒序列和時鐘補償序列中使用

對齊(/A/)

A和/A/分別是K27.7字元和/K27.7/碼組的別名。它們在空閒序列中使用並用於對齊4x通道。

標記(/M/)

M和/M/分別是K28.1字元和/K28.1/碼組的別名。它們在空閒序列2(Idle Sequence 2)中使用並給接收鏈路提供保持10位碼組邊界同步的資訊,同時標記空閒幀中CS域的位置。

||K||,||R||,||A||,||M||,||I||

||K||,||R||,||A||,||M||,||I||分別代表四通道情況下的特殊字元,含義與上面對應的字元含義相同。

三、使用序列物理層

瞭解組成序列物理層包頭的位、用於管理埠間通訊的控制符號和使用8B/10B編碼在同一訊號中傳送時鐘和DC平衡資料的位元流編碼技術後,現在我們可以研究鏈路在兩個端點間傳送資料的實際工作機制了。

3.1 埠初始化過程

埠初始化是RapidIO用來初始化和同步一對通訊埠的過程。這個過程包括檢測鏈路的另一端是否存在一個鏈路物件、建立位同步並對齊碼組邊界以及在埠能同時支援1x和4x模式(1x/4x埠)情況下,發現鏈路物件是否能支援4x操作模式並選擇1x或4x操作模式,如果選擇1x模式,則選擇通道0或者通道2作為鏈路接收通道。

若干狀態機控制了初始化過程。RapidIO規範詳細的描述了狀態機的結構。狀態機的數量和型別取決於埠僅支援1x模式(1x埠)還是同時支援1x和4x模式(1x/4x埠)。在兩種情況下都有一個主狀態機和一個或多個次狀態機。使用多個狀態機使整體設計更為簡化。正如可以預期的那樣,1x埠的初始化過程比1x/4x埠的初始化過程簡單;1x埠的初始化過程使1x/4x埠初始化過程的子集。

3.2 包交換協議

一旦埠初始化完成,就可以開始包的交換。已經定義了一個協議用於兩個序列RapidIO端點之間的包通訊。使用控制符號管理通過鏈路的包流。包由控制符號定界和確認。錯誤情況也可以通過控制符號通訊。控制符號還用於支援流量控制協議。

控制符號:

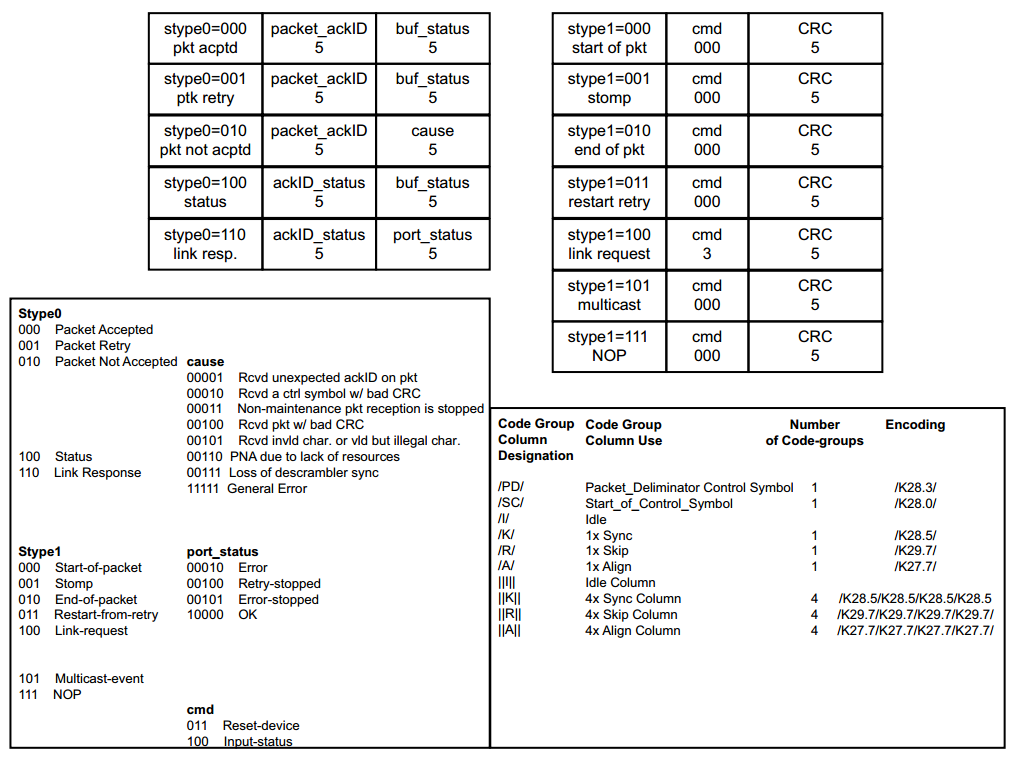

控制符號是由序列鏈路連線的埠所使用的訊息部分。控制符號用於鏈路維護、包定界、包確認,錯誤報告和錯誤恢復。

傳送時控制符號由一個單獨的8B/10B特殊(控制)字元定界。控制字元標記控制符號的開始並緊靠在控制符號的首位之前。為了通道分段(如果可用)和8B/10B編碼,在將控制符號傳遞到PCS子層前將用於定界控制的特殊字元加入控制符號。因為短控制符號的長度是固定的24位,所以控制符號不需要尾部定界符。定界符和控制符號組合在一起,稱為定界控制符號。

使用兩種特殊字元中的一種定界控制符號。如果控制符號包含一個包定界符,就使用專用字元PD(K28.3 )。如果控制符號不包含包定界符,就使用專用字元SC(K28.0)。如此使用特殊字元向接收者提供了一個控制符號內容的“預警(Early Warning)”訊號。

任何不包含包定界符的控制符號都可被嵌入到包中。嵌入的控制符號可能包含任何已定義的stype0編碼和“多播事件”或“NOP”之類的stype1編碼。不能將stype1作為包開始、包結束、消除、從重傳處重啟或鏈路請求控制符號嵌入到包中,因為它們會終止包。

在鏈路嵌入控制符號的方式和程度會影響鏈路和系統的效能。例如,嵌入多播事件控制符號允許它們的傳播延時和通過交換機處理部件的時延變化最小(某些多播事件應用迫切需要嵌入多播事件控制符號)。另一方面,嵌入所有的包確認控制符號而不是把它們儘可能多地與包定界控制符號組合的做法減少了可用於包傳送的鏈路頻寬,可能是我們所不希望的。

包:

序列 RapidIO包在傳送時由控制符號進行定界。由於包長度是變化的,所以同時需要包開始和包結束定界符。標記包的結束(包終止)的控制符號跟在包尾或嵌入的控制符號的後面。

用來進行包定界的控制符號如下:

1、 包開始

2、 包結束

3、 消除

4、 從重傳處重啟

5、 任意鏈路請求

由包開始控制符號標記包的開始。

包以下列三種方式之一終止:

1、 用包結束控制符號標記包尾。

2、 用包開始控制符號標記包尾,包開始控制符號標記新包的開始。

3、 用從重傳處重啟、消除或鏈路請求控制符號取消包。

每個包都需要一個識別符號來唯一的標識它的確認控制符號。該識別符號就是RapidIO包格式中的ackID欄位,對RapidIO序列物理層的包來說,ackID欄位的長度是5位,它允許在相鄰處理部件間存在1到32個未完成的待確認的請求或響應包,但只允許同時存在最多31個未完成的待確認包。

復位後分配給ackID 的初始值是 0b00000。ackID的後續值是連續分配的(按數字順序增加,達到最大數時返回到0),用來指示包的傳送次序。確認本身由控制符號組成。

序列RapidIO鏈路協議使用重傳從包傳送錯誤中恢復。為支援包重傳,傳送埠儲存每個通過序列鏈路傳輸的包的一個副本,直到收到接收埠發出的接收包的包確認控制符號或者直到埠判定該包已經遇到了不可恢復的錯誤情況。包確認控制符號指示接收埠已收到包並且沒有檢測到錯誤,同時已經接收對該包進行處理的責任。除了可能的錯誤,如果埠在接收到的包的優先順序上沒有足夠的可用輸入緩衝區空間,則埠也可能拒絕包。

產生包的端點處理部件為每個包分配一個優先順序。該優先順序包含在包的物理層欄位優先順序(PRIO)中並有四個可能的值: 0、1、2和3。包的優先順序隨優先順序值的增加而提高;最低優先順序為 0; 最高優先順序為3。使用包優先順序的目的有多個, 包括事務排序和死鎖預防。

3.3 空閒序列

空閒序列是一個碼組序列。當鏈路無需傳送包或控制符號時,在每個序列鏈路協議(LP- Serial)鏈路通道上連續地傳送空閒序列。空閒序列不能插入到包中。作為埠初始化過程的一部分, 在每個通道上傳送空閒序列。這是埠初始化協議所需要的。

1x空閒序列由碼組/K/、/A/、/R/ (空閒碼組)構成的偽隨機序列組成,由操作模式為1x的埠使用。4x空閒序列由縱列llKll、llAll、llRll(空閒縱列)構成的偽隨機序列組成,由操作模式為4x的埠使用。協議對空閒序列長度沒有要求。空閒序列可以是任意長度。

空閒序列中對碼組的偽隨機選擇導致空閒序列的頻譜中沒有離散譜線。這可以最小化長空閒序列產生的電磁干擾(EMI)。

空閒序列分為空閒序列1(Idle1 Sequence)和空閒序列2(Idle2 Sequence)。

空閒序列1(Idle1 Sequence):

空閒序列1是一組由A,K,R特殊字元組成的序列,這組序列在序列鏈路上傳送之前必須先經過8B/10B編碼器進行編碼產生對應的10-bit特殊碼組/A/,/K/,/R/之後才能在鏈路上傳送。

產生空閒序列1推薦使用至少7階的本原多項式來產生相應的偽隨機序列,例如:

X7+X6+1 和 X7+X3+1

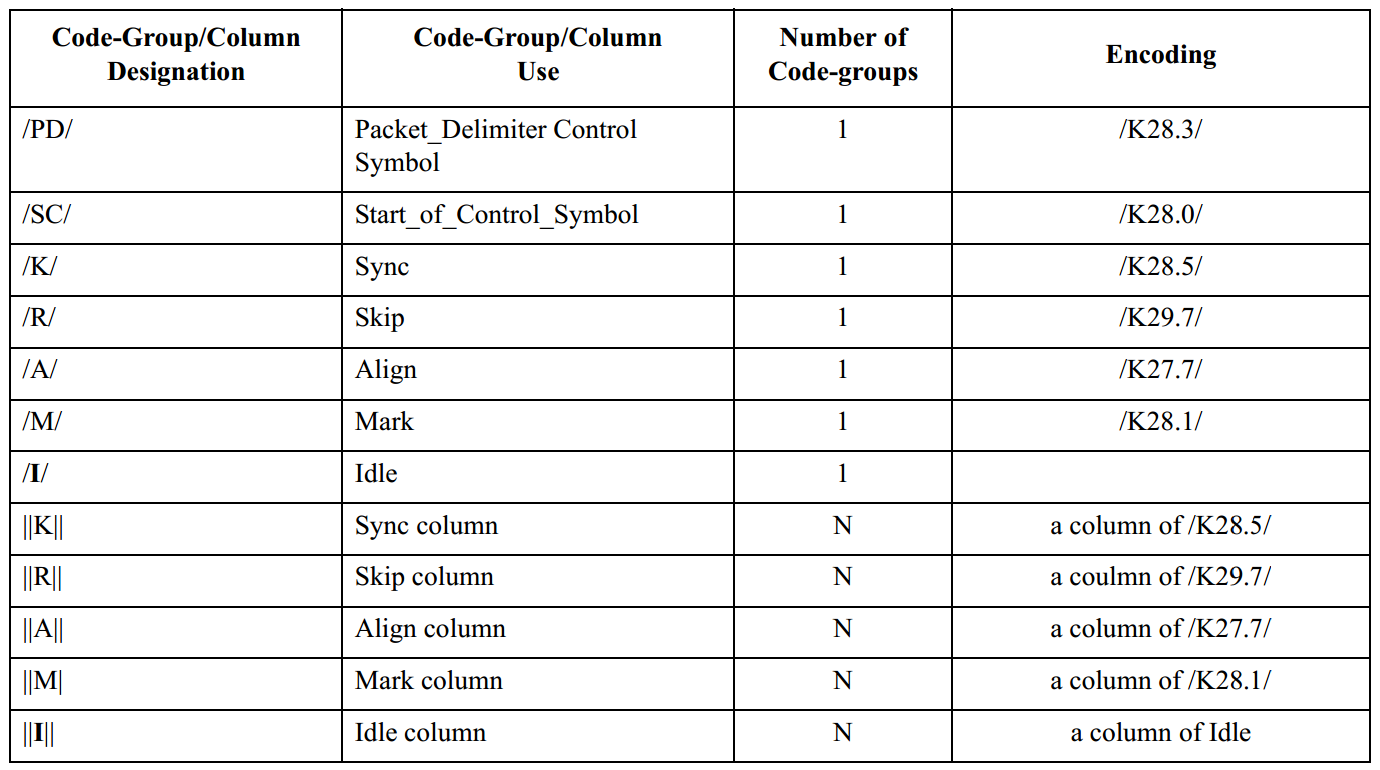

就是兩個7階本原多項式的例子,可以利用這兩個多項式的任意一個作為空閒序列1的偽隨機序列生成多項式。下圖是一個產生空閒序列1偽隨機序列的框圖

空閒序列2(Idle2 Sequence):

空閒序列2是一組由資料字元和特殊字元A,K,M,R組成的序列。這組序列在序列鏈路上傳送之前必須先經過8B/10B編碼器進行編碼產生對應的10-bit特殊碼組/A/,/K/,/M/和/R/之後才能在鏈路上傳送。

空閒序列2的空閒幀的結構如下所示

它包括509-515個字元的隨機資料域,8個字元的CS域標記以及32個字元的編碼CS域。其中隨機資料域包含偽隨機資料字元和A、M特殊字元。CS域標記欄位指明瞭命令和狀態(CS = Command and Status)域的起始位置,並且提供了鏈路極性,鏈路寬度和鏈路號等資訊。CS域給埠提供了一些狀態資訊和控制傳送埠的預加重設定。

空閒序列的選擇:

當序列鏈路每個通道的線速率在5.5Gbps以上時只能選擇空閒序列2(IDLE2 Sequence),當每通道的線速率低於5.5Gbps時既可以選擇空閒序列1(IDLE1 Sequence),也可以選擇空閒序列2(IDLE2 Sequence)。至於在埠初始化的過程中選擇空閒序列的演算法請檢視參考文獻1的516頁。

關於空閒序列的產生以及更加詳細的介紹請檢視參考文獻1的503頁到517頁。

3.4 1x序列RapidIO鏈路上的資料流

1x序列RapidIO埠通過8B/10B編碼器編碼從上層(邏輯層和傳輸層)依次傳送過來的分界控制符號與包的字元流,當控制符號與包不可獲得時,空閒序列將被送入8B/10B編碼器進行編碼併發送,以保證整個收發鏈路處於同步狀態。

對於接收鏈路來說,10-bit的碼組流將送入8B/10B解碼器進行解碼,然後把解碼得到的控制符號與包按照接收的順序依次傳入上層(邏輯層與傳輸層)。

如果鏈路的空閒序列為空閒序列2,控制符號和包資料字元在傳送之前需要擾碼,接收之前需要解擾。

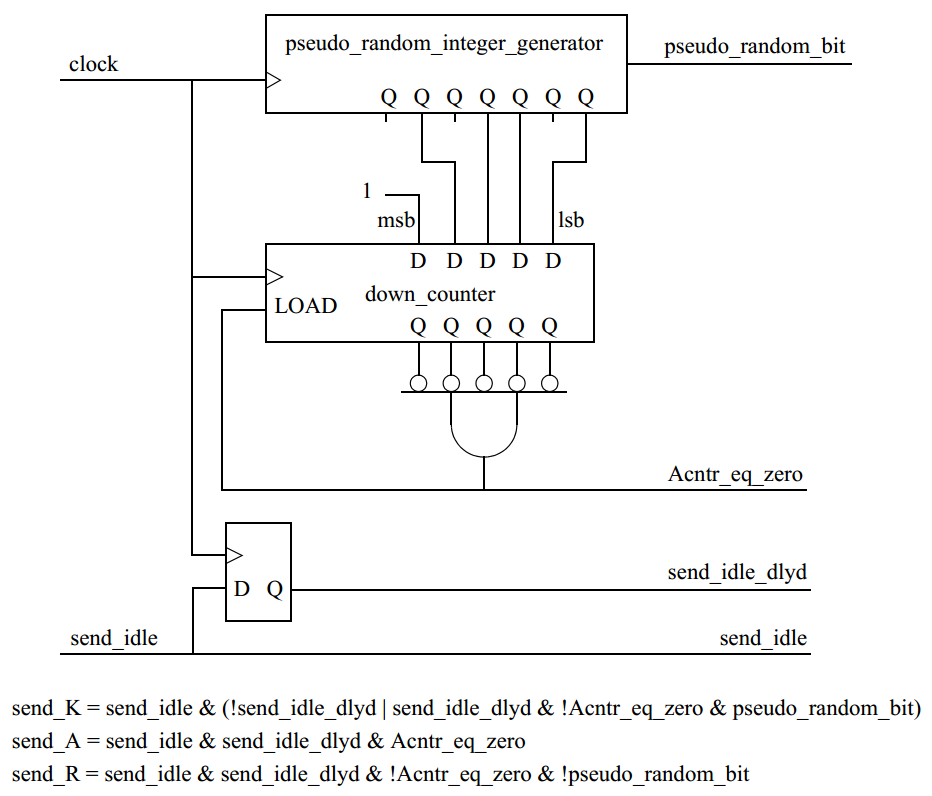

下圖顯示了短控制符號在1x序列RapidIO鏈路上的編碼和傳送順序示意圖

下圖顯示了RapidIO包在1x序列RapidIO鏈路上的編碼和傳送順序示意圖

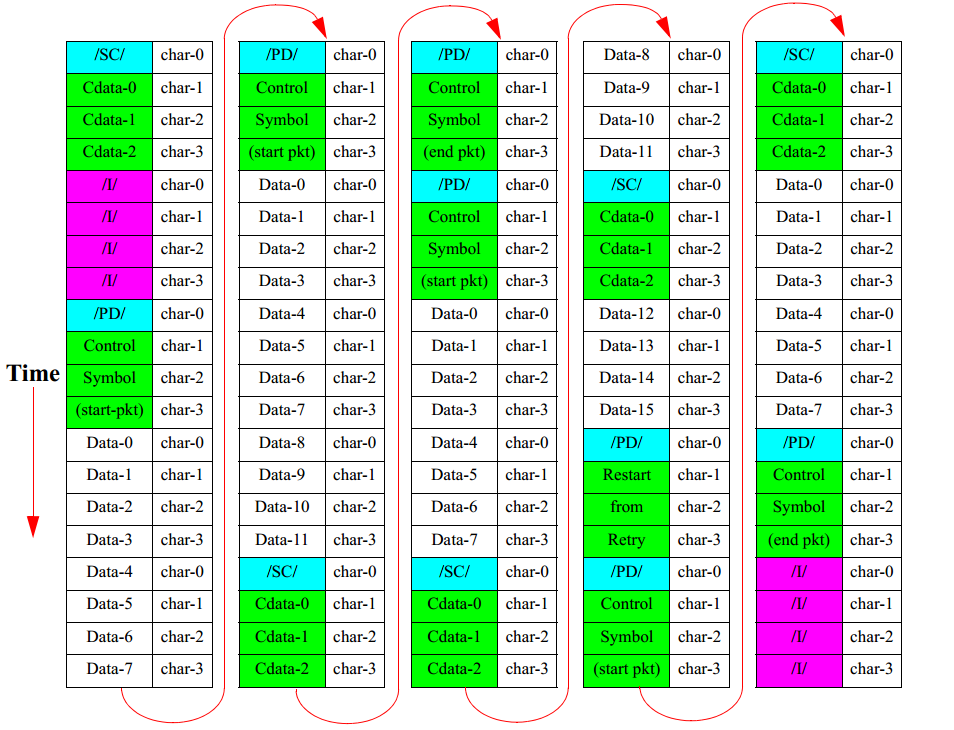

下圖顯示了一個在1x序列鏈路上傳送控制符號、包和空閒序列的例項。傳送的第一個碼組是代表控制符號開始的/SC/, 隨後是三個包含24位控制符號資訊的資料碼組。該控制符號的功能沒有顯示。控制符號後面跟著四個空閒字元。這四個空閒字元之後是一個定界包開始的/PD/碼組。後面三個碼組包含的控制符號資訊代表包定界符號資訊。碼組表示RapidIO包緊跟在該符號資訊之後。包長度為28位元組。包之後是一個包結束控制符號,這個包結束控制符號之後是另一個包開始控制符號和另一個數據包。在從重傳處重啟控制符號終止包前,該包能夠傳輸16位元組資訊。該包還插入了另外兩個控制符號, 這兩個控制符號分別插在資料流中的第8個數據位元組和第12個數據位元組之後。在RapidIO協議中,幾乎可在任意時刻將控制符號插入到通訊通道中, 無需等到包傳送完全完成即可插入控制符號。在傳送從重傳處重啟控制符號之後, 另一個包被髮送到鏈路上。該包正確地完成後鏈路成為空閒狀態。

3.5 4x序列RapidIO鏈路上的資料流

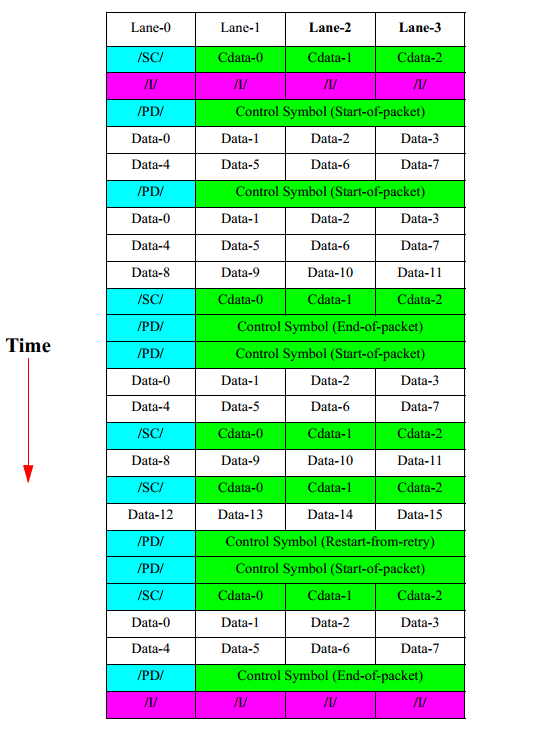

在4x操作模式下的串列埠在8B/10B編碼之前按如下方式將定界控制符號和組成包的字元流分段到四個通道上。

包和定界控制待號將被從通道0開始分段到四個通道上。每個包的第一個字元或定界控制符號被放到通道0,第二個字元被放到通道1 ,第三個字元被放到通道2,第四個字元被放到通道3。第五個字元又被放到通道0,如此迴圈。

由於控制符號的長度是固定的24位並且要求包的長度必須是32位的整數倍, 分段後定界控制符號的碼組總被放到通道0。所有包將形成整數個連續的縱列。在分段後, 4個字元流的每一個流都被獨立地進行8B/10B編碼和傳送。

在接收方對每個通道進行解碼。解碼後, 字元流對齊這4個通道。作為4x空閒序列的一部分發送的llAll縱列提供執行對齊所需的資訊。在對齊之後,縱列被合併為單獨的字元流, 然後被傳遞到上層 。

通道對齊過程消除了通道間的偏移,這樣在合併(destriping)後接收到的字元流中字元的順序與在分段和傳送前字元的順序相同。 由於||A||縱列之間最小的非llAll縱列數量為16, 所以可以明確修正的最大通道偏移是在一個通道上傳送7個碼組的時間 。下圖顯示了一個在4x鏈路上傳送空閒序列、包和定界控制符號的例項。 該例項使用的包序列與1x鏈路的例項相同。

四、總結

RapidIO序列物理層的8B/10B編解碼原理與包傳輸流程相關的內容到此介紹完畢,更多詳細的內容請閱讀參考文獻1的第485頁到560頁。為了便於大家以後的查閱,下面把控制符號與K碼相關的定義全部列到一起。

注意:上圖列出的是短控制符號的定義。長控制符號總長度為48位而短控制符號的總長度為24位。

至此,整個RapidIO理論部分全部介紹完畢,後面會繼續寫Xilinx RapidIO核的相關內容。

五、參考資料

1、RapidIO™ Interconnect Specification,下載連結 https://pan.baidu.com/s/1ek-3AAhetLAcxTuOE2IyMg

2、RapidIO嵌入式系統互連,電子工業出版社

3、Xilinx的pg007_srio_gen2,下載地址 https://china.xilinx.com/support/documentation/ip_documentation/srio_gen2/v4_0/pg007_srio_gen2.pdf