Vivado開發流程簡介(FPGA)(硬體設計)

阿新 • • 發佈:2018-11-24

前言:系統環境windows7 +Vivado2016.1.

1、啟動Vivado:

2、選擇Create New Project:

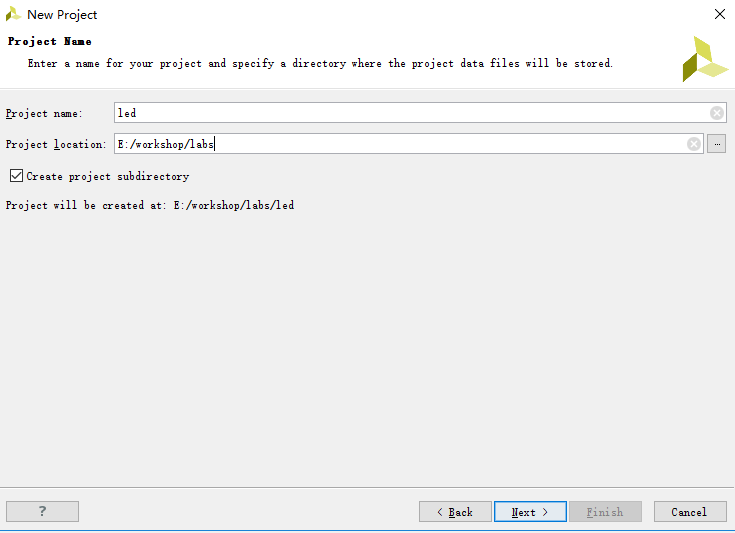

3、指定工程名字和工程存放目錄:

4、選擇RTL Project:

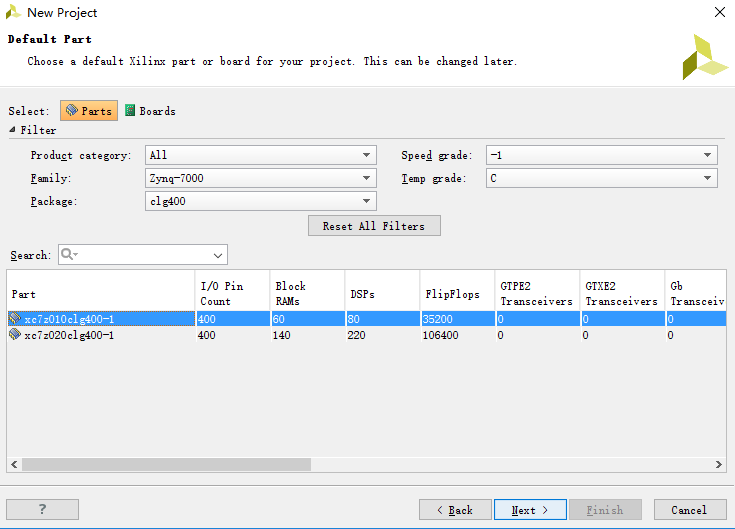

5、選擇FPGA裝置:

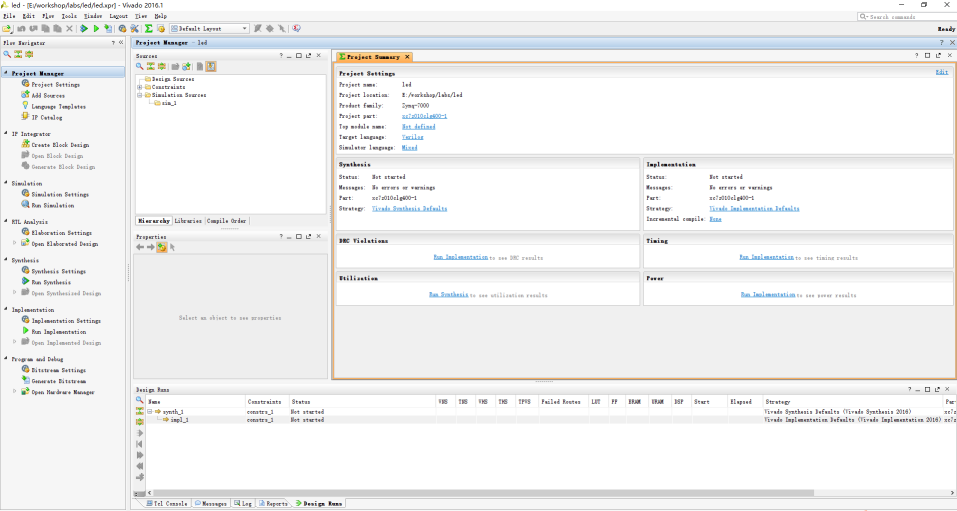

6、工程建立完成後:

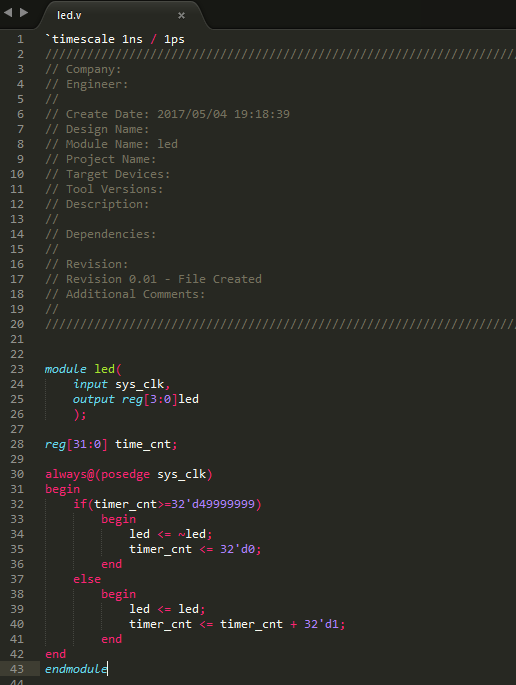

7、開始編寫verilog程式碼:

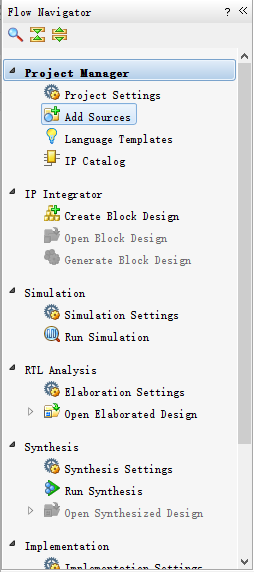

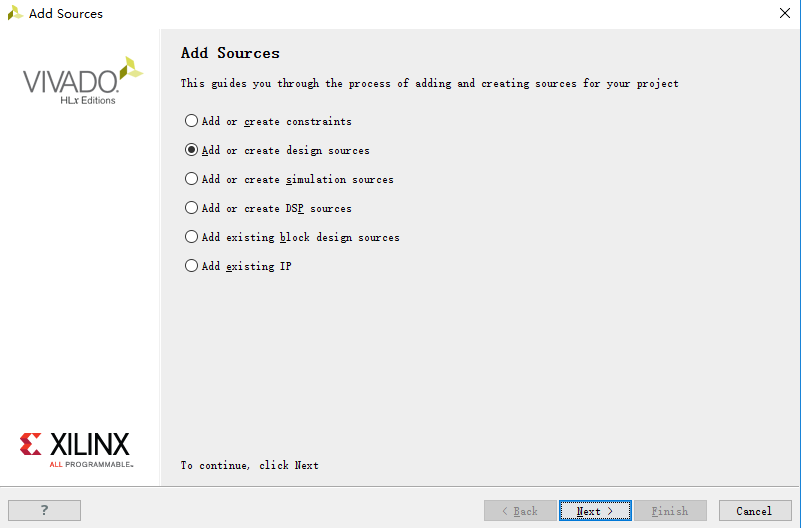

(1)點選Add Sources按鈕:

(2)選擇add or create design sources按鈕,即新增設計檔案:

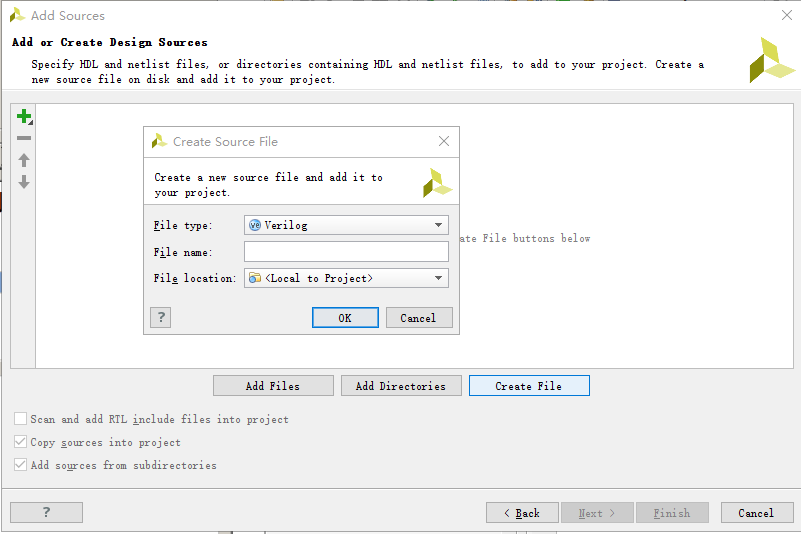

(3)選擇create file:

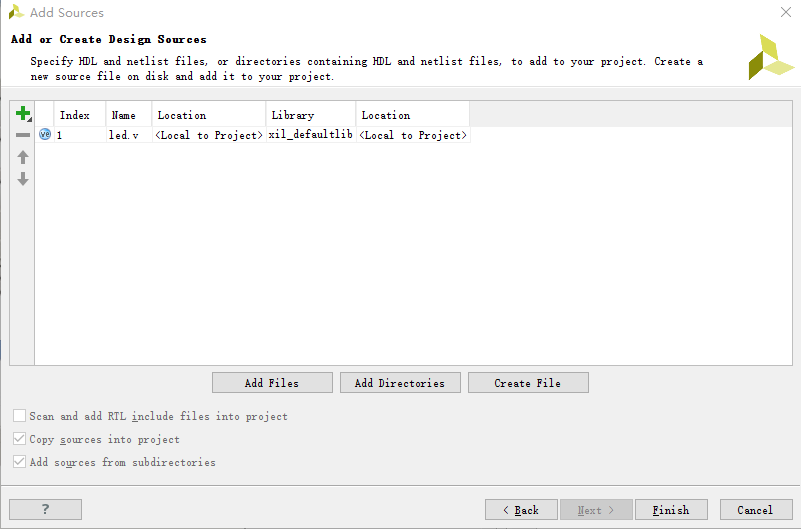

(4)檔案新建完成後:

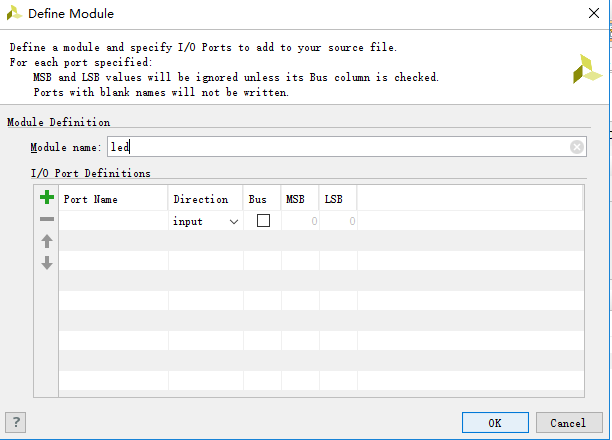

(5)此時可以定義I/O埠,我們選擇自己在程式中編寫:

(6)在編輯器中編寫verilog程式:

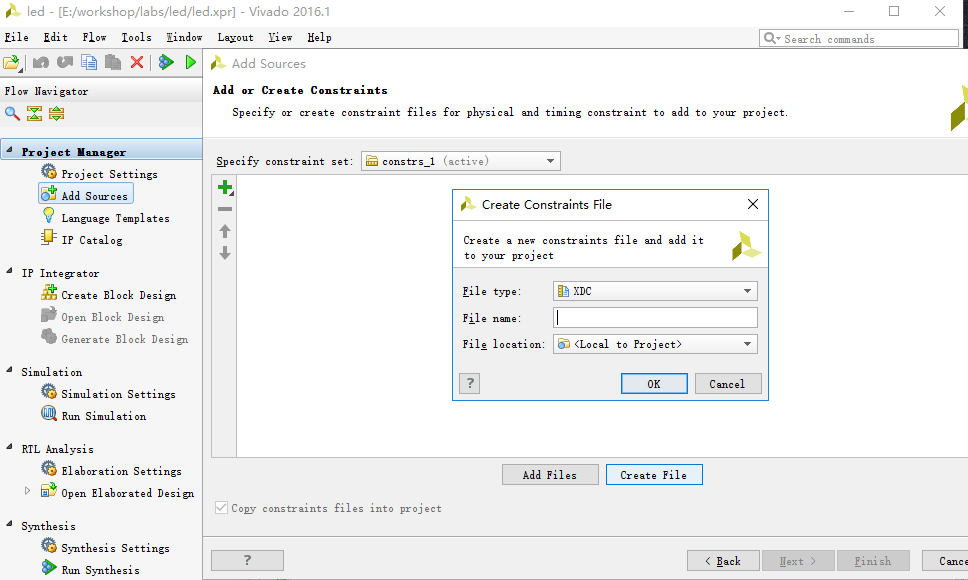

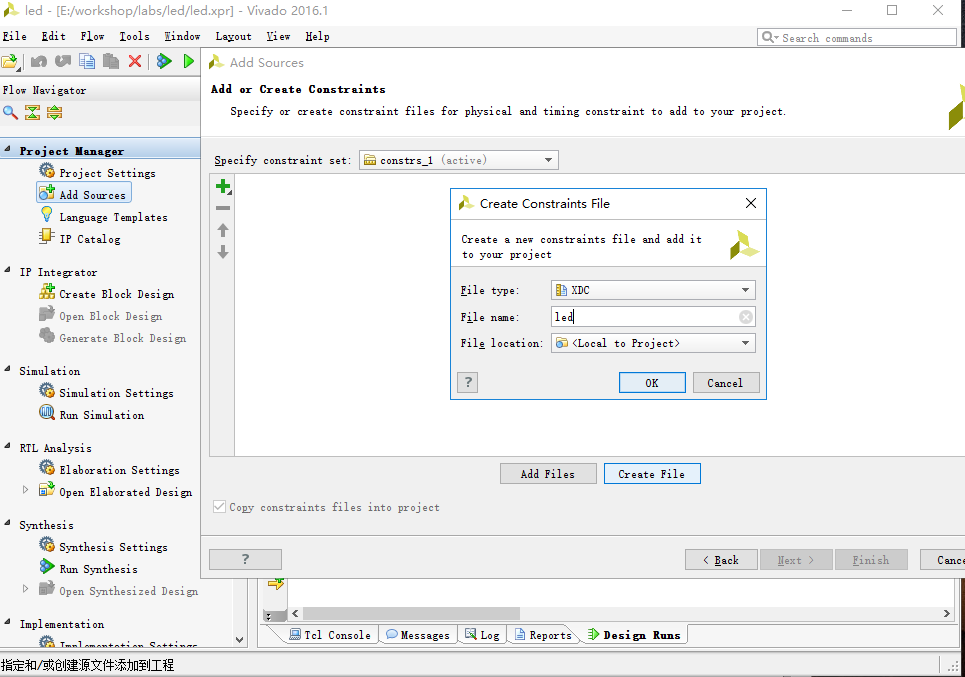

8、新增XDC管腳約束檔案(XDC檔案裡主要是完成管腳的約束,時鐘的約束,以及組的約束):

(1)新建約束檔案:

(2)創造約束檔案:

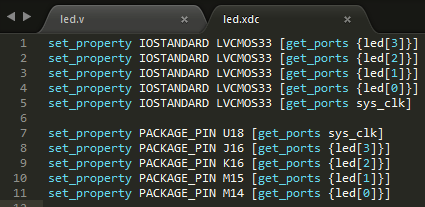

(3)編輯管腳約束檔案:

其中,set_property PACKAGE_PIN “引腳編號” [get_ports “埠名稱”]

Set_property IOSTANDARD “電壓” [get_ports “埠名稱”]

9、編譯:

(1)執行Run Synthesis 綜合

(2)執行Run Implementation 佈局佈線

(3)執行Generate Bitstream 生成bit檔案

10、下載和除錯:

執行Hardware Manager。

######## 轉載請註明出處從 https://blog.csdn.net/gentleman_qin/article/details/80044471 ########