u-boot-2015.07移植(SPL)①

本文參考https://blog.csdn.net/doccode/article/details/47212363,在此謝過!

SPL方式移植U-BOOT-2015.07

在JZ2440板子上移植u-boot-2015.07,移植思路,利用smdk2410板子作為基線進行移植.下載u-boot-2015.07.tar.bz2 解壓u-boot-2015.07.tar.bz2 到u-boot-2015.07資料夾

tar xjvf u-boot-2015.07.tar.bz2

一.檔案準備

1.在u-boot-2015.07上級目錄新建

vi spl.patch

注意:在執行make distclean的時候, patch檔案在u-boot-2015.07目錄下時會一併清除掉!!!

2.進入u-boot-2015.07/board/samsung目錄,複製smdk2410資料夾並命名為 smdk2440資料夾

cp -r smdk2410 smdk2440

修改smdk2440目錄下的smdk2410.c為smdk2440.c

mv smdk2410.c smdk2440.c

3.在./configs目錄下面的smdk2410_defconfig 複製為smdk2440_defconfig

cp ./configs/smdk2410_defconfig ./configs/smdk2440_defconfig

4.在./include/configs目錄下面的smdk2410.h複製為smdk2440.h

cp ./include/configs/smdk2410.h ./include/configs/smdk2440.h

5.在./drivers/mtd/nand/目錄下面的s3c2410_nand.c複製為s3c2440_nand.c

cp ./drivers/mtd/nand/s3c2410_nand.c ./drivers/mtd/nand/s3c2440_nand.c

6.新建檔案./board/samsung/smdk2440/nand_read_ii.c(參考文章開頭連結,在此不貼出來了)

7.返回上級目錄壓縮資料夾備份一下

tar cjvf u-boot-2015.07_smdk2440_spl.tar.bz2 u-boot-2015.07

二、製作補丁檔案

spl.patch .patch對應要修改的檔案

01 ./Kconfig

02 ./arch/arm/lib/crt0.S

03 ./arch/arm/Kconfig

04 ./board/samsung/smdk2440/Kconfig

05 ./board/samsung/smdk2440/Makefile

06 ./include/configs/smdk2440.h

07 ./configs/smdk2440_defconfig

08 ./Makefile

09 ./drivers/mtd/nand/s3c2440_nand.c

10 ./drivers/mtd/nand/Makefile

11 ./arch/arm/cpu/arm920t/start.S

12 ./board/samsung/smdk2440/lowlevel_init.S

13 ./board/samsung/smdk2440/smdk2440.c

14 ./board/samsung/smdk2440/MAINTAINERS

補丁檔案內容:

1 --- u-boot-2015.07/Kconfig 2 @@ -105,1 +105,1 @@ 3 - bool 4 + bool "SUPPORT_SPL" 5 --- u-boot-2015.07/arch/arm/lib/crt0.S 6 @@ -103,2 +103,14 @@ 7 - /* mov r0, #0 not needed due to above code */ 8 - bl board_init_f 9 +#if defined(CONFIG_SPL_BUILD) 10 + /* Read u-boot from Nandflash to SDRAM address $CONFIG_SYS_TEXT_BASE */ 11 + ldr r0,=CONFIG_UBOOT_NAND_ADDR /* nand_read_ii() 1nd argument */ 12 + ldr r1,=CONFIG_SYS_TEXT_BASE /* nand_read_ii() 2st argument */ 13 + ldr r2,=CONFIG_UBOOT_LENGTH /* nand_read_ii() 3rd argument */ 14 + 15 + bl copy_code_to_sdram 16 + 17 + ldr pc,=CONFIG_SYS_TEXT_BASE 18 + 19 +#else 20 + /* mov r0, #0 not needed due to above code */ 21 + bl board_init_f 22 +#endif 23 --- u-boot-2015.07/arch/arm/Kconfig 24 @@ -87,0 +87,4 @@ 25 + 26 +config TARGET_SMDK2440 27 + bool "Support smdk2440" 28 + select CPU_ARM920T 29 @@ -947,0 +947,1 @@ 30 +source "board/samsung/smdk2440/Kconfig" 31 #--- u-boot-2015.07/arch/arm/config.mk 32 #@@ -82,1 +82,1 @@ 33 #-LDFLAGS_u-boot += -pie 34 #+#LDFLAGS_u-boot += -pie 35 #@@ -104,1 +104,1 @@ 36 #-ALL-y += checkarmreloc 37 #+#-ALL-y += checkarmreloc 38 --- u-boot-2015.07/board/samsung/smdk2440/Kconfig 39 @@ -1,15 +1,15 @@ 40 -if TARGET_SMDK2410 41 - 42 -config SYS_BOARD 43 - default "smdk2410" 44 - 45 -config SYS_VENDOR 46 - default "samsung" 47 - 48 -config SYS_SOC 49 - default "s3c24x0" 50 - 51 -config SYS_CONFIG_NAME 52 - default "smdk2410" 53 - 54 -endif 55 +if TARGET_SMDK2440 56 + 57 +config SYS_BOARD 58 + default "smdk2440" 59 + 60 +config SYS_VENDOR 61 + default "samsung" 62 + 63 +config SYS_SOC 64 + default "s3c24x0" 65 + 66 +config SYS_CONFIG_NAME 67 + default "smdk2440" 68 + 69 +endif 70 --- u-boot-2015.07/board/samsung/smdk2440/Makefile 71 @@ -7,3 +7,3 @@ 72 - 73 -obj-y := smdk2410.o 74 -obj-y += lowlevel_init.o 75 +obj-y := smdk2440.o 76 +obj-y += lowlevel_init.o 77 +obj-$(CONFIG_SPL_BUILD) += nand_read_ii.o 78 --- u-boot-2015.07/include/configs/smdk2440.h 79 @@ -8,1 +8,1 @@ 80 - * Configuation settings for the SAMSUNG SMDK2410 board. 81 + * Configuation settings for the SAMSUNG SMDK2440 board. 82 @@ -21,2 +21,2 @@ 83 -#define CONFIG_S3C2410 /* specifically a SAMSUNG S3C2410 SoC */ 84 -#define CONFIG_SMDK2410 /* on a SAMSUNG SMDK2410 Board */ 85 +#define CONFIG_S3C2440 /* specifically a SAMSUNG S3C2440 SoC */ 86 +#define CONFIG_SMDK2440 /* on a SAMSUNG SMDK2440 Board */ 87 @@ -24,1 +24,6 @@ 88 -#define CONFIG_SYS_TEXT_BASE 0x0 89 +/* set linker addr = 0x33f0_0000 = 0x3400_0000 - 0x100_0000 */ 90 +/* 64M 1M*/ 91 +#define CONFIG_SYS_TEXT_BASE 0x30008000 92 +#define CONFIG_UBOOT_LENGTH 0x100000 93 +#define CONFIG_UBOOT_NAND_ADDR 0x20000 94 +#define CONFIG_SPL_STACK 0X1000 95 #+#define CONFIG_SYS_GENERIC_GLOBAL_DATA 96 #@@ -26,1 +26,1 @@ 97 #-#define CONFIG_SYS_GENERIC_BOARD 98 #+/* #define CONFIG_SYS_GENERIC_BOARD */ 99 @@ -30,1 +30,1 @@ 100 -/* input clock of PLL (the SMDK2410 has 12MHz input clock) */ 101 +/* input clock of PLL (the SMDK2440 has 12MHz input clock) */ 102 @@ -41,1 +41,1 @@ 103 -#define CONFIG_CS8900_BASE 0x19000300 104 +#define CONFIG_CS8900_BASE 0x20000000 105 @@ -48,1 +48,1 @@ 106 -#define CONFIG_SERIAL1 1 /* we use SERIAL 1 on SMDK2410 */ 107 +#define CONFIG_SERIAL1 1 /* we use SERIAL 1 on SMDK2440 */ 108 @@ -109,1 +109,1 @@ 109 -#define CONFIG_SYS_PROMPT "SMDK2410 # " 110 +#define CONFIG_SYS_PROMPT "SMDK2440 # " 111 @@ -146,1 +146,0 @@ 112 -#define CONFIG_FLASH_CFI_LEGACY 113 @@ -152,1 +152,1 @@ 114 -#define CONFIG_SYS_MAX_FLASH_SECT (19) 115 +#define CONFIG_SYS_MAX_FLASH_SECT (35) 116 @@ -173,2 +173,2 @@ 117 -#define CONFIG_NAND_S3C2410 118 -#define CONFIG_SYS_S3C2410_NAND_HWECC 119 +#define CONFIG_NAND_S3C2440 120 +#define CONFIG_SYS_S3C2440_NAND_HWECC 121 --- u-boot-2015.07/configs/smdk2440_defconfig 122 @@ -2,1 +2,2 @@ 123 -CONFIG_TARGET_SMDK2410=y 124 +CONFIG_TARGET_SMDK2440=y 125 +CONFIG_SPL=y 126 --- u-boot-2015.07/Makefile 127 @@ -243,0 +243,2 @@ 128 +ARCH = arm 129 +CROSS_COMPILE ?=arm-linux- 130 --- u-boot-2015.07/drivers/mtd/nand/s3c2440_nand.c 131 @@ -14,11 +14,11 @@ 132 -#define S3C2410_NFCONF_EN (1<<15) 133 -#define S3C2410_NFCONF_512BYTE (1<<14) 134 -#define S3C2410_NFCONF_4STEP (1<<13) 135 -#define S3C2410_NFCONF_INITECC (1<<12) 136 -#define S3C2410_NFCONF_nFCE (1<<11) 137 -#define S3C2410_NFCONF_TACLS(x) ((x)<<8) 138 -#define S3C2410_NFCONF_TWRPH0(x) ((x)<<4) 139 -#define S3C2410_NFCONF_TWRPH1(x) ((x)<<0) 140 - 141 -#define S3C2410_ADDR_NALE 4 142 -#define S3C2410_ADDR_NCLE 8 143 +#define S3C2440_NFCONF_EN (1<<15) 144 +#define S3C2440_NFCONF_512BYTE (1<<14) 145 +#define S3C2440_NFCONF_4STEP (1<<13) 146 +#define S3C2440_NFCONF_INITECC (1<<12) 147 +#define S3C2440_NFCONF_nFCE (1<<11) 148 +#define S3C2440_NFCONF_TACLS(x) ((x)<<8) 149 +#define S3C2440_NFCONF_TWRPH0(x) ((x)<<4) 150 +#define S3C2440_NFCONF_TWRPH1(x) ((x)<<0) 151 + 152 +#define S3C2440_ADDR_NALE 4 153 +#define S3C2440_ADDR_NCLE 8 154 @@ -52,11 +52,11 @@ 155 - IO_ADDR_W |= S3C2410_ADDR_NCLE; 156 - if (!(ctrl & NAND_ALE)) 157 - IO_ADDR_W |= S3C2410_ADDR_NALE; 158 - 159 - chip->IO_ADDR_W = (void *)IO_ADDR_W; 160 - 161 - if (ctrl & NAND_NCE) 162 - writel(readl(&nand->nfconf) & ~S3C2410_NFCONF_nFCE, 163 - &nand->nfconf); 164 - else 165 - writel(readl(&nand->nfconf) | S3C2410_NFCONF_nFCE, 166 + IO_ADDR_W |= S3C2440_ADDR_NCLE; 167 + if (!(ctrl & NAND_ALE)) 168 + IO_ADDR_W |= S3C2440_ADDR_NALE; 169 + 170 + chip->IO_ADDR_W = (void *)IO_ADDR_W; 171 + 172 + if (ctrl & NAND_NCE) 173 + writel(readl(&nand->nfconf) & ~S3C2440_NFCONF_nFCE, 174 + &nand->nfconf); 175 + else 176 + writel(readl(&nand->nfconf) | S3C2440_NFCONF_nFCE, 177 @@ -77,7 +77,7 @@ 178 -#ifdef CONFIG_S3C2410_NAND_HWECC 179 -void s3c24x0_nand_enable_hwecc(struct mtd_info *mtd, int mode) 180 -{ 181 - struct s3c24x0_nand *nand = s3c24x0_get_base_nand(); 182 - debug("s3c24x0_nand_enable_hwecc(%p, %d)\n", mtd, mode); 183 - writel(readl(&nand->nfconf) | S3C2410_NFCONF_INITECC, &nand->nfconf); 184 -} 185 +#ifdef CONFIG_S3C2440_NAND_HWECC 186 +void s3c24x0_nand_enable_hwecc(struct mtd_info *mtd, int mode) 187 +{ 188 + struct s3c24x0_nand *nand = s3c24x0_get_base_nand(); 189 + debug("s3c24x0_nand_enable_hwecc(%p, %d)\n", mtd, mode); 190 + writel(readl(&nand->nfconf) | S3C2440_NFCONF_INITECC, &nand->nfconf); 191 +} 192 @@ -133,4 +133,4 @@ 193 - cfg = S3C2410_NFCONF_EN; 194 - cfg |= S3C2410_NFCONF_TACLS(tacls - 1); 195 - cfg |= S3C2410_NFCONF_TWRPH0(twrph0 - 1); 196 - cfg |= S3C2410_NFCONF_TWRPH1(twrph1 - 1); 197 + cfg = S3C2440_NFCONF_EN; 198 + cfg |= S3C2440_NFCONF_TACLS(tacls - 1); 199 + cfg |= S3C2440_NFCONF_TWRPH0(twrph0 - 1); 200 + cfg |= S3C2440_NFCONF_TWRPH1(twrph1 - 1); 201 @@ -156,1 +156,1 @@ 202 -#ifdef CONFIG_S3C2410_NAND_HWECC 203 +#ifdef CONFIG_S3C2440_NAND_HWECC 204 @@ -168,1 +168,1 @@ 205 -#ifdef CONFIG_S3C2410_NAND_BBT 206 +#ifdef CONFIG_S3C2410_NAND_BBT 207 --- u-boot-2015.07/drivers/mtd/nand/Makefile 208 @@ -63,0 +63,1 @@ 209 +obj-$(CONFIG_NAND_S3C2440) += s3c2440_nand.o 210 --- u-boot-2015.07/arch/arm/cpu/arm920t/start.S 211 @@ -52,0 +52,1 @@ 212 +#ifdef CONFIG_SPL_BUILD 213 @@ -77,2 +77,2 @@ 214 -# if defined(CONFIG_S3C2410) 215 - ldr r1, =0x3ff 216 +# if defined(CONFIG_S3C2440) 217 + ldr r1, =0x7fff 218 @@ -83,5 +83,26 @@ 219 - /* FCLK:HCLK:PCLK = 1:2:4 */ 220 - /* default FCLK is 120 MHz ! */ 221 - ldr r0, =CLKDIVN 222 - mov r1, #3 223 - str r1, [r0] 224 +#define LOCKTIME 0x4c000000 225 +#define MPLL_CON 0x4c000004 226 + 227 +#define DIV_VAL ((2 << 1) | (1 << 0)) 228 +#define S3C2440_FLCK_400M ((0x5c << 12) | (0x01 << 4) | (0x01)) 229 + 230 +init_clock: 231 +/* set LOCKTIME = 0xffffffff */ 232 + ldr r0, =LOCKTIME 233 + ldr r1, =0xffffffff 234 + str r1, [r0] 235 + 236 +/* set tFCLK:tHCLK:tPCLK = 1:4:8 FCLK:HCLK:PCLK = 400M:100M:50M */ 237 + ldr r0, =CLKDIVN 238 + ldr r1, =DIV_VAL 239 + str r1, [r0] 240 + 241 +/* set s3c2440 working asynchronous mode */ 242 + mrc p15,0,r0,c1,c0,0 243 + orr r0,r0,#0xc0000000 244 + mcr p15,0,r0,c1,c0,0 245 + 246 +/* FLCK = 400MHz */ 247 + ldr r0, =MPLL_CON 248 + ldr r1, =S3C2440_FLCK_400M 249 + str r1,[r0] 250 @@ -97,0 +97,1 @@ 251 +#endif /* CONFIG_SPL_BUILD */ 252 --- u-boot-2015.07/board/samsung/smdk2440/lowlevel_init.S 253 @@ -7,1 +7,1 @@ 254 - * Modified for the Samsung SMDK2410 by 255 + * Modified for the Samsung SMDK2440 by 256 @@ -36,7 +36,7 @@ 257 -#define B1_BWSCON (DW32) 258 -#define B2_BWSCON (DW16) 259 -#define B3_BWSCON (DW16 + WAIT + UBLB) 260 -#define B4_BWSCON (DW16) 261 -#define B5_BWSCON (DW16) 262 -#define B6_BWSCON (DW32) 263 -#define B7_BWSCON (DW32) 264 +#define B1_BWSCON (DW16) 265 +#define B2_BWSCON (DW16) 266 +#define B3_BWSCON (DW16 + UBLB) 267 +#define B4_BWSCON (DW16 + WAIT + UBLB) /*網絡卡*/ 268 +#define B5_BWSCON (DW8) 269 +#define B6_BWSCON (DW32) /*SDRAM*/ 270 +#define B7_BWSCON (DW32) 271 @@ -78,7 +78,7 @@ 272 -#define B4_Tacs 0x0 /* 0clk */ 273 -#define B4_Tcos 0x0 /* 0clk */ 274 -#define B4_Tacc 0x7 /* 14clk */ 275 -#define B4_Tcoh 0x0 /* 0clk */ 276 -#define B4_Tah 0x0 /* 0clk */ 277 -#define B4_Tacp 0x0 278 -#define B4_PMC 0x0 /* normal */ 279 +#define B4_Tacs 0x0 /* 0clk */ 280 +#define B4_Tcos 0x3 /* 4clk */ 281 +#define B4_Tacc 0x7 /* 14clk */ 282 +#define B4_Tcoh 0x1 /* 1clk */ 283 +#define B4_Tah 0x3 /* 4clk */ 284 +#define B4_Tacp 0x6 /* 6clk */ 285 +#define B4_PMC 0x0 /* normal */ 286 @@ -108,1 +108,1 @@ 287 -#define REFCNT 1113 /* period=15.6us, HCLK=60Mhz, (2048+1-15.6*60) */ 288 +#define REFCNT 0x4f4 /* period=7.8125us, HCLK=100Mhz, (2048+1-7.8125*100) */ 289 @@ -117,1 +117,2 @@ 290 - ldr r1, =CONFIG_SYS_TEXT_BASE 291 +/* ldr r1, =CONFIG_SYS_TEXT_BASE */ 292 + ldr r1, =0x0 293 @@ -144,1 +144,1 @@ 294 - .word 0x32 295 + .word 0xb1 296 --- u-boot-2015.07/board/samsung/smdk2440/smdk2440.c 297 @@ -60,9 +60,0 @@ 298 - /* to reduce PLL lock time, adjust the LOCKTIME register */ 299 - writel(0xFFFFFF, &clk_power->locktime); 300 - 301 - /* configure MPLL */ 302 - writel((M_MDIV << 12) + (M_PDIV << 4) + M_SDIV, 303 - &clk_power->mpllcon); 304 - 305 - /* some delay between MPLL and UPLL */ 306 - pll_delay(4000); 307 @@ -99,2 +99,2 @@ 308 - /* arch number of SMDK2410-Board */ 309 - gd->bd->bi_arch_number = MACH_TYPE_SMDK2410; 310 + /* arch number of SMDK2440-Board */ 311 + gd->bd->bi_arch_number = MACH_TYPE_S3C2440; 312 --- u-boot-2015.07/board/samsung/smdk2440/MAINTAINERS 313 @@ -1,1 +1,1 @@ 314 -SMDK2410 BOARD 315 +SMDK2440 BOARD 316 @@ -4,3 +4,3 @@ 317 -F: board/samsung/smdk2410/ 318 -F: include/configs/smdk2410.h 319 -F: configs/smdk2410_defconfig 320 +F: board/samsung/smdk2440/ 321 +F: include/configs/smdk2440.h 322 +F: configs/smdk2440_defconfig

三、MAKE

1. 打補丁: patch -p1 < ../spl.patch

2. 配置: make smdk2440_defconfig

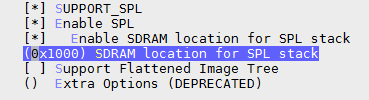

3. 設定 make menuconfig

4.Make

四、使用TFTP下載

1. 把./spl/u-boot-spl.bin和./u-boot.bin複製到windows的某個目錄下。

2. 用網線將開發板和電腦主機連線

3. 設定電腦主機:

IP地址為192.168.13.122

子網掩碼為255.255.255.0

閘道器為192.168.13.1

4.開發板需要燒寫好u-boot,修改 ip

set ipaddr 192.168.13.123

set serverip 192.168.13.122

set gatewayip 255.255.255.0

save

5.檢視開發板和電腦是否能ping通

開發板u-boot命令列輸入ping 192.168.13.122 顯示is not alive-->不通 顯示is alive-->連通

6.以管理員身份開啟tftpd32可執行檔案,將目錄定位到u-boot-spl.bin和u-boot.bin所在目錄

7.到u-boot介面,輸入以下命令

7.1 tfpt 3000_0000 u-boot-spl.bin 將u-boot-spl.bin下載到起始地址為3000_0000的記憶體

回顯: Bytes transferred = 976 (3d0 hex)

7.2 nand erase 0 0x20000 將nand的前0x20000位元組擦除

回顯: Erasing at 0x0 -- 100% complete.

7.3 nand write 3000_0000 0 0x20000 把u-boot-spl.bin從3000_0000地址寫入nand的0地址

回顯: 131072 bytes written: OK

7.4 tftp 3000_0000 u-boot.bin 將u-boot.bin下載到起始地址為3000_0000的記憶體

回顯: Loading: ######################################################################################################

done

Bytes transferred = 522092 (7f76c hex)

7.5 nand erase 0x20000 0x120000 將nand的0x20000---0x120000位元組擦除

回顯 :Erasing at 0x120000 -- 100% complete. OK

7.6 nand write 3000_0000 0x20000 0xc0000 從記憶體寫入nand的0x20000開始的地址

回顯 :786432 bytes written: OK

以上6條命令可以一次執行,中間用分號隔開。

8. reset重啟系統後串列埠顯示:

U-Boot 2015.07 (Nov 26 2018 - 09:59:02 +0800)

CPUID: 32440001

FCLK: 400 MHz

HCLK: 100 MHz

PCLK: 50 MHz

DRAM: 64 MiB

WARNING: Caches not enabled

Flash: ## Unknown flash on Bank 1 - Size = 0x00000000 = 0 MB

0 Bytes

NAND: 0 MiB

*** Warning - bad CRC, using default environment

In: serial

Out: serial

Err: serial

Net: CS8900-0

Error: CS8900-0 address not set.