Intel Platform Firmware Resilience

Intel Platform Firmware Resilience

Intel PFR是一項安全技術,目的是保護伺服器系統免遭PDoS攻擊。在Whitley平臺設計中,PFR是一個可選的特徵。實現PFR特徵需要硬體和軟體的協作。本文件用於描述PFR的硬體設計需求。關於PFR韌體開發指南在其他文件有闡述。

Intel PFR的關鍵前提是無論一個系統是否存在韌體保護,黑客都有辦法繞過這些保護措施。Intel PFR提供了韌體保護和恢復功能,它可以檢測系統是否遭受了攻擊,以及遭受攻擊後,將系統恢復到一個正常狀態。這個過程是快速的且無需使用者干涉的,非常適合大型資料中心。Intel PFR技術是通過把信任的根源放置到Intel Xeon處理器(Intel PFR-Enabled)和平臺的PFR CPLD實現的。同時,處理器和PFR CPLD授權平臺上的其他各種韌體,如果必要,可以把這些韌體恢復到正常狀態。在執行過程中,Intel PFR技術提供了對關鍵匯流排(諸如SPI和SMBus,它們可以訪問NV儲存)的主動過濾能力。這可以避免對關鍵部件(諸如SPI Flash,電源韌體,熱交換背板韌體和數字電壓調節器韌體)損壞的攻擊。

Intel PFR也提供一種可選的PIT功能(運輸途中保護),保護系統在運輸中免遭篡改。

韌體保護和恢復

Intel PFR提供多層韌體攻擊保護和韌體恢復機制,因此增加了平臺的彈性:

- 顯式檢查:執行在Intel Xeon處理器(PFR-Enabled)的廠商程式碼模組(VCM)對平臺韌體執行簽名驗證(比如,SPI描述,BIOS,BMC,Intel ME, NIC).

- 隱式檢查:PFR CPLD監測平臺引導過程,檢查與正常引導行為的差異.

- 主動過濾:PFR CPLD維護一個針對不同平臺元件允許的SPI和SMBus命令白名單,這可以過濾惡意的訪問和操作。

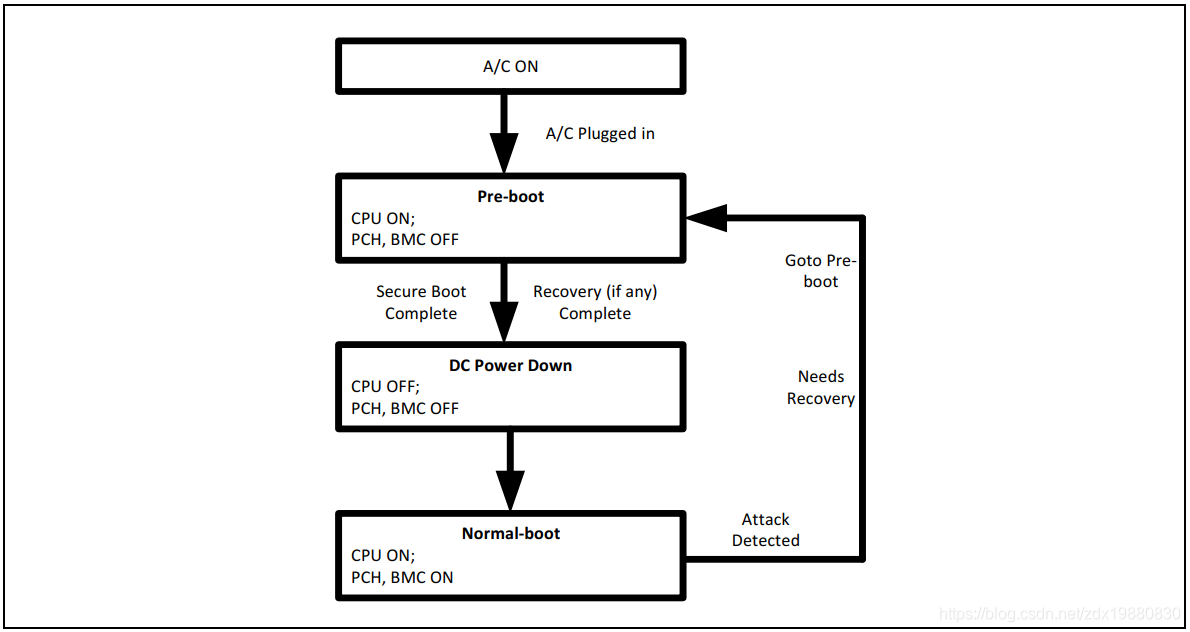

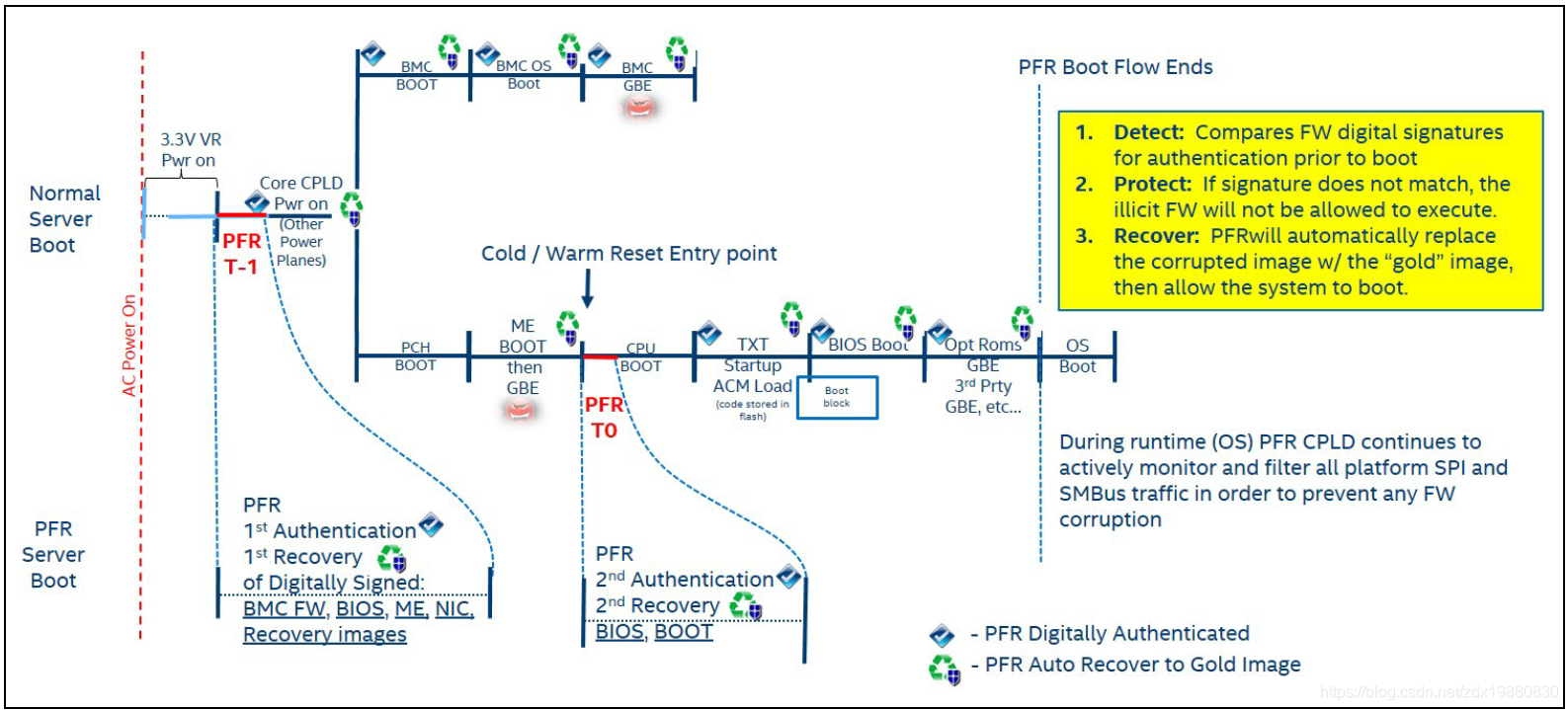

Intel PFR技術使得Intel Xeon處理器按照一種特定的預啟動模式(T-1)啟動,這種模式下,只有CPU處理啟用狀態,所有有可能干擾引導路徑(或引導操作)的其他裝置(比如PCH/ME和BMC)處於復位狀態。關鍵的引導韌體(諸如BIOS,ME,BMC等等)在T-1模式下需要數字驗證。以韌體汙染為例,一旦檢測到韌體汙染,PFR觸發一個韌體恢復事件,然後移除SPI Flash Active區域中受汙染的韌體,從Gold中拷貝一份韌體到SPI Flash Active區域。從Gold恢復拷貝中更新也是在T-1模式下執行的。一旦成功,系統繼續按照正常模式引導。

在系統執行時,諸如SPI和SMBus等關鍵匯流排,由於它們可以訪問NV儲存,因而被監控以過濾掉潛在的惡意操作和訪問。

Protect In Transit(PIT)

為了防止系統韌體在運輸途中被篡改,Intel PFR提供了多層的運輸保護機制:

- 平臺鎖定:密碼保護平臺上電

1.1 板上PFR CPLD和RF部件提供隨機密碼(PIT密碼)

1.2 PFR CPLD在平臺上電時比較PIT密碼,如果板上RF部件的密碼遺失,那麼阻止上電時序

1.3 在出貨前,從RF部件中移除密碼,這樣就可以阻止平臺在運輸中上電 - 封閉平臺韌體

2.1 在出貨前,PFR CPLD計算平臺上所有韌體的雜湊值,然後把這些雜湊值儲存到一個安全的NVRAM空間

2.2 在交付的時候,PFR CPLD重新計算平臺上所有韌體的雜湊值,如果發現有韌體的雜湊值與儲存在NVRAM中不匹配,發出告警資訊

Intel PFR硬體架構

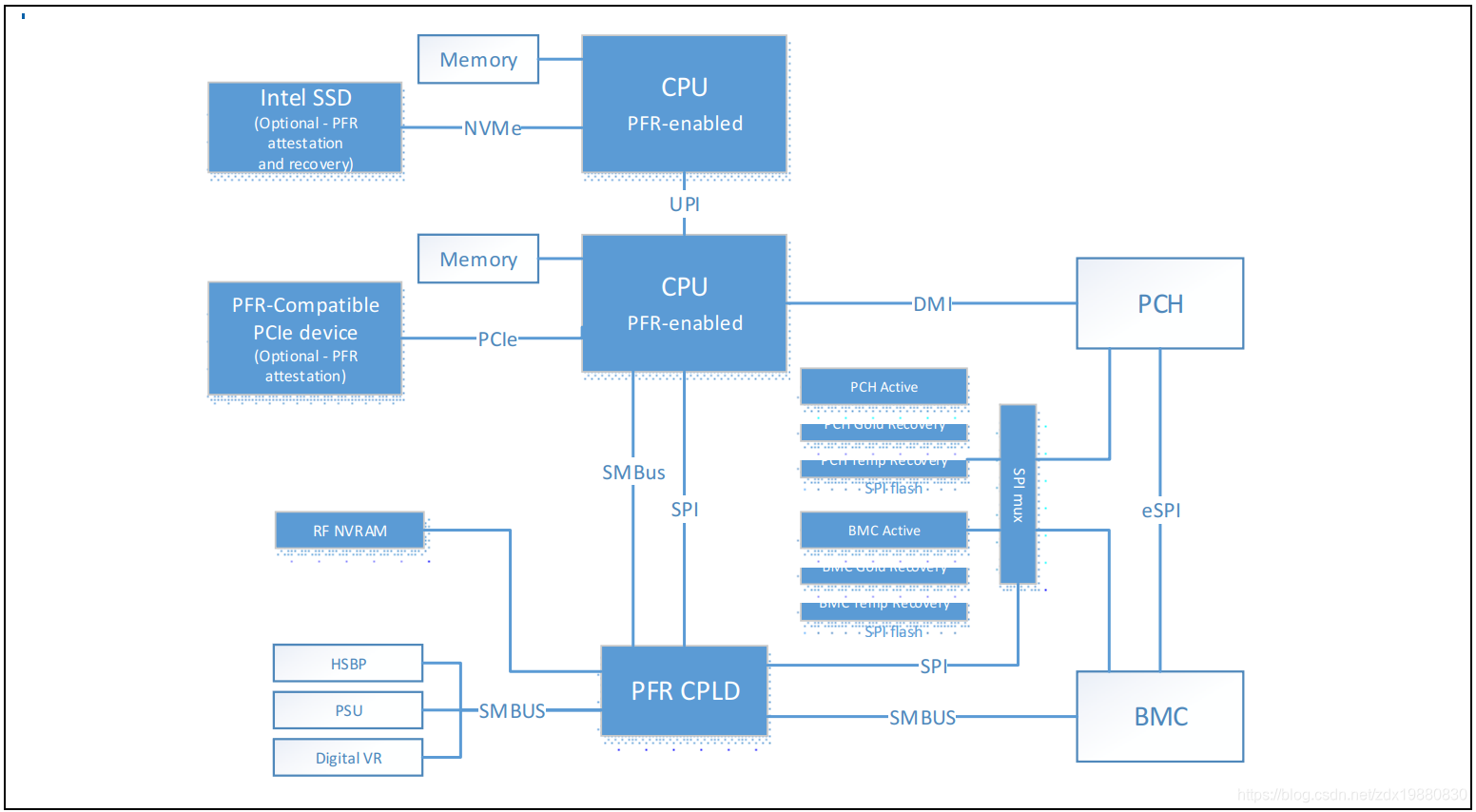

Intel PFR由如下幾個關鍵模組構成:

- PFR CPLD是Intel PFR的核心,它主要用於關鍵的監測,計算雜湊值,硬體保護,通訊介面和平臺時序

- BMC韌體Flash用於儲存BMC韌體的映象。該Flash的特定區域由PFR保護,同時該Flash也會儲存BMC的韌體恢復映象

- PCH附帶的SPI Flash用於儲存BIOS,ME和平臺其他的韌體映象。該Flash的特定區域由PFR保護,同時,它也儲存平臺上關鍵部件的韌體恢復映象

- SPI匯流排多路複用邏輯用於選擇BMC SPI和PCH SPI的主控。在PFR預啟動模式(T-1),PFR充當BMC和PCH SPI的SPI主控。在正常引導模式下(T0),BMC SPI和PCH SPI主控分別控制各自的Flash裝置

- CPU Microcode/pcode:在PFR預引導環境下,CPU的Microcode和Pcode能夠在PCH和BMC部件處於復位狀態時使能CPU的引導過程,並載入廠商程式碼模組(VCM)。它可以通過SPI介面與PFR CPLD進行最初始得通訊

- CPU授權程式碼模組(也被稱為VCM),是一段OEM自有和簽名得X86程式碼,在特殊環境下執行在CPU上。VCM儲存在PCH的SPI Flash中,由CPU Microcode通過PFR CPLD的SPI介面載入到CRAM。VCM包含了執行PFR安全引導和恢復操作的大部分程式碼

- PFR與其他預先存在的部件協助,以確保這些部件按照指定次序工作,保證PFR功能正常工作。

上圖顯示了PFR平臺架構的框圖,所有的CPU通過SPI匯流排介面連線到了PFR CPLD。SPI是CPU和PFR CPLD之間的主要通訊通道,即每顆CPU與PFR CPLD有一條SPI通道。同時在PFR CPLD和CPU還需要額外保留一條SMBus通訊介面。

PFR CPLD可以通過板上SPI多路複用器訪問PCH SPI Flash和BMC SPI Flash。PFR CPLD控制多路複用器的選通。這獲得了預引導(T-1)模式下SPI Flash的訪問。在正常引導模式(T0)下,PCH和BMC可以分別訪問它們各自的Flash裝置。Flash裝置的SPI輸入訊號也應該連線到PFR CPLD,以便允許CPLD在正常引導模式下,監控和過濾PCH和BMC下達的SPI Flash事務。BMC還可以通過SMBus訪問數字VR,熱交換背板和PSU等板上關鍵部件的韌體,這些匯流排也應該連線到PFR CPLD,以便允許PFR在正常引導和執行時監控和過濾SMBus上對這些裝置通訊事務。

為了實現可選的PIT功能,板上還需要增加RFID模組和天線。

上圖中顯示的可選的Intel SSD(支援PFR證明和恢復)以及PFR相容的PCIe裝置(支援證明)並不需要任何硬體上的變動,也不需要韌體上的變動。關於韌體的需求在其他的文件有說明。

帶有PFR的伺服器平臺互連

PFR訊號連線

如圖786顯示了Wilson City參考平臺(RP)上PFR實現的整個平臺互連。該互連僅僅適用於Wilson City,而對於其他平臺,需要系統設計者選擇合適各自平臺的實現方案。

PFR CPLD是PFR技術的核心,平臺互連以PFR CPLD為核心。與PFR互動的主要部件是Core CPLD(Core CPLD和PFR CPLD可以整合在同一個物理部件),CPU,BMC,PCH和儲存韌體的Flash裝置。PFR也提供了對平臺上諸如PSU,數字VR和高速背板保護,保護這些部件的NV儲存以及提供了一種安全更新這些部件韌體的機制。

PFR平臺引導流程

在T-1模式下,PFR CPLD可以完全訪問所有的SPI裝置。在這個階段的重要操作如下:

- 完成PCH和BMC有效區和恢復區的韌體數字簽名驗證。PFR VCM和PFR CPLD協助計算SHA256雜湊值進行驗證。它也可以檢查任何韌體是否需要更新:PCH/BMC恢復gold更新,數字VR/PSU,HSBP韌體更新等等。它通過驗證更新候選副本的真實性執行更新操作。比如,PCH或者BMC任一有效SPI Flash映象被檢測到受損,這將觸發一個恢復操作,即完整刪除有效備份,並且從最新Gold恢復區域還原。

- 一旦T-1模式下的這些安全操作成功完成,系統繼續正常引導。

帶有PFR平臺的復位Sequence

下圖顯示了開啟PFR功能的平臺復位時序。

PFR平臺支援

PFR功能開啟和禁止控制

處理器根據PFR_DISABLE Strap Pin配置決定平臺是否支援Intel PFR,從而決定處理器的動作。PFR_DISABLE在CPU內部上拉。建議:在不支援PFR功能的平臺把PFR_DISABLE Strap Pin在板上上拉。

支援PFR功能的平臺在執行時將PFR_DISABLE拉低。建議:在板卡測試前期,將PFR功能禁止掉,這意味著需要有能力把PFR_DISABLE訊號拉高。