do檔案的編寫(轉)

以前在使用ModelSim進行模擬的時候,一直是使用其GUI進行操作的,但是這樣很繁瑣也很費時。故希望學習其自動化模擬do檔案,下面是學習的一些總結。

一、編寫基本的do檔案

下面按照實際模擬的步驟來說明do檔案中需要用到的各個tcl命令。

1、quit -sim —- 退出原來的模擬工程;

2、cd —- 設定工作目錄的路徑,就是模擬工程路徑;

3、vlib work —- 在工作目錄下建立一個work目錄,請注意不要用作業系統直接新建一個work的資料夾,因為用作業系統建立的work資料夾並沒有modelsim SE自動生成的_info檔案。還有個問題是,當你的軟體工程裡需要用到軟核時,可能會需要一些庫,但這些庫ISE軟體中是沒有的,此時就需要我們自己新建庫了,並對映到當前目錄下。我們將自己新建的庫一般放在work庫前面建立;

4、vmap work /vmap work work —- 將新建的work庫對映到當前工作目錄下(當前目錄就是第一步中的目錄了),其他新建的庫也要這樣的方法對映。此處需要注意的事邏輯庫名與物理庫名最好保持一致,後面的work為物理的庫目錄,即上一步的目錄;

5、vlog +acc –work work “file_path/*.v” —- 編譯“file_path”目錄下所有.v檔案,並將其新增進工作庫(work)中,包括IP生成的V檔案也要編譯的。編譯時可以分開單獨編譯,但是一定要注意順序,先編譯被呼叫的檔案。其中的“-work work”是將後面的原始檔編譯到哪個庫中,如果是編譯到預設的work庫中,則也可以不寫該引數。若只想編譯其中某些檔案,則可以直接寫出這些檔案的名字,比如下面兩種寫法等效:

vlog div.v div_tb.v

vlog -work work div.v div_tb.v

若是要編譯基本器件庫,可參照下面的例子:

vlib verilog_libs/altera_ver

vmap altera_ver ./verilog_libs/altera_ver

vlog -vlog01compat -work altera_ver {d:/quartus9.0/quartus/eda/sim_lib/altera_primitives.v

vlog後面的兩個引數“-vlog01compat”、“-work”是固定的。其中“-work”是必須保留的,“-vlog01compat”則在原始檔為verilog檔案時可以保留,如果為VHDL檔案則不能使用該引數。需要注意的一點是該工程目錄下的“verilog_libs”庫資料夾需要手動建立,否則執行會出現錯誤。

需要編譯的檔案有兩種:原始碼檔案、庫檔案。對於庫檔案的編譯可以有兩種處理方式:

1、將這些庫檔案與原始碼檔案一起編譯到work庫中,這樣比較方便省事;

2、將庫檔案單獨編譯到一個庫中,在執行的時候需要通過引數設定來將庫選擇上。由於第一種方式較為簡單,後面將採用第二種方式。

當某一路徑會經常用到時,可以通過設定一個路徑變數來儲存該路徑,示例如下:

set LIBPATH c:/altera/11.0/quartus/eda/sim_lib/

vlib sim_lib

vmap sim_lib sim_lib

vlog -work sim_lib

vlog命令負責編譯verilog檔案,如果是VHDL檔案,則需要將vlog命令換成vcom命令。

在該命令中,如果想要include某個檔案,則可以通過vlog的incdir選項來實現,比如:

vlog +incdir+d:/work

6、vsim -novopt -quiet -c -L altera_ver -L E:/modeltech_6.6a/Xilinx_lib_edk/unimacro_ver -lib work div -t 1ns -do “run 2084655ns” —- 啟動模擬命令,該命令可以有許多引數。

引數“-L altera_ver”是新增模擬庫,該處是直接使用邏輯庫名稱,也可以像後面一樣使用物理庫的名稱及路徑;若是庫與原始檔一起編譯到work庫中的,則不需要該引數;

引數“-t 1ns”表示模擬時間單位為1ns;

引數“-novopt”禁止優化(no vopt),可能會因為vopt的緣故使得一些不重要signal被modelsim自動忽略,一般會保留該引數;

引數“-do”表示執行時間,該引數一般不用,在後面再執行該命令;

引數“-c”表示進入命令列模式,如果沒有該引數,則表示進行GUI模式。

預設工作庫為work,因而下面幾種寫法等效:

vsim div_tb

vsim -lib work div_tb

vsim work.div_tb

sim -L D:/Modelsim/Installfiles/altera/altera_mf work.videoin_tb

7、view signals source wave —- 開啟signal、source、wave視窗,也可以只打開wave視窗;

8、delete wave * —- 刪除原來wave視窗中的波形;

9、add wave -binary clk rst —- 打新增要觀察的波形訊號,clk、rst為tb的頂層訊號名,若要新增內部訊號則要給出路徑,-binary表示使用二進位制顯示;

新增一個模組的所有訊號則可以用下面的方式:

add wave -dec sim:/div_tb/*

若只是要新增單個訊號,則把“*”換成對應的訊號即可,比如:

add wave -unsigned sim:/div_tb/clk

在wave視窗中,可以對波形進行相關配置,下面是常用的配置命令:

WaveRestoreCursors {{Cursors 1} {200ns} 0} {{Cursors 2} {400ns} 0}

configure wave -rowmargin 4

configure wave -childrowmargin 2

configure wave -namecolwidth 150

configure wave -valuecolwidth 100

configure wave -signalnamewidth 0

configure wave -justifyvalue left

configure wave -snapdistance 10

configure wave -datasetprefix 0

configure wave -gridoffset 0

configure wave -gridperiod 1

configure wave -griddelta 40

configure wave -timeline 0

update

WaveRestoreZoom {0 ns} {1000 ns}

如果所有訊號均採用同一種方式顯示,則可以用如下方式設定,就不必要在每次新增訊號時設定顯示引數:

radix -hex

10、run 5000/run @5000 —- 開始執行模擬程式;

沒有“@”則表示在當前時刻繼續執行5000個單位時間;

有“@”則表示執行到5000這個時刻,如果當前程式模擬已經執行到了5000以後的時刻,則該方法不會繼續向後執行,而會彈出一個錯誤資訊,提示當前模擬時刻已經超過了該數值。

run -all則表示一直執行,直到手動停止。

在5000後面也可以跟上一個單位,不跟單位時則以模擬的最小單位為基準。

11、quit -f/quit -sim —- 引數為“f”時則結束ModelSim,引數為“sim”時則結束該模擬程序。

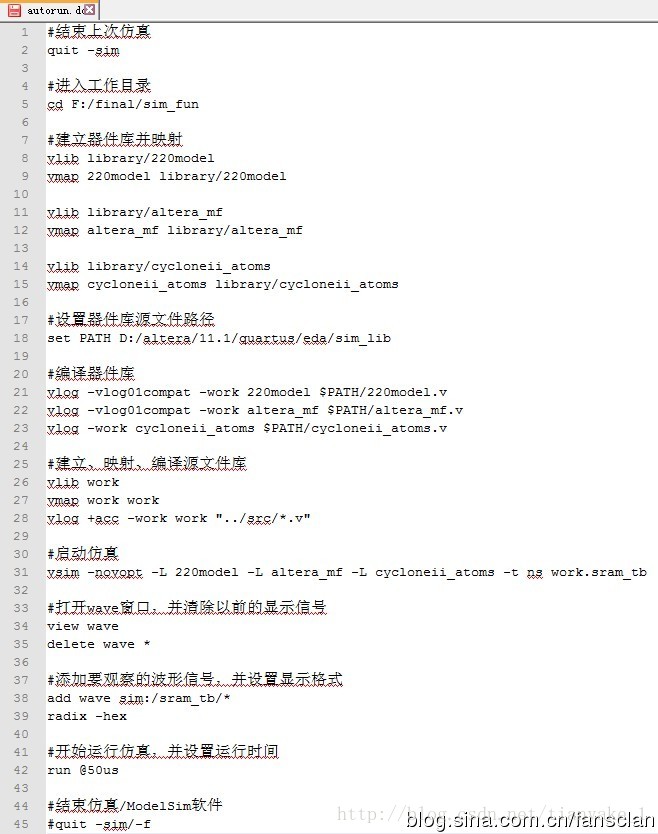

下圖是我寫的一個do檔案的截圖,能夠正確執行。

這裡只是編寫了基本的do檔案,需要在ModelSIm的Transcipts視窗輸入相應的命令才可以執行。

1、cd filepath —-進入do檔案所在的目錄;

2、do filename.do —-執行do檔案,開始模擬。

二、進行優化

還可以對上面的流程進行優化,真正達到自動模擬,使得模擬更有效率。

1、批處理bat檔案 —- 直接執行該檔案即可啟動模擬,而不需要首先進入ModelSim啟動do檔案;該方法還未實驗成功。

2、單獨的檔案儲存檔案路徑 —-當有多個不同的檔案路徑時,為使do檔案更加簡潔,可以將所有路徑儲存在一個檔案中。該方法也未實驗成功。

我是按照Modelsim中常用的Tcl命令中的方法實驗的,以後有時間再來看看怎麼弄這個。

三、互動式命令

通過在主視窗的命令視窗輸入命令來實現,具有更好的除錯和互動功能,提供多種指令,既可以是單步指令,也可以構成批處理檔案,用來控制編輯、編譯和模擬流程。

1、force-repeat

指令格式:force 開始時間開始電平值,結束電平值忽略時間(即0電平保持時間) -repeat 週期

force clk 0 0,1 30 -repeat 100 表示強制clk從0時間單元開始,起始電平為0,結束電平為1,0電平保持時間為30個預設時間單元,週期為100個預設時間單元,佔空比為70%。

指令功能:每隔一段的週期重複一定的force命令,用來產生時鐘訊號,也可用來產生週期的輸入訊號,如01010101,00110011等。

2、force

指令格式:force item_name value time,value time;item_name為埠訊號或內部訊號,支援萬用字元號,但只能匹配一個;value不能預設,time,可選項,支援時間單元; force din 16#40900000 從當前時刻起給din賦值16進位制40900000; force bus 16#F @100ns 在100ns時刻給bus賦值16進位制F; force clr 1 100 經歷100個預設時間單元延遲後為clr賦值1;

force clr 1,0 100 表示clr賦值1後,經歷100個預設時間單元延遲後為clr賦值為0。

3、run

指令格式:run timestepstime_unit,timesteps時間步長,time_unit時間單元,可以是fs、ps、ns、us、ms、sec;

指令功能:執行(模擬)並指定時間及單元;

run 100,表示執行100個預設時間單元;

run 2500ns,表示執行2500ns;

run -all,表示執行全過程;

run -continue,表示繼續執行。

4、force-cancel

指令格式:force-cancel period

指令功能:執行period週期時間後取消force命令;

force clk 0 0,1 30 -repeat 60-cancel 1000,表示強制clk從0時刻開始,直到1000個時間單元結束。

5、view

指令格式:view 視窗名

指令功能:開啟Modelsim的視窗

view souce,開啟原始碼視窗;

view wave,開啟波形視窗;

view list,開啟列表視窗;

view varibles,開啟變數視窗;

view signals,開啟訊號視窗;

view all,開啟所有視窗。