Tsetup和Thold的經典問題 & max fanout的解決辦法

Tsetup和Thold的經典問題

有個著名的筆試題,這樣說道:時鐘週期為T,觸發器D1的建立時間最大為T1max,最小為T1min,該觸發器的資料輸出延時為Tco。組合邏輯電路最大延遲為T2max,最小為T2min。假設D1在前,D2去取樣D1的資料(實際就是對圖2的文字描述),問,觸發器D2的建立時間T3和保持時間應滿足什麼條件。這裡給出一個簡易公式供大家死記一下,

以下兩個公式確定了D2的Tsetup和Thold:下面兩個公式可以在我的這篇部落格中找到更詳細的答案。

https://blog.csdn.net/weixin_43343190/article/details/82960601

1、D1的Tco+ max資料鏈路延時+ D2的Tsetup< T(即T3 < T - Tco - T2max)

2、D1的Tco+ min資料鏈路延時> D2的Thold(即T4< Tco+ T2min)

其實上面的式2可以從T3+T4=T推出,不過要注意把1)中的T2max改為T2min即可。

總之,建立時間長了,保持時間就短了。

實際中,某條資料鏈路延時是一個定值,只不過要求它落在區間{T2min,T2max}。這也是T2min和T2max的實際意義。

看完上述,應該可以回答以下問題了:

1、為什麼模擬時,更看重MAX,較輕看重MIN?

答:根據上述最後的兩個公式,邏輯路徑的MAX和setup有關,有可能不滿足要求,需要模擬驗證;而MIN和hold有關,hold的公式易滿足。

2、 為什麼模擬時,更看重setup,較輕看重hold?

答:原理同上。

3、 邏輯路徑延時的範圍要求,怎麼計算?

答:根據上述的最後兩個公式,可以計算。

4、 非同步不好,時序方面的原因?

答:非同步導致時鐘的不穩定,會產生Tpd,上述的兩個公式加入Tpd後會有影響,尤其是hold

5、 setup,hold不滿足要求時怎麼辦?

答:根據公式,hold不滿足要求時,增加邏輯路徑延時,即加buffer。

Setup不滿足要求時,優化路徑,減小延時。

扇入和扇出,延時,解決辦法

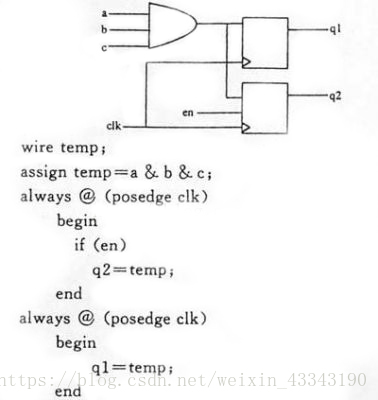

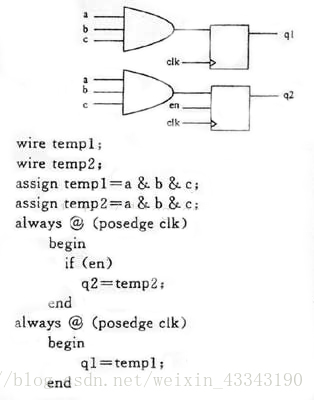

max fanout(最大扇出)主要指的是定義該訊號最多驅動多少個訊號,max fanin 是指連線到該門輸入的數目;扇出越大,延遲越大,解決方法:電路複製。

例子:

如果一個扇出大於1的組合邏輯不能在CLB內部實現,這時需要對組合邏輯進行復制。下面給出組合邏輯複製的例子。