STM32中GPIO的8種工作模式 轉載

有關推輓輸出、開漏輸出、複用開漏輸出、複用推輓輸出,以及上拉輸入、下拉輸入、浮空輸入、模擬輸入的區別

最近在看資料手冊的時候,發現在Cortex-M3裡,對於GPIO的配置種類有8種之多:

(1)GPIO_Mode_AIN 模擬輸入 (2)GPIO_Mode_IN_FLOATING 浮空輸入 (3)GPIO_Mode_IPD 下拉輸入 (4)GPIO_Mode_IPU 上拉輸入 (5)GPIO_Mode_Out_OD 開漏輸出 (6)GPIO_Mode_Out_PP 推輓輸出 (7)GPIO_Mode_AF_OD 複用開漏輸出 (8)GPIO_Mode_AF_PP 複用推輓輸出 對於剛入門的新手,我想這幾個概念是必須得搞清楚的,平時接觸的最多的也就是推輓輸出、開漏輸出、上拉輸入這三種,但一直未曾對這些做過歸納。因此,在這裡做一個總結:

推輓輸出:可以輸出高,低電平,連線數字器件; 推輓結構一般是指兩個三極體分別受兩互補訊號的控制,總是在一個三極體導通的時候另一個截止。高低電平由IC的電源低定。

推輓電路是兩個引數相同的三極體或MOSFET,以推輓方式存在於電路中,各負責正負半周的波形放大任務,電路工作時,兩隻對稱的功率開關管每次只有一個導通,所以導通損耗小、效率高。輸出既可以向負載灌電流,也可以從負載抽取電流。推拉式輸出級既提高電路的負載能力,又提高開關速度。

詳細理解:

如圖所示,推輓放大器的輸出級有兩個“臂”(兩組放大元件),一個“臂”的電流增加時,另一個“臂”的電流則減小,二者的狀態輪流轉換。對負載而言,好像是一個“臂”在推,一個“臂”在拉,共同完成電流輸出任務。當輸出高電平時,也就是下級負載門輸入高電平時,輸出端的電流將是下級門從本級電源經VT3拉出。這樣一來,輸出高低電平時,VT3 一路和 VT5 一路將交替工作,從而減低了功耗,提高了每個管的承受能力。又由於不論走哪一路,管子導通電阻都很小,使RC常數很小,轉變速度很快。因此,推拉式輸出級既提高電路的負載能力,又提高開關速度。

如圖所示,推輓放大器的輸出級有兩個“臂”(兩組放大元件),一個“臂”的電流增加時,另一個“臂”的電流則減小,二者的狀態輪流轉換。對負載而言,好像是一個“臂”在推,一個“臂”在拉,共同完成電流輸出任務。當輸出高電平時,也就是下級負載門輸入高電平時,輸出端的電流將是下級門從本級電源經VT3拉出。這樣一來,輸出高低電平時,VT3 一路和 VT5 一路將交替工作,從而減低了功耗,提高了每個管的承受能力。又由於不論走哪一路,管子導通電阻都很小,使RC常數很小,轉變速度很快。因此,推拉式輸出級既提高電路的負載能力,又提高開關速度。

開漏輸出:輸出端相當於三極體的集電極. 要得到高電平狀態需要上拉電阻才行. 適合於做電流型的驅動,其吸收電流的能力相對強(一般20ma以內).

開漏形式的電路有以下幾個特點:

1. 利用外部電路的驅動能力,減少IC內部的驅動。當IC內部MOSFET導通時,驅動電流是從外部的VCC流經R pull-up ,MOSFET到GND。IC內部僅需很下的柵極驅動電流。

2. 一般來說,開漏是用來連線不同電平的器件,匹配電平用的,因為開漏引腳不連線外部的上拉電阻時,只能輸出低電平,如果需要同時具備輸出高電平的功能,則需要接上拉電阻,很好的一個優點是通過改變上拉電源的電壓,便可以改變傳輸電平。比如加上上拉電阻就可以提供TTL/CMOS電平輸出等。(

3. OPEN-DRAIN提供了靈活的輸出方式,但是也有其弱點,就是帶來上升沿的延時。因為上升沿是通過外接上拉無源電阻對負載充電,所以當電阻選擇小時延時就小,但功耗大;反之延時大功耗小。所以如果對延時有要求,則建議用下降沿輸出。

4. 可以將多個開漏輸出的Pin,連線到一條線上。通過一隻上拉電阻,在不增加任何器件的情況下,形成“與邏輯”關係。這也是I2C,SMBus等匯流排判斷匯流排佔用狀態的原理。補充:什麼是“線與”?:

在一個結點(線)上, 連線一個上拉電阻到電源 VCC 或 VDD 和 n 個 NPN 或 NMOS 電晶體的集電極 C 或漏極 D, 這些電晶體的發射極 E 或源極 S 都接到地線上, 只要有一個電晶體飽和, 這個結點(線)就被拉到地線電平上. 因為這些電晶體的基極注入電流(NPN)或柵極加上高電平(NMOS), 電晶體就會飽和, 所以這些基極或柵極對這個結點(線)的關係是或非 NOR 邏輯. 如果這個結點後面加一個反相器, 就是或 OR 邏輯.

其實可以簡單的理解為:在所有引腳連在一起時,外接一上拉電阻,如果有一個引腳輸出為邏輯0,相當於接地,與之並聯的迴路“相當於被一根導線短路”,所以外電路邏輯電平便為0,只有都為高電平時,與的結果才為邏輯1。

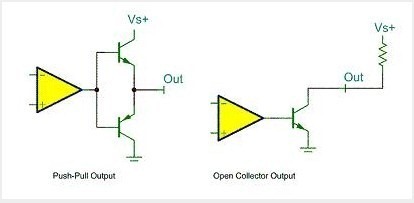

關於推輓輸出和開漏輸出,最後用一幅最簡單的圖形來概括:

該圖中左邊的便是推輓輸出模式,其中比較器輸出高電平時下面的PNP三極體截止,而上面NPN三極體導通,輸出電平VS+;當比較器輸出低電平時則恰恰相反,PNP三極體導通,輸出和地相連,為低電平。右邊的則可以理解為開漏輸出形式,需要接上拉。

該圖中左邊的便是推輓輸出模式,其中比較器輸出高電平時下面的PNP三極體截止,而上面NPN三極體導通,輸出電平VS+;當比較器輸出低電平時則恰恰相反,PNP三極體導通,輸出和地相連,為低電平。右邊的則可以理解為開漏輸出形式,需要接上拉。

浮空輸入:對於浮空輸入,一直沒找到很權威的解釋,只好從以下圖中去理解了

由於浮空輸入一般多用於外部按鍵輸入,結合圖上的輸入部分電路,我理解為浮空輸入狀態下,IO的電平狀態是不確定的,完全由外部輸入決定,如果在該引腳懸空的情況下,讀取該埠的電平是不確定的。

上拉輸入/下拉輸入/模擬輸入:這幾個概念很好理解,從字面便能輕易讀懂。

複用開漏輸出、複用推輓輸出:可以理解為GPIO口被用作第二功能時的配置情況(即並非作為通用IO口使用)

最後總結下使用情況:

在STM32中選用IO模式 (1) 浮空輸入_IN_FLOATING ——浮空輸入,可以做KEY識別,RX1 (2)帶上拉輸入_IPU——IO內部上拉電阻輸入 (3)帶下拉輸入_IPD—— IO內部下拉電阻輸入 (4) 模擬輸入_AIN ——應用ADC模擬輸入,或者低功耗下省電 (5)開漏輸出_OUT_OD ——IO輸出0接GND,IO輸出1,懸空,需要外接上拉電阻,才能實現輸出高電平。當輸出為1時,IO口的狀態由上拉電阻拉高電平,但由於是開漏輸出模式,這樣IO口也就可以由外部電路改變為低電平或不變。可以讀IO輸入電平變化,實現C51的IO雙向功能 (6)推輓輸出_OUT_PP ——IO輸出0-接GND, IO輸出1 -接VCC,讀輸入值是未知的 (7)複用功能的推輓輸出_AF_PP ——片內外設功能(I2C的SCL,SDA) (8)複用功能的開漏輸出_AF_OD——片內外設功能(TX1,MOSI,MISO.SCK.SS) STM32設定例項: (1)模擬I2C使用開漏輸出_OUT_OD,接上拉電阻,能夠正確輸出0和1;讀值時先GPIO_SetBits(GPIOB, GPIO_Pin_0);拉高,然後可以讀IO的值;使用GPIO_ReadInputDataBit(GPIOB,GPIO_Pin_0); (2)如果是無上拉電阻,IO預設是高電平;需要讀取IO的值,可以使用帶上拉輸入_IPU和浮空輸入_IN_FLOATING和開漏輸出_OUT_OD;

通常有5種方式使用某個引腳功能,它們的配置方式如下: 1)作為普通GPIO輸入:根據需要配置該引腳為浮空輸入、帶弱上拉輸入或帶弱下拉輸入,同時不要使能該引腳對應的所有複用功能模組。 2)作為普通GPIO輸出:根據需要配置該引腳為推輓輸出或開漏輸出,同時不要使能該引腳對應的所有複用功能模組。 3)作為普通模擬輸入:配置該引腳為模擬輸入模式,同時不要使能該引腳對應的所有複用功能模組。 4)作為內建外設的輸入:根據需要配置該引腳為浮空輸入、帶弱上拉輸入或帶弱下拉輸入,同時使能該引腳對應的某個複用功能模組。 5)作為內建外設的輸出:根據需要配置該引腳為複用推輓輸出或複用開漏輸出,同時使能該引腳對應的所有複用功能模組。 注意如果有多個複用功能模組對應同一個引腳,只能使能其中之一,其它模組保持非使能狀態。

比如要使用STM32F103VBT6的47、48腳的USART3功能,則需要配置47腳為複用推輓輸出或複用開漏輸出,配置48腳為某種輸入模式,同時使能USART3並保持I2C2的非使能狀態。

如果要使用STM32F103VBT6的47腳作為TIM2_CH3,則需要對TIM2進行重對映,然後再按複用功能的方式配置對應引腳。