利用ZYNQ SOC快速開啟演算法驗證通路(6)——利用AXI匯流排實時配置sysGen子系統

利用ZYNQ驗證演算法的一大優勢在於,可以在上位機發送指令藉助CPU的控制能力和C語言易開發特點,實時配置演算法模組的工作模式、引數等對來對其演算法模組效能進行全面的評估。最重要的是無需重新綜合硬體模組。

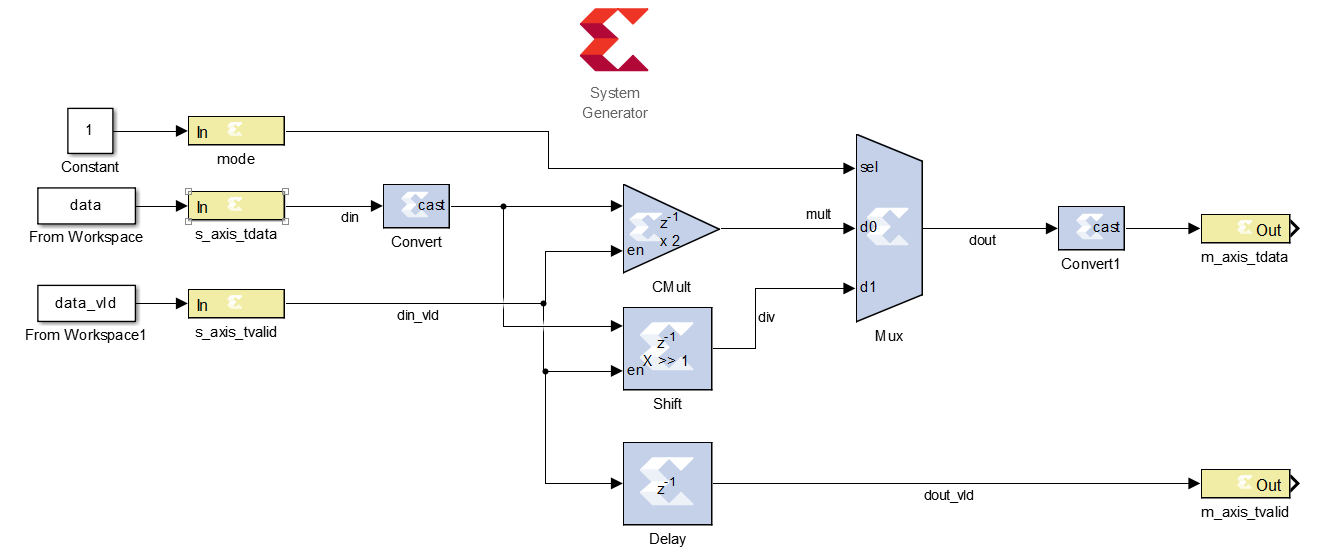

接著上篇該系列博文,在sysGen中設計模組功能為:根據模式選擇輸入,來完成乘2或除2兩種運算,0乘1除。

測試激勵選用From Workspace模組,從MATLAB工作空間匯入資料。利用MALTAB指令碼可以非常容易地生成任意資料集,極大體現了sysGen開發的優勢。

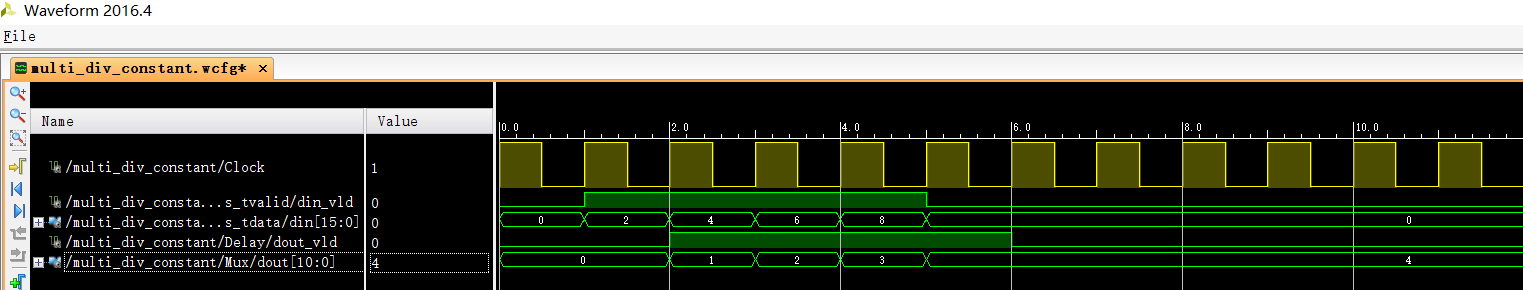

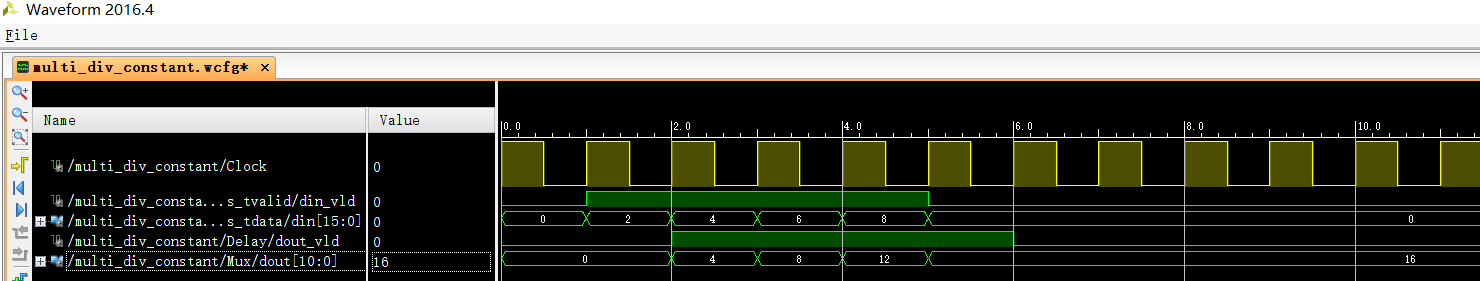

設計完成呼叫xilinx waveform viewer,兩種運算行為模擬波形如下:

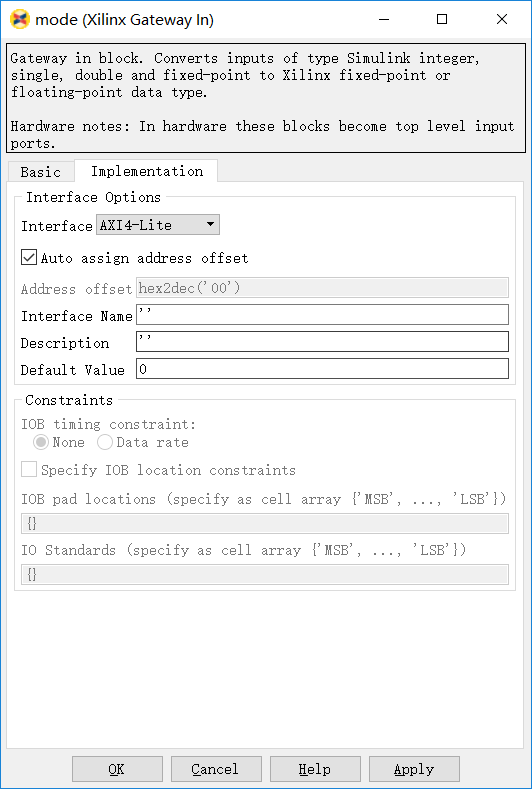

功能驗證無誤,關鍵的一點是讓mode埠以AXI匯流排形式傳遞資料。

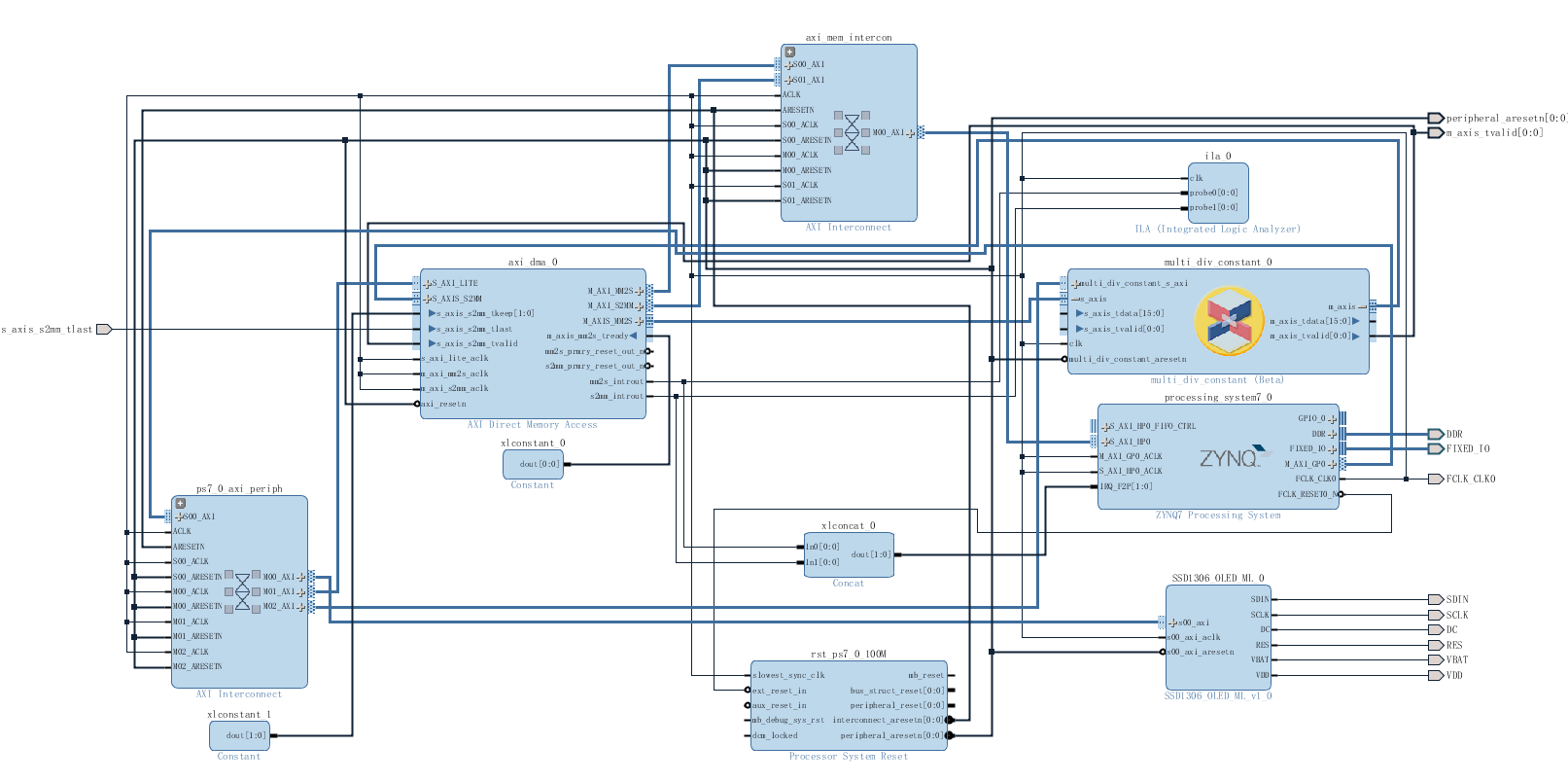

現在將sysGen演算法子系統生成IP核,並匯出到IP Integrator中作為CPU外設。

可以看到multi_div_constant模組多出一個multi_div_constant_s_axi匯流排介面集。這裡本人有個疑問:為什麼sysGen中選擇mode介面服從AXI-Lite匯流排形式,而生成的介面卻為AXI-Full形式?雖然不影響使用,也希望有看到的朋友幫忙解答這個疑惑。

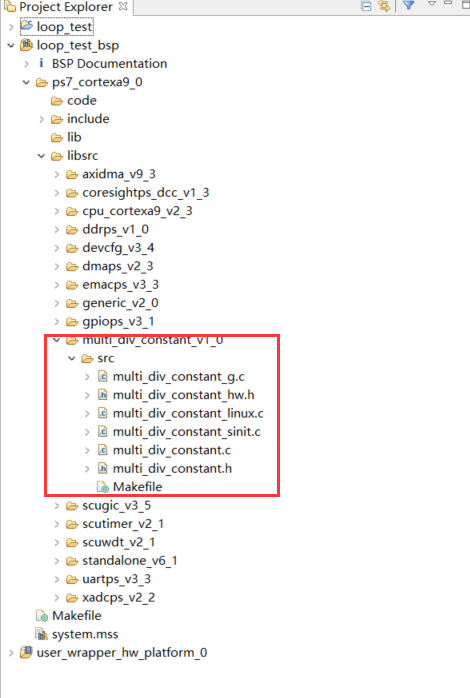

硬體系統設計完畢,匯出硬體啟動SDK。當新建工程後,能看到AXI匯流排驅動自動新增進來了。

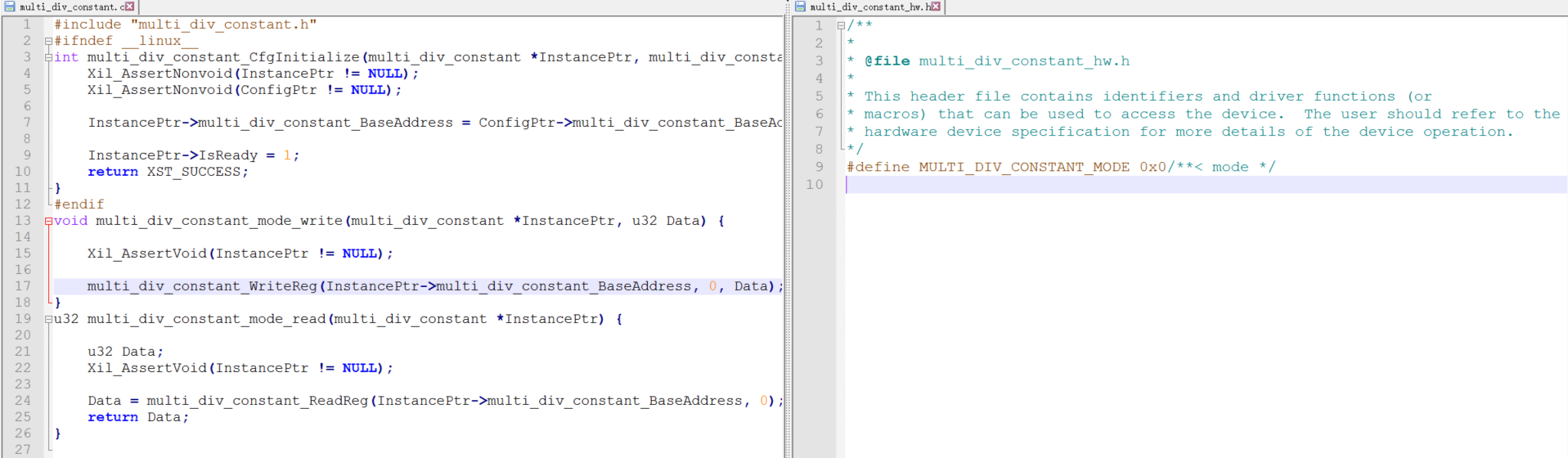

multi_div_constant_hw.h內部為AXI-Lite匯流排暫存器地址,multi_div_constant.c內是驅動函式的具體實現。

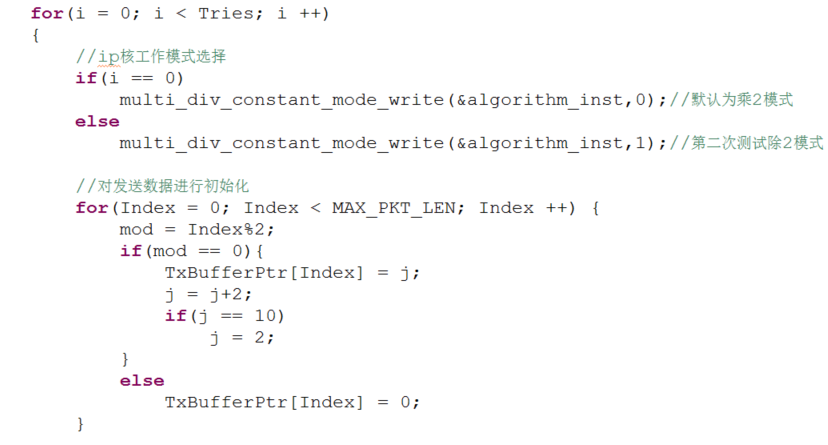

C程式碼對演算法模組進行板級驗證:

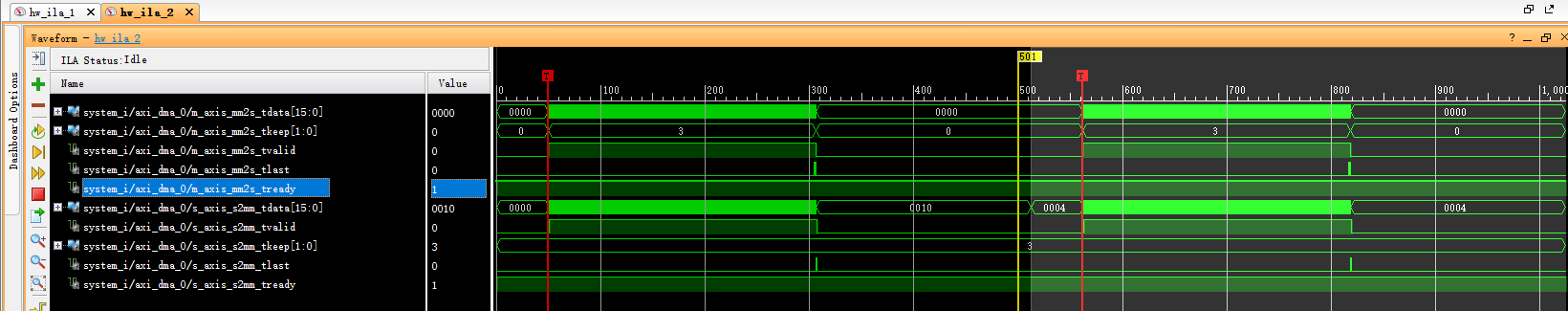

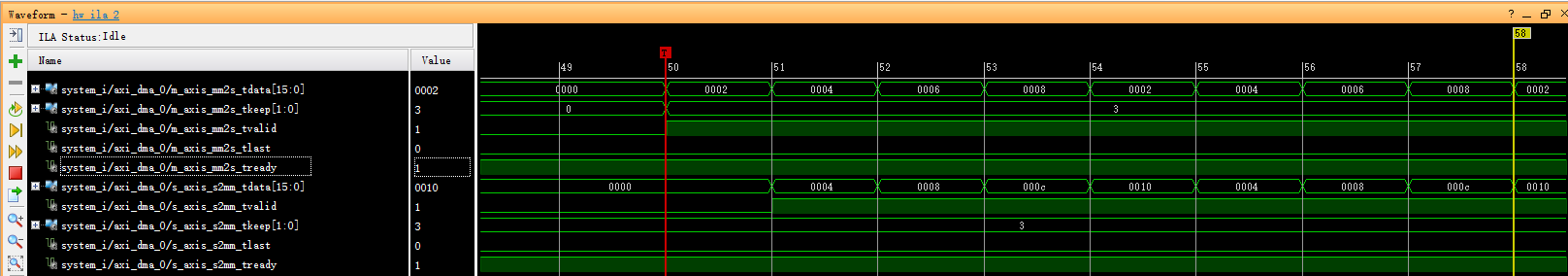

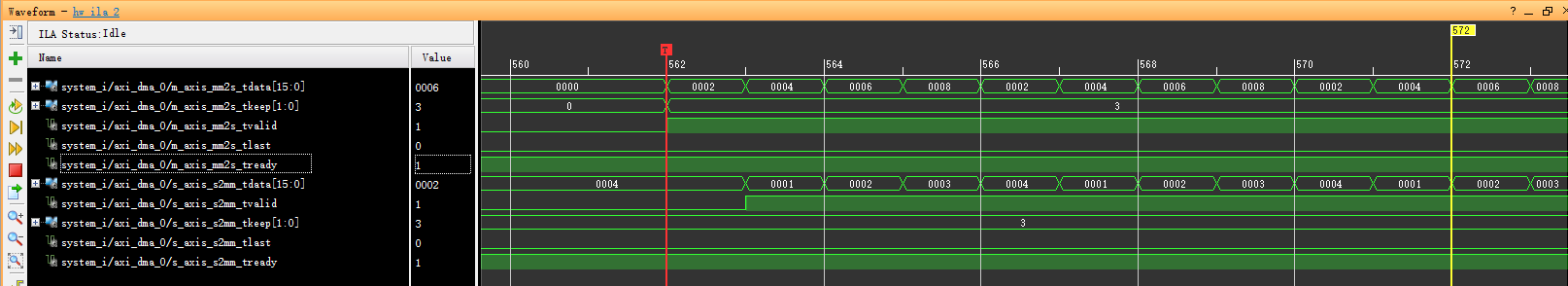

啟動Debug,點選執行檢視軟體執行結果和AXI-Stream匯流排時序波形。

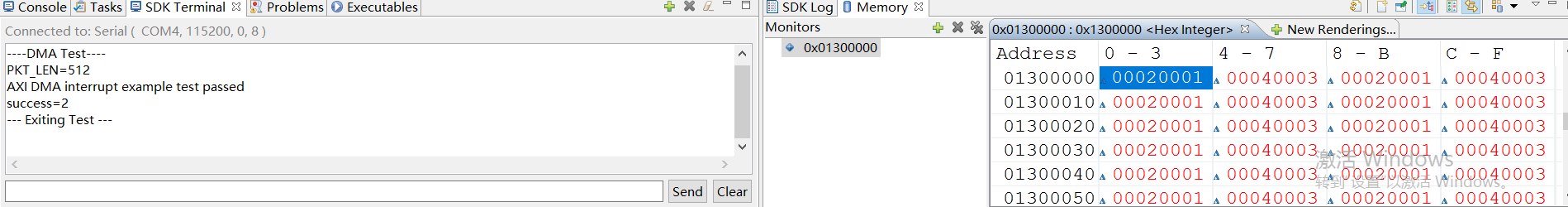

SDK中串列埠列印結果及Memory視窗檢視DDR接收快取絕對地址。

正確啟動了兩次DMA環回傳輸,第一次演算法模組工作在乘2模式,第二次則除2.C程式碼中測試返回資料與生成測試資料關係無誤,DDR絕對地址資料也別正確更新。