計算機組成與體系結構

阿新 • • 發佈:2018-12-10

計算機體系結構分類

| 體系結構型別 | 結構 | 關鍵特性 | 代表 |

|---|---|---|---|

| 單指令流單資料流SISD |

控制部分:一個 處 理 器:一個 主存模組:一個 |

單處理器系統 |

|

| 單指令流多資料流SIMD |

控制部分:一個 處理器:多個 主存模組 |

各處理器以非同步的形式執行同一條指令 |

並行處理機 陣列處理機 超級向量處理機 |

| 多指令流單資料流MISD |

控制部分:多個 處理器:一個 主存模組:多個 |

被證明不可能,至少是不實際 | 目前沒有,有文獻稱流水線計機為此類 |

|

多指令多資料流MIMD |

控制部分:多個 處理器:多個 主存模組:多個 |

能夠實現作業、任務、指令各級全面並行 |

多處理機系多計算機 |

CISC與RISC

| 批令系統型別 | 指令 | 定址方式 | 實現方式 | 其它 |

|---|---|---|---|---|

| CISC(複雜) | 數量多,使用頻率差別大,可變長格式 | 支援多種 | 微程式控制技術(微碼) | 研製週期長 |

| RISC(精簡) | 數量少,使用頻率接近,定長格式,大部分為單週期指令,操作暫存器,中有Load/Store操作記憶體 | 支援方式 少 | 增加了能用暫存器;適合採用流水線 | 優化編譯,有效支援高階語言 |

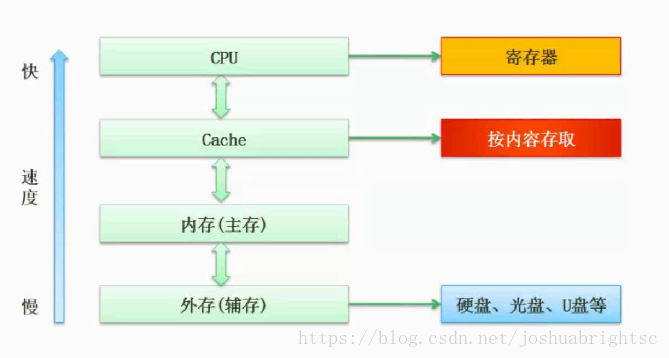

層次化儲存結構

Cache - 概念

Cache的功能:提高CPU資料輸入輸出的速率,突破馮·諾依曼瓶頸即CPU與儲存系統間資料傳關頻寬限制。

在計算機的儲存系統體系,Cache是訪問速度最快的層次。

使用Cache改善系統性能的依據是程式的區域性性原理

如果以h代表Cache的訪問命中率,t1表表Cache的週期時間,t2表示主儲存器週期時,以讀操作為例,使用“Cache+主儲存器”的統平均週期為t3.則:其中(1-h)又稱為失效率(未命中率)

區域性性原理

時間區域性性

空間區域性性

工作集理論:工作集是程序執行時被頻繁訪問的頁面集合

int i,s = 0

for (i=1;i<1000;i++){

for(i=i;j<1000;j++){

s+=j;

}

}

printf("結果為:%d",s)主存-分類

| 只讀儲存器 | 隨機存取儲存器 |

| MROM(Mask ROM, 掩模式ROM) | DRAM(Dynamic RAM,動態RAM)- SDRAM |

| RPOM(Rrogramable ROM,一次可程式設計 ROM) |

SRAM(Static RAM,靜態) |

| EROM(Erasable PROM,可擦除的PROM) | |

| 閃速儲存器(flash memory,快閃記憶體) |

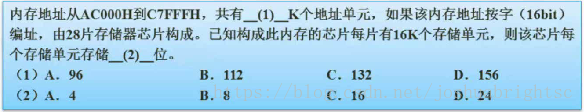

主存-編址

答案:B A

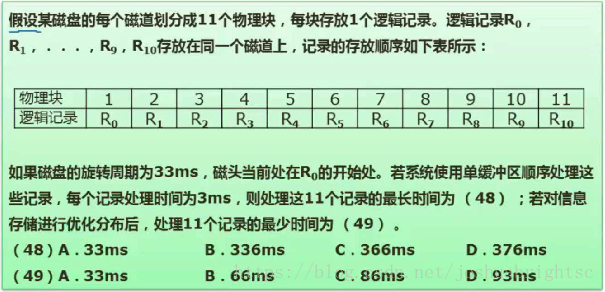

磁碟結構與引數

存取時間 = 尋道時間+等待時間(平均定位時間+轉動延遲)

注意:尋道時間是指磁頭移動到磁軌所需的時間:等待時間為等待讀寫的扇區轉到磁頭下方所用的時間。

答案:C B