【原創】建立與保持時間裕量詳細分析

筆者這段時間在找工作中發現,關於時序分析的基礎概念,時序關係表示式及時序違例計算幾乎是每個IC/FPGA崗位筆試面試的必考內容。就此,從建立保持時間裕量出發,夯實基礎。本文主要是對之前轉載部落格【時序約束學習筆記1】Vivado入門與提高--第12講 時序分析中的基本概念和術語 做一些總結和個人理解。

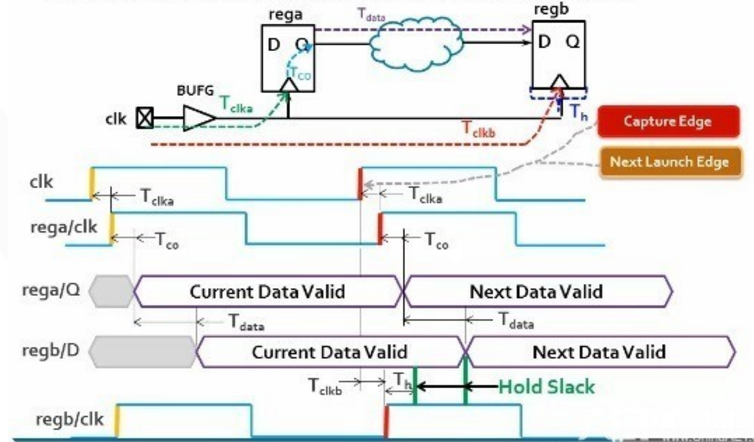

還是直接用之前轉載部落格中圖片:

圖中的兩個暫存器中間加一段組合邏輯電路是時序分析的經典模型,主時鐘clk前後兩個上升沿分別叫啟動沿和鎖存沿,是時序分析的起點和終點。下邊一步步推匯出建立時間和保持時間裕量及常用通式。要注意,下邊的“時間”均表示一個時刻。且為了方便,將啟動沿時刻定義為0時刻,故鎖存沿為T時刻。

1 時鐘到達時間:時鐘有效沿到達帶二個暫存器的時刻。

Tcd = capature Edge + Tclkb = T + Tclkb

2 資料到達時間:資料到達第二個暫存器的時刻。

Tdd = launch Edge + Tclka + Tco + Tdata = Tclka + Tco + Tdata

3 資料需求時間(建立時間需求):為滿足建立時間要求,資料最晚到達的時刻。

Tsu,req = Tcd - Tsu = T+ Tclkb - Tsu

4 資料需求時間(保持時間需求):為了滿足保持時間要求,資料最早更新的時刻。

Th,req = Tcd + Th = T + Tclkb + Th

5 建立時間裕量:為滿足建立時間要求,富餘出來的時間段長度。

setup slack = 建立時間需求 - 資料到達時間

= Tdd - Tsu,req = T+ Tclkb - Tsu - Tclka - Tco - Tdata

= T + T△ - Tco - Tdata - Tsu

6 保持時間裕量:為了滿足保持時間要求,富餘出來的時間長度。

hold slack = 資料到達時間(下一次)- 保持時間需求

= Tdd' - Th,req = Tclka + Tco + Tdata + T - T - Tclkb - Th

= -T△ + Tco + Tdata - Th

同步數位電路就係統中,每條時序路徑必須滿足建立時間裕量和保持時間裕量 ≥ 0,否則無法滿足建立與保持時間要求,引起系統不穩定甚至無法正常工作。常用通式(不考慮時鐘偏抖):

1 通過建立時間裕量引出系統最高時鐘頻率

setup slack≥0:T - Tco - Tdata - Tsu ≥ 0 -->T ≥ Tco + Tdata + Tsu

2 通過保持時間裕量得到保持時間與時序引數關係

hold slack≥0:-T△ + Tco + Tdata - Th ≥ 0 --> Th ≤ Tco + Tdata

還不趕緊背下來!