STM32CubeMX學習筆記——STM32H743_DRAM

阿新 • • 發佈:2018-12-11

STM32CubeMX學習筆記——STM32H743_DRAM

Github

https://github.com/HaHaHaHaHaGe/Planof2019_half/tree/master/Course_Project/STM32H7/Class05_SDRAM

功能簡述

移植原子的W9825G6KH初始化、讀寫函式並配合STM32CubeMX的測試專案,可以進行讀寫

STM32CubeMX配置

STM32CubeMX版本:4.27.0

配置流程:

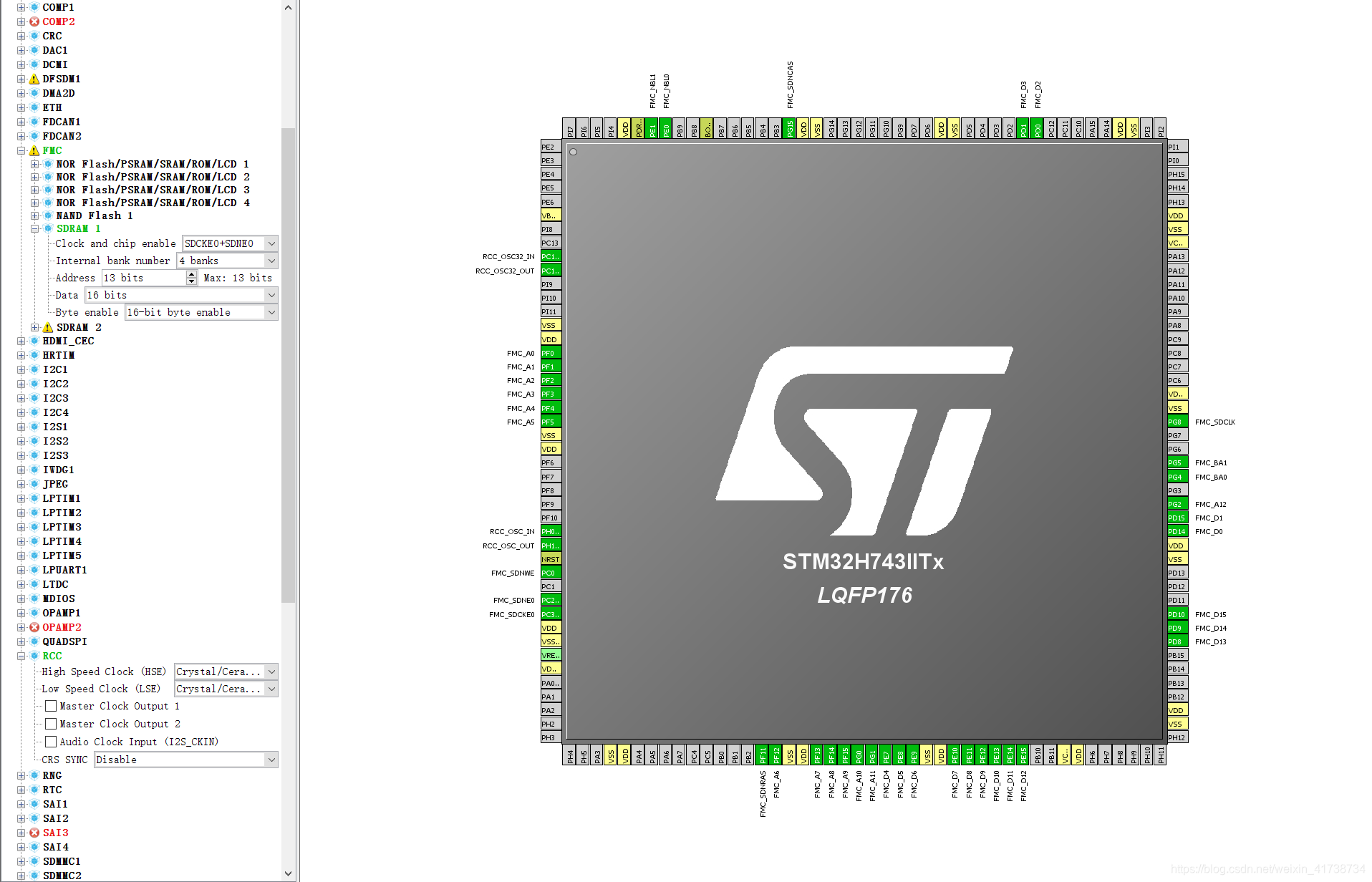

Pinout介面選擇並開啟FMC與RCC

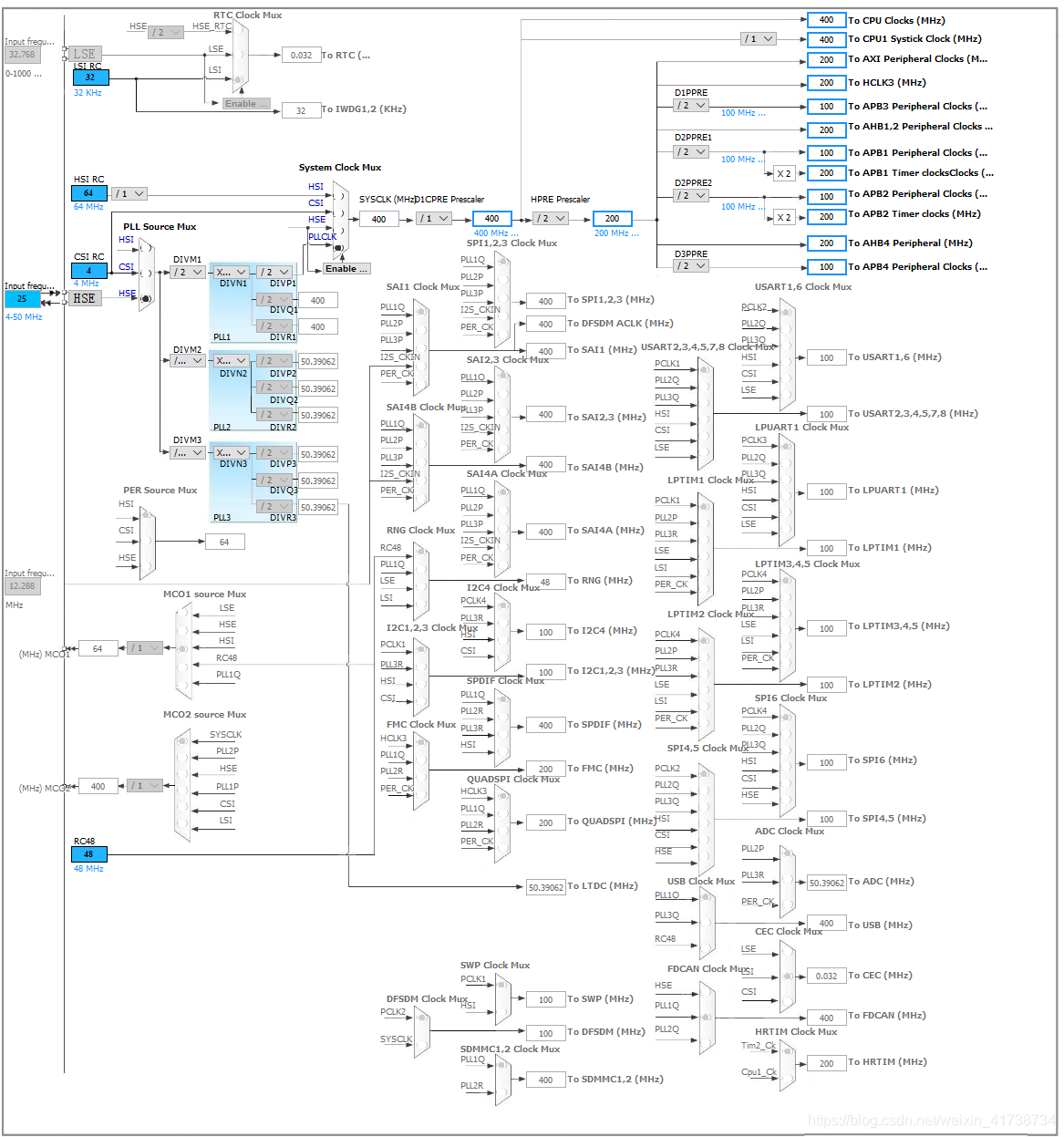

Clock Configuration配置時鐘樹

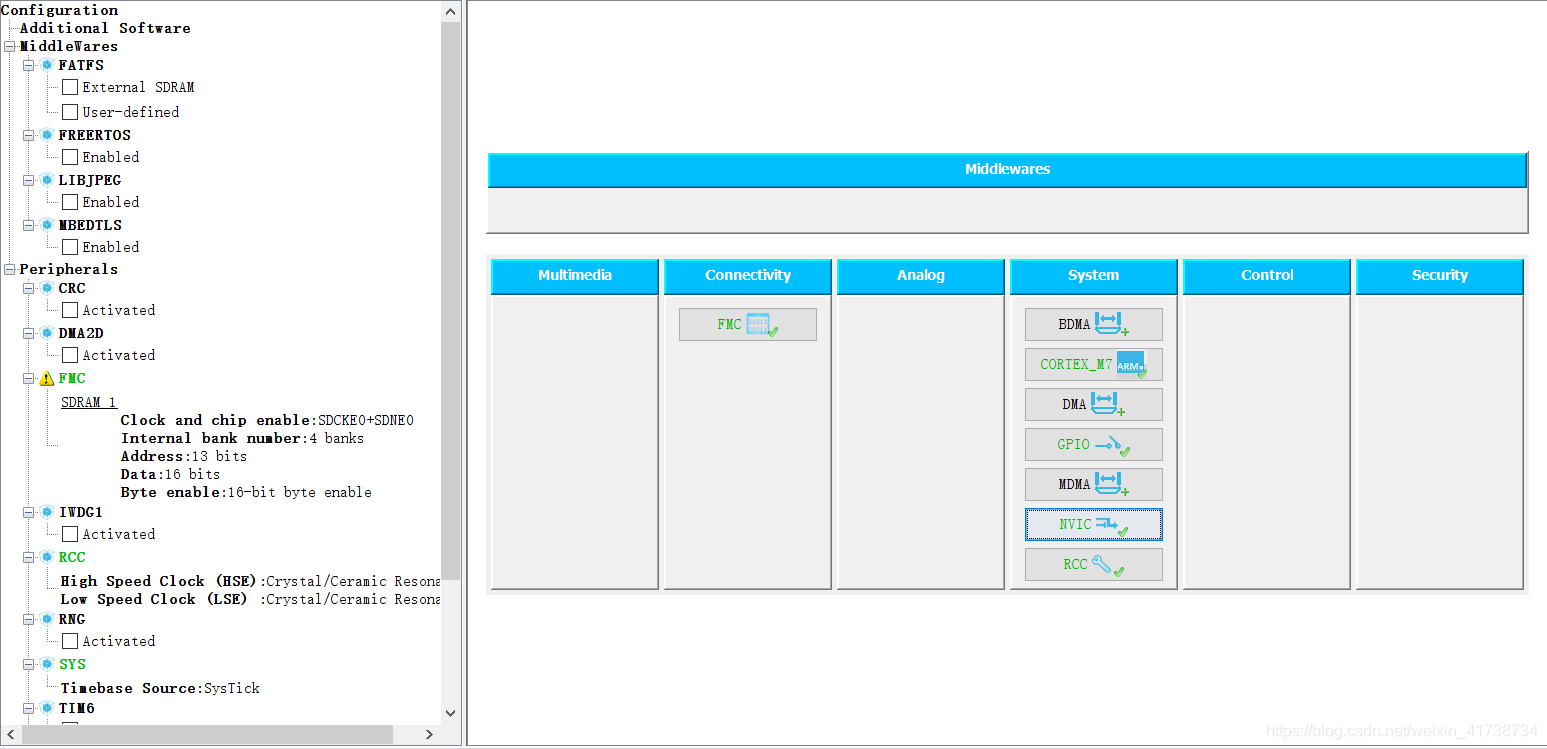

Configuration介面配置System

生成工程

Pinout配置

根據晶片進行合適的配置

Clock Configuration配置

開啟系統時鐘,

Configuration

左側主要系統功能的開啟,或中間軟體層功能的開啟(如:RTOS、JPEG解碼器,檔案系統等)

右側是系統及外設模組的具體配置

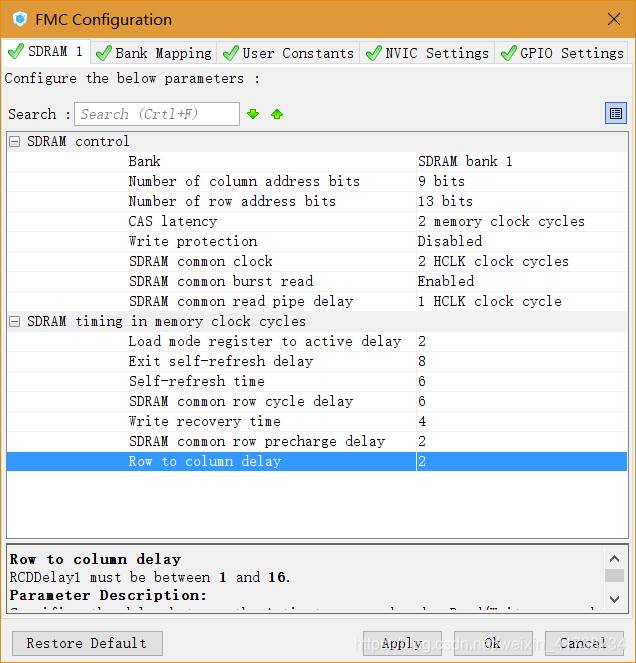

FMC

程式碼部分

main.c

USER CODE BEGIN 0 、USER CODE BEGIN Includes中的程式碼源自原子的H7中DRAM中的部分驅動程式碼

/* USER CODE BEGIN Includes */

#define Bank5_SDRAM_ADDR ((unsigned int)(0XC0000000))

#define SDRAM_MODEREG_BURST_LENGTH_1 ((unsigned int)0x0000)

#define SDRAM_MODEREG_BURST_LENGTH_2 ((unsigned int)0x0001)