【OS學習筆記】十二 現代處理器的結構和特點

本文是一個銜接點,上一篇文章以前都是學習8086真實模式的知識。本文開始學習80386這種現代處理器的程式設計架構。由此進入保護模式的學習。點選連結檢視上一篇文章:上一篇文章

1、現代處理器的結構和特點

1 流水線技術

處理器可以做很多事情,能夠執行各種不同的指令,完成不同的功能,但這些事情大多不會再一個時鐘週期內完成。執行一條指令,需要從記憶體中取指令,譯碼,訪問運算元和結果,並進行移位、加法、減法、乘法以及其他任何操作。

為了提高處理器的執行效率和速度,可以把一條指令的執行過程分解成若干個細小的步驟,並分配給相應的單元來完成。各個單元的執行都是獨立的、並行的。如此一來,各個步驟在時間上就會重疊起來,這種執行指令的方法,就是流水線(Pipe-Line)技術。

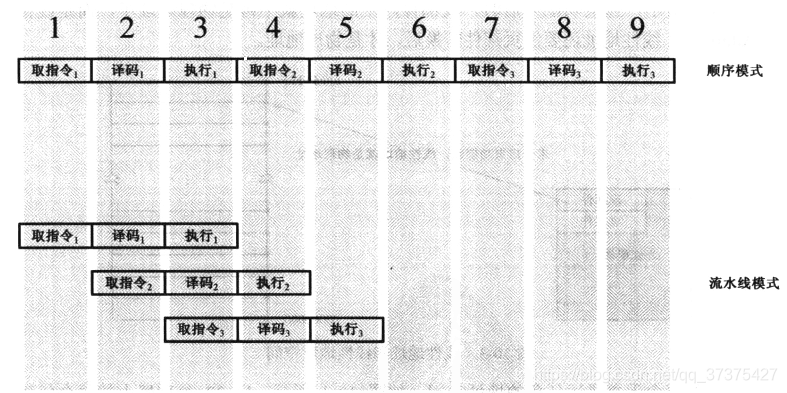

比如,一條指令的執行過程分為取指令、譯碼和執行三個步驟的話。假設每個步驟都要花一個時鐘週期,那麼如下圖所示,如果採用順序執行,則執行三條指令就要花9個時鐘週期,沒3個時鐘週期才能得到一條指令的執行結果;如果採用3級流水線技術的話,則執行這三條指令只需要5個時鐘週期,每隔一個時鐘週期就能夠得到一條指令的執行結果。

2、快取記憶體技術

快取記憶體,在以前的文章中有講的很詳細,這裡不再贅述,直接檢視以前的文章即可。

點解下面連結檢視:

其實簡單來說快取記憶體就是為了彌補外存(記憶體條)的讀寫速度過於緩慢的缺陷。將記憶體中的一些指令和資料,快取到快取記憶體中,那麼CPU可以不用訪問記憶體而直接訪問快取記憶體,這樣會快的多!!!

3、亂序執行技術

為了實現流水線技術,需要將指令拆分成更小的可獨立執行部分,即拆分成微操作。

一旦將指令拆分成微操作,處理器就可以在必要的時候亂序執行。考慮以下程式:

mov eax , [mem1]

shl eax , 5

add eax , [mem2]

mov [mem3] , eax

這裡add eax , [mem2]可以拆分成兩個微操作。先從mem2對應的地址取資料,然後將資料與eax暫存器中存的資料相加,得到的結果存入eax暫存器。如此一來,在執行邏輯左移指令的同時,處理器可以提前從記憶體中讀取mem2的內容。典型的,如果資料不在快取記憶體中,那麼處理器在獲取mem1的內容後,會立即開始獲取mem2的內容,與次同時,shl指令的執行早就開始了。

類似的這種亂序執行很多很多,總給不在贅述。

4、暫存器重新命名技術

考慮以例子:

mov eax , [mem1]

shl eax , 3

mov [mem2] , eax

mov eax , [mem3]

add eax , 2

mov [mem4] , eax

以上程式碼做了兩件事情,但是互不相干。

- 將mem1的內容左移3次後,傳給mem2

- 將mem3的內容加2後,傳給mem4

如果我們為最後三條指令使用不同的暫存器,就更能清楚的看明白,這兩件事的互不相干性。事實上,處理器也是這麼做的。處理器為最後三條指令使用了另一個不用的臨時暫存器,因此,左移和加法指令可以並行的處理。

IA-32架構的處理器只有8個32位的通用暫存器,但通常都會被我們全部派上用場(甚至還覺得不夠)。因此我們不能奢望在每個計算機中都使用新的暫存器。不過在處理器內部,卻有大量的臨時暫存器可用,處理器可以重新命名這些暫存器,但是以代表一個邏輯暫存器,比如上述的EAX暫存器。

暫存器重新命名以一種完全自動和非常簡單的方式工作。每當指令寫一個邏輯暫存器時,處理器就為那個邏輯暫存器分配一個新的臨時暫存器。

在所有操作都完成之後,那個代表EAX的臨時暫存器裡面存的內容就會被寫入真實的EAX暫存器,該處理過程稱為引退。

所有通用暫存器,棧指標暫存器,標誌暫存器,浮點暫存器,甚至段暫存器都有可能被重新命名。

5、 分支目標預測技術

流水線並不是百分之百完美的解決方案。實際上,有很多潛在的因素會使得流水線不能達到最佳的效率。一個典型的情況是,如果遇到一條轉移指令,則後面那些已經進入流水線的指令就都無效了。換句話說,我們必須清空流水線,從要轉移到的目標位置處重新取指令放入到流水線。

隨著複雜架構下的流水線變得越來越長,程式分支帶來的問題變得很大。為了解決這個問題,引入了分支預測技術。

從統計學的角度來看,有些事情一旦發生,下一次發生的概率很大。比如下面的程式片段:

xor si , si

lops:

......

cmp si , 20

jnz lops

當jnz指令第一次執行時,轉移一定會發生。那麼處理器就可以預測,下一次它還會轉移到標號lops處,而不是順序往下執行。事實上,這個預測通常是很準的。

在處理器內部,有一個小容量的快取記憶體器,叫做 分支目標快取器(BTB)。當處理器執行了一條分支語句後,它會在BTB中記錄當前指令的地址、分支目標的地址。以及本次分支預測的結果。下一次,在那條轉移指令實際執行之前,處理器會查詢BTB中,看有沒有最近的轉移記錄。如果能找到最近的條目,則推測執行和上次相同的分支,把該分支的指令送入流水線。

當該指令執行時,如果預測是失敗的,那麼清空流水線,同時重新整理BTB中的記錄。這個代價很大。

細心的人早已發現,這其實就是一個快取的思想!!!這個思想很牛逼!!!

2、總結

理解現代處理器的結構特點:

- 流水線技術

- 快取記憶體思想

- 亂序執行思想

- 暫存器重新命名

- 分支目標預測技術

其實這些思想,在以後的上層軟體開發中,也是經常遇到。

筆記記得不是很全,如果有不懂的可以加我聯絡方式一起交流。

學習探討加個人:

qq:1126137994

微信:liu1126137994