計算機組成原理--main memory 到 cache 對映機制

基本介紹

為了平衡高速的CPU與較慢的主存之間的差異,我們引入到了cache作為中間媒介,cache的主要作用說來可以理解成將主存中很有可能被CPU使用的小部分資料調入cache中,由於cache是很快的,則可以對系統的系統有較大提升。相關詳細情況可以參見計算機組成原理–cache概念及其作用。

這篇部落格的主要任務是探討Main memory到cache的多種對映機制,並討論其優勢與劣勢,知道後期的使用。

目前已經投入使用的對映機制主要有以下三種:

- 直接對映(Direct Mapping)

- 全域性關聯對映(Fully Associative Mapping)

- 組關聯對映(Set Associate Mapping)

以下將對三種分別進行介紹。

直接對映(Direct Mapping)

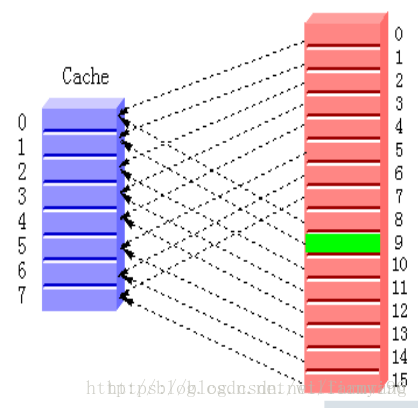

直接對映的直觀表示圖為:

關於其設計實現是基於模數計算得到的。我們知道,cache的每一行與主存的一個塊是相互對應的。

我們有如下公式:

i = j mod m- 其中j是主存塊的編號,m是cache的行數,而i是主存中塊對映到cache中的行編號。

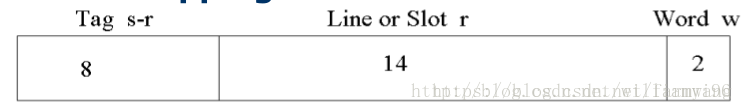

接下來我們看一看直接對映的地址結構,如圖所示:

其將24位的地址分為字地址,行數和標籤。其中字數是由主存中塊所包含的大小決定的(如此處word為2,假設每個地址空間有一個位元組的資料,則一個塊有四個位元組)。

行數是根據實際條件進行確定的,將在之後的練習中具體說明。

而Tag的位數,則是有減法計算得到的。

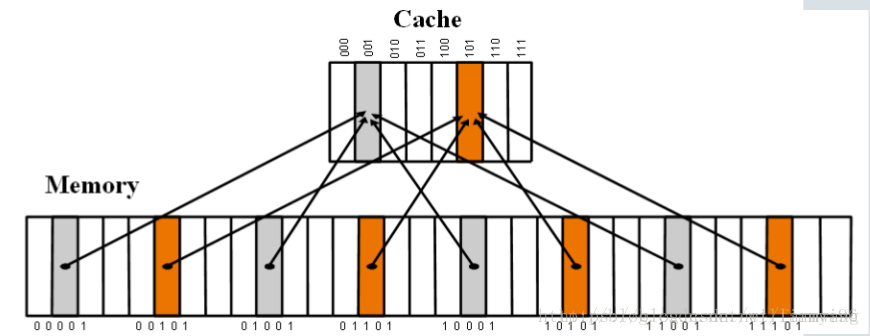

我們可以很直觀地看到,使用直接對映的方式實現起來相對而言較為方便,但是其劣勢也是很大的一個問題,也就是thrashing(抖動)。 如圖所示:

由於00001與01001的word位相同,因此其將被對映到cache的同一行,呼叫完成00001後,不命中,CPU去主存中取01001的塊,然後10001也不命中,再去主存中取。則會大大浪費時間,因為不命中的時間消耗等於cache訪問的消耗加上主存訪問的消耗。

這也就是我們所說的抖動的現象。

全域性關聯對映(Fully Associate Mapping)

上面講到的直接對映機制有著容易發生抖動致使CPU效率降低的現象,那麼產生這種問題的根本原因是什麼呢?不難發現,是我們將對映規則定義得太死板了,也就是存在主存和快取記憶體之間的一一對映關係。

為了解決抖動的這一問題,我們引入了全域性關聯對映(Fully Associate Mapping)。其核心思想就是對於每一個塊都可以放入任何一個cache中的行。

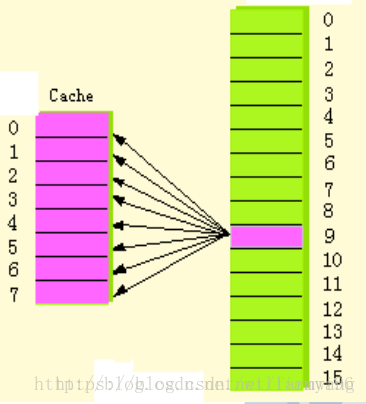

直觀表示為:

當cache還有空行時,對應的塊直接填入其中的任意一個。當cache被填滿時,則使用後面部落格中會提到的替換演算法來進行選擇性填入。

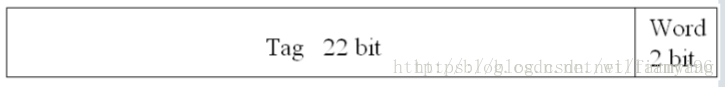

全域性關聯對映的地址結構為:

我們可以看到tag位有22bit之多,因此實現起來的並行比較電路較為複雜,計算量較大,影響效能,同時這種複雜性就自然造成了成本的提升。

組關聯對映(Set Associate Mapping)

直接對映的實現結構簡單但是對映機制不夠靈活,全域性關聯對映的對映機制靈活但是實現結構相對複雜。

那麼我們能不能對兩者進行折中呢?自然可以。這也便引出了組關聯對映(Set Associate Mapping)的概念。

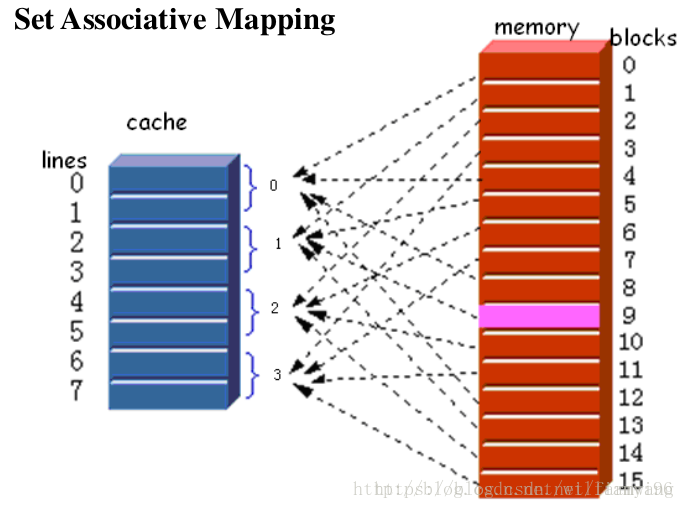

其是將多個塊歸類為一個組,同時將cache中的多行也化歸為一組。主存中的組與cache中的組是對應的,也是採用的直接對映中模數的方式,只不過其模的m為cache中組的數量。

此外,主存中的資料匯入到cache中仍然是採用塊的方式,而且其匯入的塊可以放在對應組的任何一行,其思想來源便是全域性關聯對映。

組關聯對映的直觀表示為:

對應的,組關聯對映的地址結構為:

其得到的方式與直接對映以及全域性關聯對映基本相同,此處便不再進行贅述。

實踐證明,組的線數在2–8是在trade-off之下效能的最好狀態。

總結

本文章討論了主存到cache對映的三種機制。從直接對映,到全域性關聯對映,再到兩者的折中,組關聯對映。從巨集觀上對其進行了分析,對其思想進行了清晰的闡述。

特別感謝西安交通大學李晨老師為我們教授的計算機組成原理這門課,生動幽默,深入淺出。文中所有使用的圖片均來自於李晨老師的課件,所有權歸屬於李晨老師。