智慧閘道器韌體編譯學習筆記——Makefile

一、makefile簡介

(1)程式的編譯和連結

為了更好的理解makefile的意義,有必要了解一些程式編譯的規範和方法。就C語言的編譯規則來看,首先要把原始檔編譯成中間程式碼檔案,在Windows下也就是 .obj 檔案,UNIX下是 .o 檔案,即 Object File,這個動作叫做編譯(compile)。然後再把大量的Object File合成執行檔案,這個動作叫作連結(link)。 總結一下,原始檔首先會生成中間目標檔案,再由中間目標檔案生成執行檔案。

(2)為什麼要用makefile

當整個專案中有很多檔案,你使用的是命令列而不是IDE,那麼在對專案進行編譯時,需要一個檔案一個檔案的執行:

gcc -0 1.c 2.c 3.c ... -0 XXX.out

這樣不僅編譯命令複雜,檔案還需要一個個去查詢,很明顯會影響到這個專案的編譯效率。而使用makefile進行編譯可以很好的解決這問題,make命令執行時,需要一個makefile檔案,以告訴make命令需要怎麼樣的去編譯和連結程式。

(3)makefile規則和結構

我們可以簡單的把makefile認為是一份定義了原始檔間依賴關係、如何編譯各個原始檔並生成可執行檔案的說明書。makefile實現了“自動化編譯”,只需一個make命令,整個工程完全自動編譯,極大的提高了軟體開發的效率。比如我們可以這樣定義編譯規則

1.如果這個專案沒有編譯過,那麼我們的所有C檔案都要編譯並被連結。

2.如果這個專案的某幾個C檔案被修改,那麼我們只編譯被修改的C檔案,並連結目標程式。

3.如果這個工程的標頭檔案被改變了,那麼我們需要編譯引用了這幾個標頭檔案的C檔案,並連結目標程式。

makefile基本結構:

Target : Prerequisites....

Command....

........

......

Target:規則的目標,最終生成檔案的名字或者是中間過程檔名,也可以是make執行的動作的名稱。

Prerequisites:規則的依賴,生成目標所必須的檔名列表。

Command:規則的命令。規則需要執行的動作 注意

這是一個檔案的依賴關係,也就是說,target這一個或多個的目標檔案依賴於prerequisites中的檔案,其生成規則定義在command中。說白一點就是說,prerequisites中如果有一個以上的檔案比target檔案要新的話,command所定義的命令就會被執行。這就是Makefile的規則。也就是Makefile中最核心的內容。

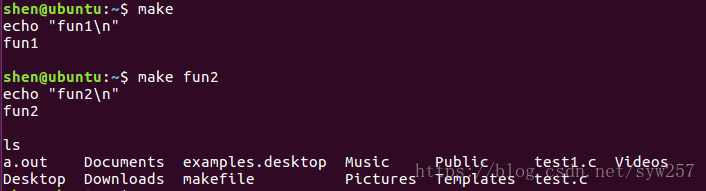

(4)makefile簡單示例

fun1:

echo "fun1"

fun2:

echo "fun2"

ls

執行結果如下圖所示: