【轉載】閘電路組成D觸發器

5.4.1 D觸發器電路結構與工作原理

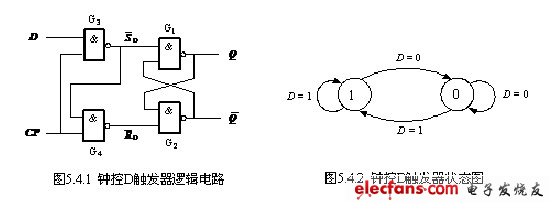

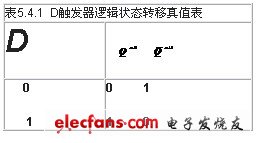

簡單的鐘控D觸發器的邏輯電路如圖5.4.1所示。它也是在基本的RS觸發器的基礎上發展而來的。D觸發器只有一個數據端。

下面結合其電路結構分析其工作原理。

當時鍾訊號CP = 0時,經G3和G4與非門後,得 、

、 ,所以D觸發器得邏輯狀態保持不變。

,所以D觸發器得邏輯狀態保持不變。

當時鍾訊號CP = 1時,經G3和G4與非門後,得 、

、 ,代入基本RS觸發器得特性方程可得:

,代入基本RS觸發器得特性方程可得:

(5.4.1)

(5.4.1)

上式即為D觸發器特性方程,根據基本RS觸發器約束條件:

所以鍾控D觸發器輸入端沒有約束條件得限制。從式(5.4.1)的特性方程可以看出其工作得特點為:CP

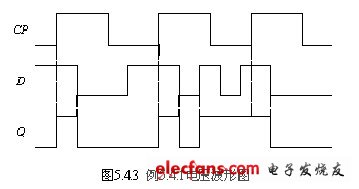

例5.4.1 在圖5.4.1所示的鐘控D觸發器中,已知CP和D的波形如圖5.4.3所示,試畫出輸出端 的電壓波形。設初始狀態

的電壓波形。設初始狀態 。

。

解:鍾控D觸發器的工作特點是在時鐘訊號為1期間,輸出端根據輸入端D的資料而發生變化。根據這一特點作出輸出端的電壓波形如圖5.4.3所示。

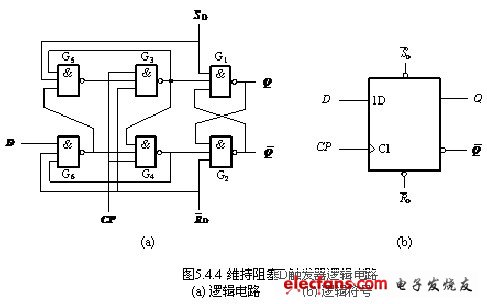

5.4.2 邊沿D觸發器

鍾控D觸發器同樣存在CP = 1期間的多次翻轉現象。只有採用邊沿結構的D觸發器才能解決這個問題,使輸出端的值只與時鐘訊號邊沿時刻所對應的D資料有關。圖5.4.4為維持阻塞D觸發器邏輯電路圖和符號。

電路中 、

、 是非同步復位、置位功能端,其作用如下:

是非同步復位、置位功能端,其作用如下:

(1)當 、

、 時,門G2輸出為1,即

時,門G2輸出為1,即 ;同時

;同時 的低電平送到了G3,則G3輸出為1,G1的三個輸入端都為1,G1則輸出為0,即

的低電平送到了G3,則G3輸出為1,G1的三個輸入端都為1,G1則輸出為0,即 ,觸發器復位。

,觸發器復位。

(2)當 、

、 時,G1輸出為1,即

時,G1輸出為1,即 ;同時

;同時 的低電平送到了G5,則G5輸出為1,如果CP = 1,則G3的三個輸入端都為1,G3輸出為0,得G4的輸出為1,從而得出G2輸出為0,即

的低電平送到了G5,則G5輸出為1,如果CP = 1,則G3的三個輸入端都為1,G3輸出為0,得G4的輸出為1,從而得出G2輸出為0,即 ,如果CP = 0,G3 和G4輸出都為1,得G2輸出為0,即

,如果CP = 0,G3 和G4輸出都為1,得G2輸出為0,即 ,觸發器置位。

,觸發器置位。

從分析的結果來看, 和

和 的復位和置位與時鐘訊號CP無關,都是低電平有效。

的復位和置位與時鐘訊號CP無關,都是低電平有效。

、

、 中沒有低電平出現時,在時鐘訊號的邊沿作用下,輸出端的邏輯狀態與輸入端的資料D有關。其工作原理如下:

中沒有低電平出現時,在時鐘訊號的邊沿作用下,輸出端的邏輯狀態與輸入端的資料D有關。其工作原理如下:

(1)當D= 0時

在CP= 0時,G3、G4的輸出為1,G6 輸出為1,G5輸出為0,此低電平封鎖了G3。在CP由0→1時刻,G4的輸入端的時鐘訊號變為1,其全部的輸入端都是1,所以G4輸出為0,從而 、

、 。G4輸出0送到了G6,此時即使D的資料發生變化,G6的輸出也不會改變。所以將G4到G6的連線稱為置0維持線。G3到G4的連線稱為置0阻塞線。

。G4輸出0送到了G6,此時即使D的資料發生變化,G6的輸出也不會改變。所以將G4到G6的連線稱為置0維持線。G3到G4的連線稱為置0阻塞線。

(2) 當D= 1時

在CP= 0時,G3、G4的輸出為1,G6 輸出為0,此低電平封鎖了G4,G5輸出為1。在CP由0→1時刻,G3的輸入端的時鐘訊號變為1,其全部的輸入端都是1,所以G3輸出為0,從而 、

、 。G3輸出0送到了G5,此時即使D的資料發生變化,G5的輸出也不會改變。所以將G3到G5的連線稱為置1維持線。G5到G6的連線稱為置1阻塞線。

。G3輸出0送到了G5,此時即使D的資料發生變化,G5的輸出也不會改變。所以將G3到G5的連線稱為置1維持線。G5到G6的連線稱為置1阻塞線。

通過上面的分析可知,由於採用了維持阻塞結構,在CP訊號的上升沿到來時將D的資料送到了輸出端,具有邊沿觸發特性,在CP訊號上升沿之後,D的資料即使發生變化,也不會影響到輸出端。其抗干擾能力比主從結構的觸發器強。

邊沿D觸發器的特性方程為:

。 (5.4.2)

。 (5.4.2)

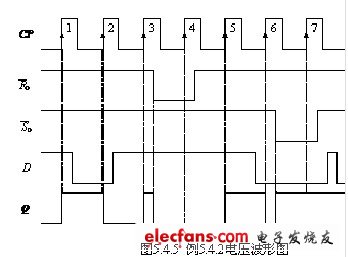

例5.4.2 在圖5.4.4所示的邊沿D觸發器中,已知CP、D、 和

和 波形如圖5.4.5所示,試畫出輸出端

波形如圖5.4.5所示,試畫出輸出端 的電壓波形。設初始狀態

的電壓波形。設初始狀態 。

。

解:根據邊沿D觸發器的工作特點,電路中 、

、 是直接復位、置位功能端,與此時的CP和D訊號無關,在

是直接復位、置位功能端,與此時的CP和D訊號無關,在 、

、 同時為高電平時,時鐘訊號的上升沿到來時將D的資料儲存到輸出端。作出輸出端

同時為高電平時,時鐘訊號的上升沿到來時將D的資料儲存到輸出端。作出輸出端 的電壓波形如圖5.4.5所示。

的電壓波形如圖5.4.5所示。

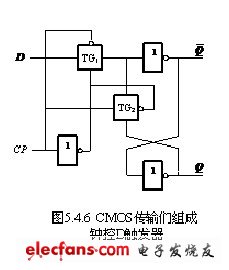

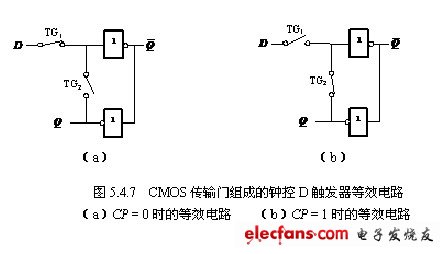

利用CMOS傳輸門也可以組成鍾控D觸發器。其電路結構如圖5.4.6所示。電路由兩個傳輸門和兩個非-門組成。

當CP = 0時,TG1導通,TG2關斷,此時的等效電路如圖5.4.7(a)所示,觸發器的輸出端 和

和 的值與輸入端D有關,即:

的值與輸入端D有關,即: ,

, 。當CP = 0時,TG2導通,TG1關斷,此時的等效電路如圖5.4.7(b)所示,觸發器的輸出端

。當CP = 0時,TG2導通,TG1關斷,此時的等效電路如圖5.4.7(b)所示,觸發器的輸出端 和

和 的狀態保持不變。

的狀態保持不變。

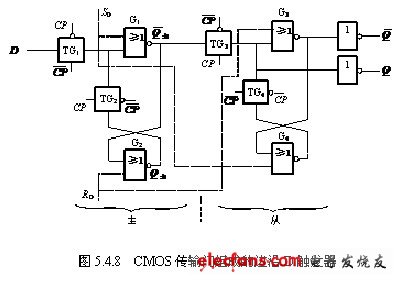

利用CMOS傳輸門也可以組成邊沿D觸發器,其電路結構如圖5.4.8所示。

電路採用的是主從結構,將兩個CMOS傳輸門組成的鐘控D觸發器連線而成。圖中的虛線表明的是D觸發器的非同步復位、置位功能端RD、SD,是高電平有效復位和置位。

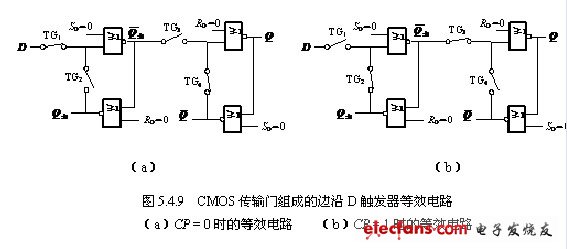

當CP = 0時,TG1導通,TG2關斷,TG3關斷,TG4導通,此時的等效電路如圖5.4.9(a)所示,觸發器的輸出端 跟隨輸入端D的資料變化而變化,而輸出端

跟隨輸入端D的資料變化而變化,而輸出端 和

和 的值保持不變。

的值保持不變。

當CP = 1時,TG2導通,TG1關斷,TG4關斷,TG3導通,此時的等效電路如圖5.4.9(b)所示,觸發器的輸出端 和

和 的值取決與

的值取決與 的值,也就是說在時鐘訊號的上升沿到來時,將主觸發器的資料送到輸出端儲存下來,而在時鐘訊號下降沿前夕,

的值,也就是說在時鐘訊號的上升沿到來時,將主觸發器的資料送到輸出端儲存下來,而在時鐘訊號下降沿前夕, 的值是等於此時的輸入端D的值,所以在CP由0→1時,輸出端接收D的資料,也就是邊沿觸發器的特點。其邏輯符號如圖5.4.4(b)所示。

的值是等於此時的輸入端D的值,所以在CP由0→1時,輸出端接收D的資料,也就是邊沿觸發器的特點。其邏輯符號如圖5.4.4(b)所示。