嵌入式課程有關CPSR程式狀態暫存器的解析

阿新 • • 發佈:2018-12-15

1.定義:

CPSR:程式程式狀態暫存器(current program status register) cpsr在使用者級程式設計時用於儲存條件碼;CPSR包含條件碼標誌,中斷禁止位,當前處理器模式以及其他狀態和控制資訊。

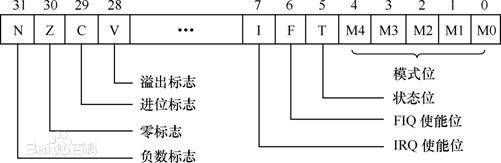

結構詳情參見下圖:

2.CPSR格式如下:

31 30 29 28 27 26 7 6 5 4 3 2 1 0 N Z C V Q DNM(RAZ) I F T M4 M3 M2 M1 M0 3.解析 ***CPSR中的其他位***

這些位用於將來擴充套件。應用軟體不要操作這些位。

CPSP也叫恆功率調速比,是英文constant power speed ratio的縮寫。常出現於永磁電機控制方法中。

***CPSR中的其他位***

這些位用於將來擴充套件。應用軟體不要操作這些位。

CPSP也叫恆功率調速比,是英文constant power speed ratio的縮寫。常出現於永磁電機控制方法中。