NVIDIA TX2---Tegra架構介紹

一、Tegra發展以及各Tegra對比

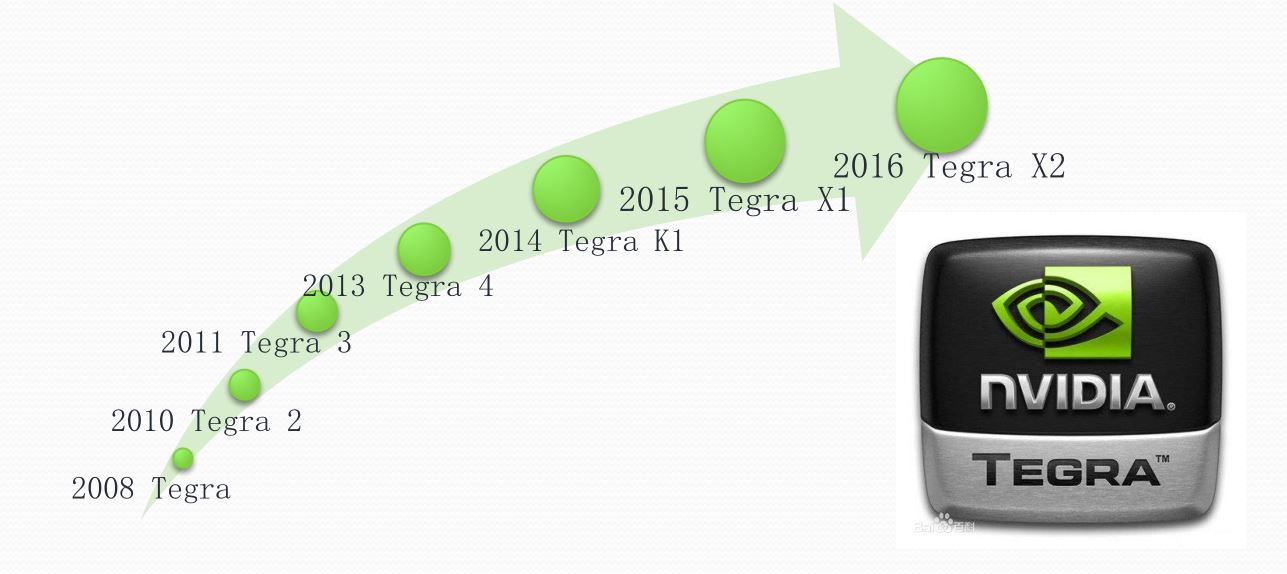

1、Tegra發展

(1)2008年2月,NVIDIA與Microsoft合作開發基於ARM11架構的APX 2500應用處理器釋出。

(2)隨後英偉達釋出Tegra產品Tegra 600 和 Tegra 650,整合的顯示核心是基於GeForce 6,並加入了對CUDA和雙精度浮點運算的支援。

2、Tegra發展圖譜

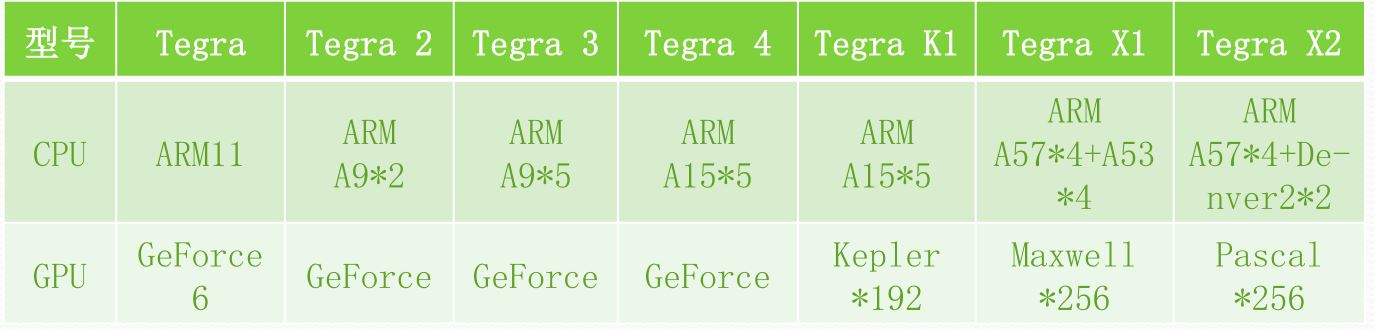

3、各Tegra簡要對比

二、Tegra X1/X2 架構解析

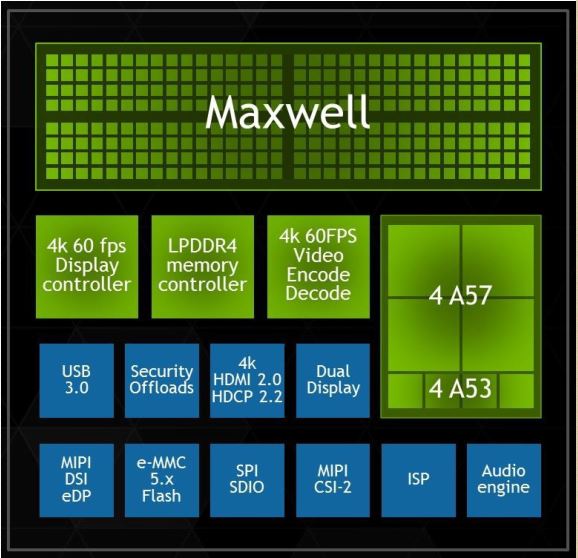

1、Tegra X1架構解析

(1)NVIDIA GeForce Maxwell 圖形處理單元(GPU);

(2)四核 ARM Cortex-A57 核心;

(3)64位DRAM介面提供了高寬頻;

(4)基於一個Cortex-A9處理器和獨立RAM的獨立音訊子系統;

(5)雙顯示控制器;

(6)高效能H.265/H.264視訊硬體編碼器,以及編碼器完全支援超高清的10位畫素4K視訊60fps。

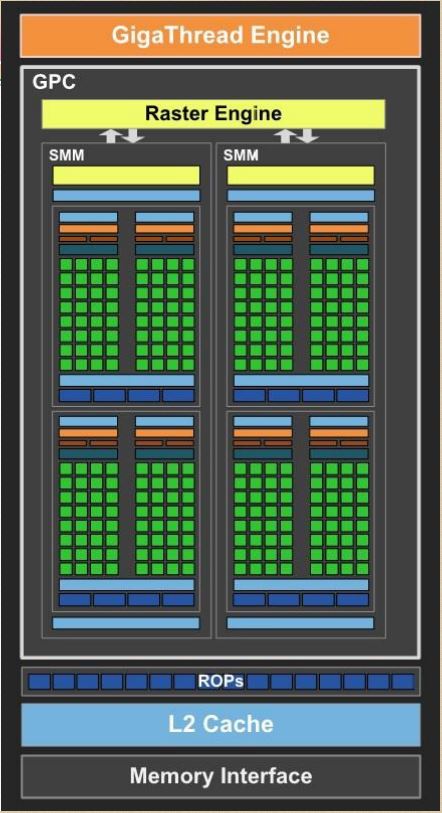

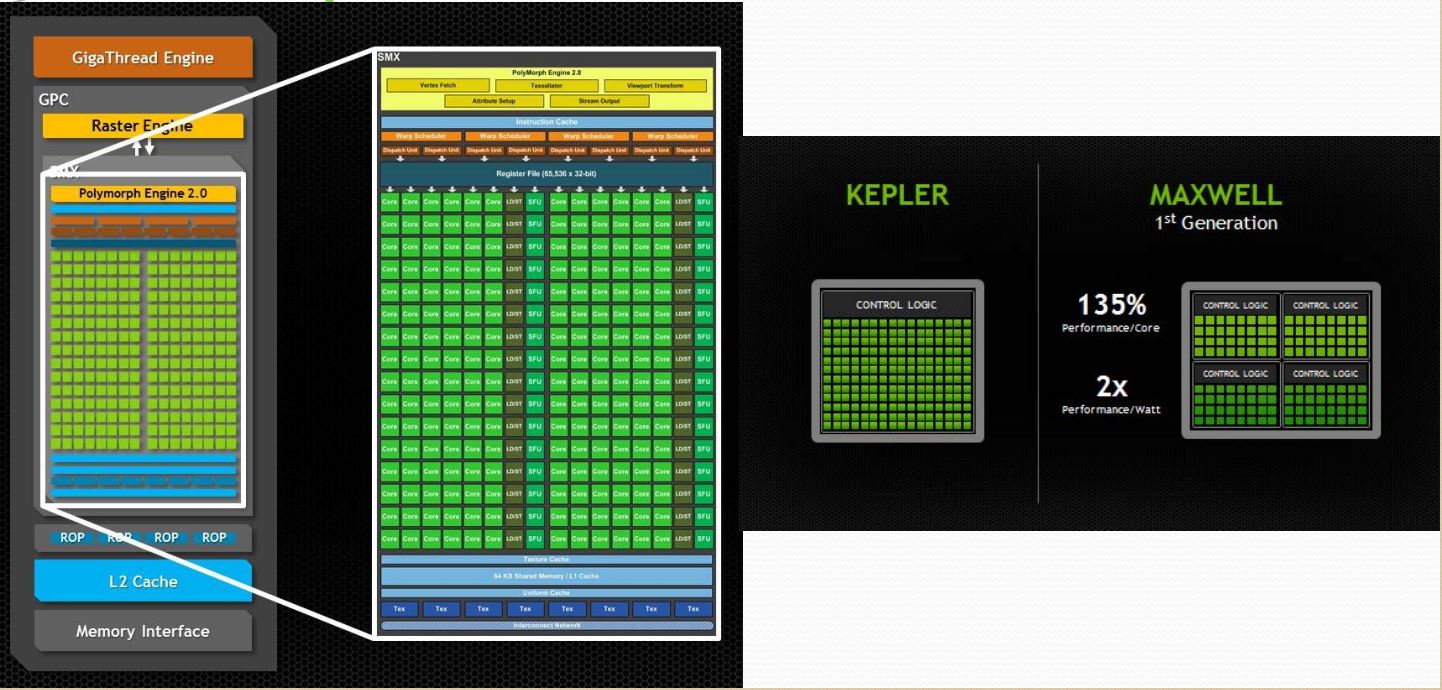

2、Maxwell架構解析

(1)相對Kepler而言,Maxwell重構了新的SMM以提高效率,全新的資料通路管理與組織;

(2)每個SMM包含4個Warp Schedulers;

(3)每個Warp Scheduler可以在每個Warp週期發起兩條指令;

(4)Maxwell的CUDA Core是Kepler效能的1.4倍;

(5)2 SMM * 4 Warp Scheduler * 32 CUDA Core Processing Blocks = 256 CUDA Core

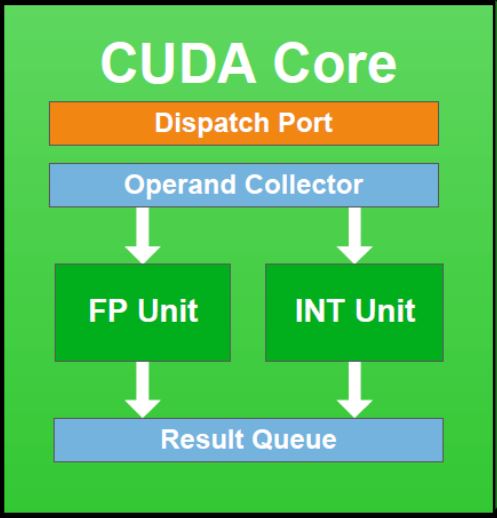

3、CUDA Core

4、Kepler VS Maxwell

5、GTX 980 VS TX1

6、Tegra X2架構解析

(1)NVIDIA Pascal 圖形處理單元(GPU)架構;

(2)雙核NVIDIA Denver 2 ARM CPU 核心,加四核ARM Cortex-A57核心;

(3)基於一個Cortex-A9處理器和獨立RAM的獨立音訊子系統;

(4)基於獨立的ARM Cortex-R5F 感測器處理器;

(5)基於獨立的ARM Cortex-R5F 處理器子系統用於處理啟動和能量管理;

(6)基於獨立的ARM Cortex-R5F 處理器子系統用於處理攝像頭管理;

(7)128位DRAM介面提供了高寬頻的LPDDR4支援。

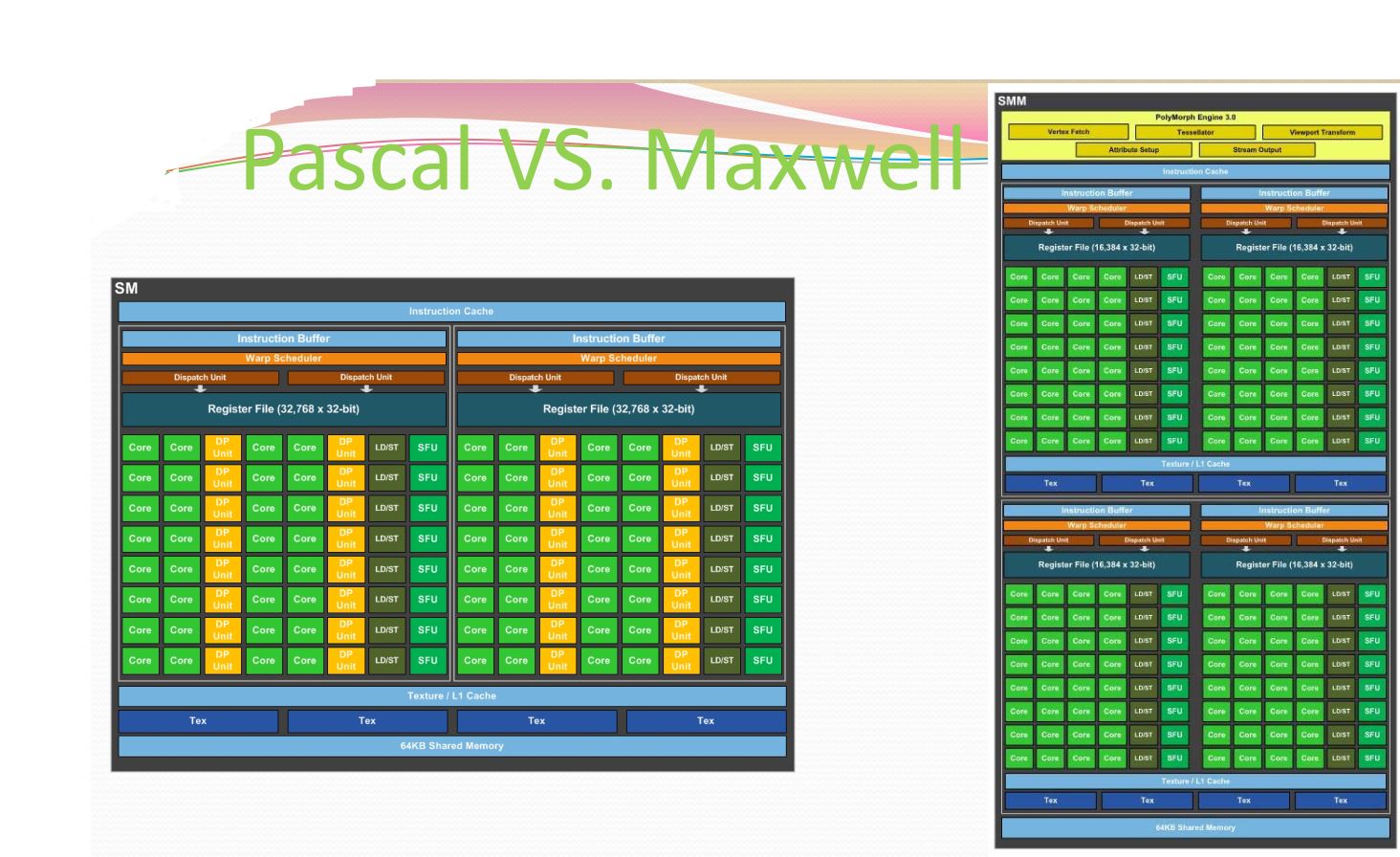

7、Pascal 架構解析

(1)相對於Kepler,Pascal簡化了資料通路組織與管理,降低了Die區域大小,降低了資料傳輸時的能量消耗;

(2)新的SM排程器架構基於Maxwell排程器,且更加的智慧化,即提高了效能有降低了功耗;

(3)一個SM內有2個Warp Scheduler,每個Warp Scheduler 可以在每個Warp週期發起兩條指令;

(4)一個Warp Scheduler內有32個單精度CUDA Core。

8、Pascal VS Maxwell

9、Jetson TX1 VS Jetson TX2

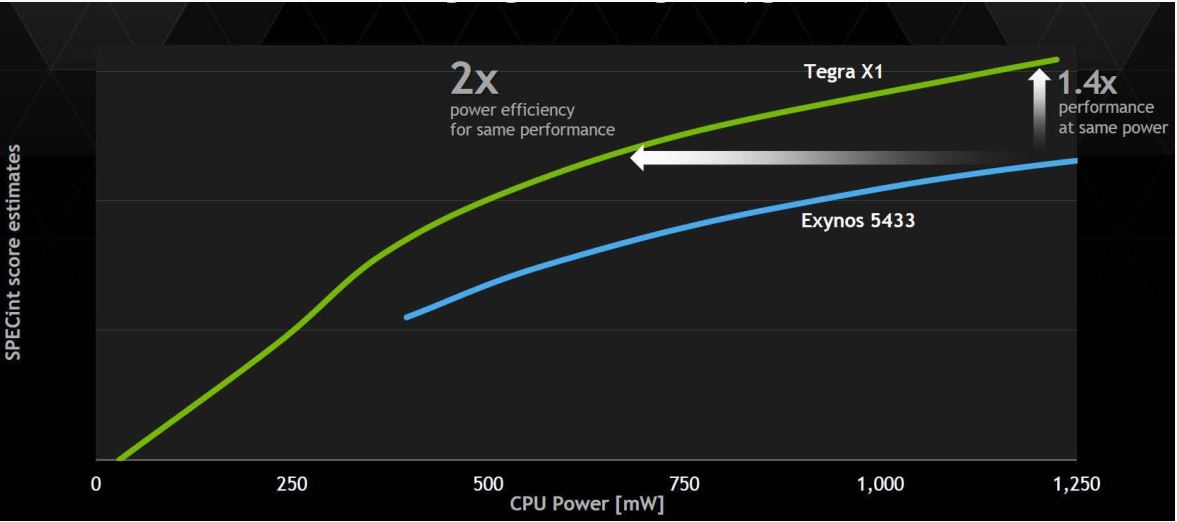

10、TX1處理器效能

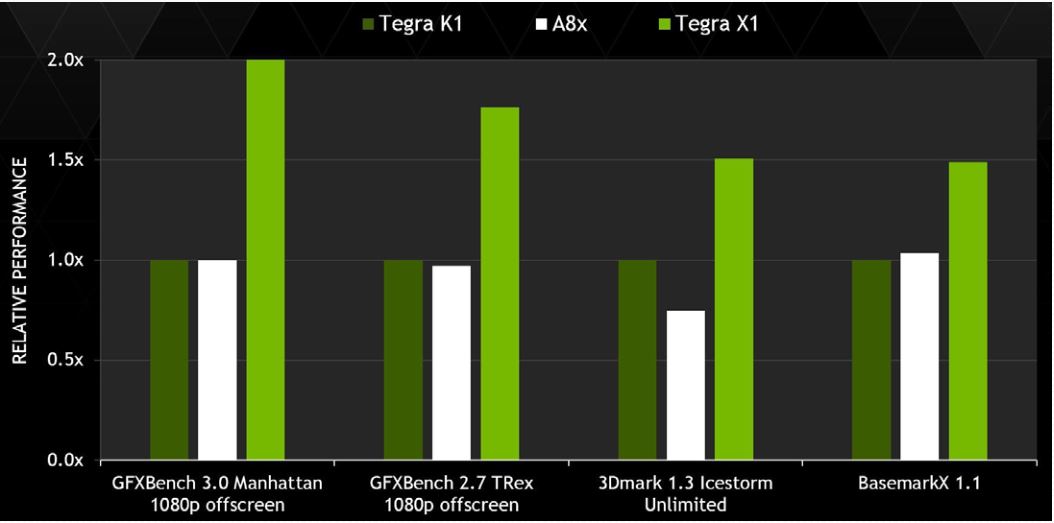

11、TX1圖形效能

三、ARM Cortex-A57架構解析

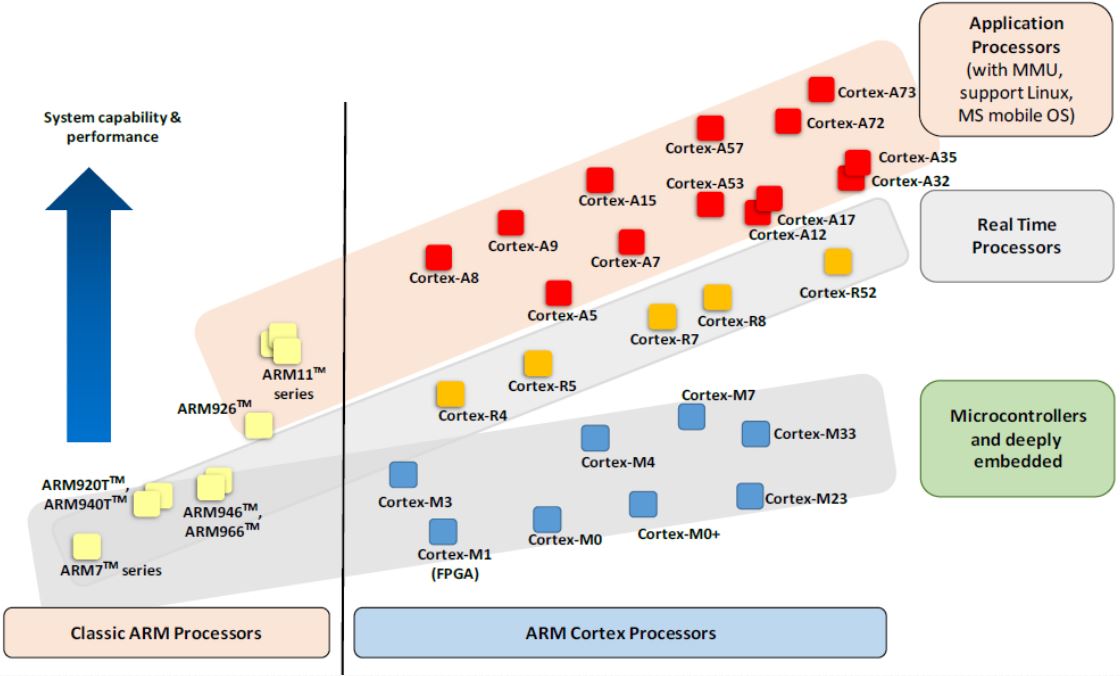

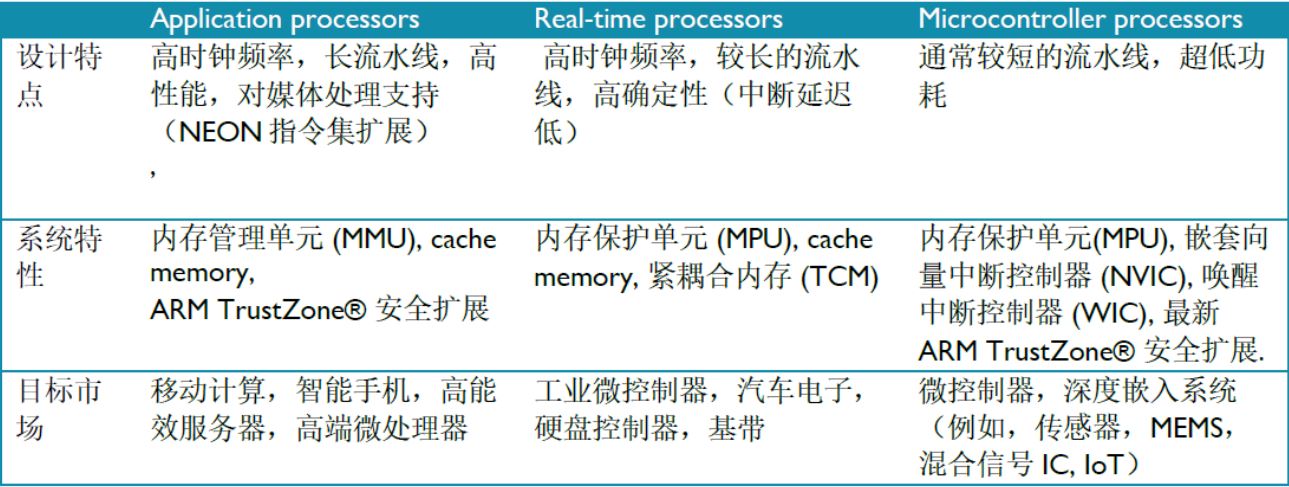

1、ARM處理器家族

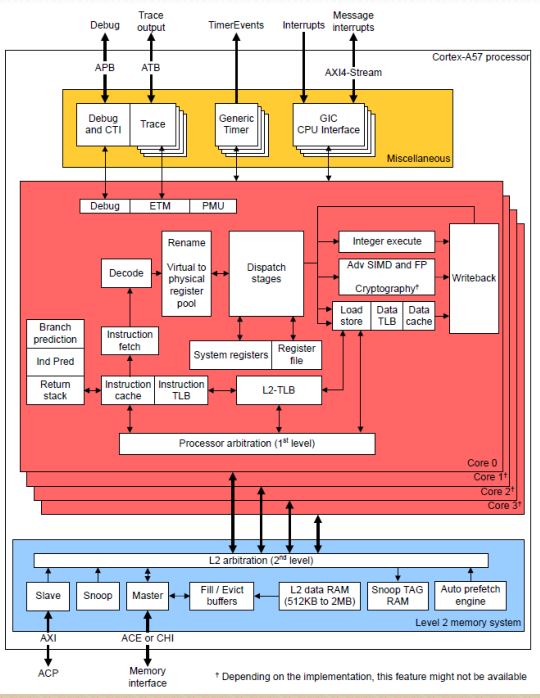

2、ARM Cortex-A57架構解析

(1)完全遵循 ARMv8-A 指令集規範;

(2)超標量,可變長度,亂序執行流水線;

(3)帶有分支目標緩衝(BTB)與全域性歷史緩衝(GHB)RAM,一個返回堆疊,以及一個間接預測器的動態分支預測;

(4)AMBA 4 AXI 一致性擴充套件(ACE)或CHI 主機介面;

(5)實現了加速器一致性埠(ACP)為AXI4一致性從機介面;

(6)支援基於ETMv4架構的嵌入式跟蹤單元(ETM);

(7)支援基於PMUv3架構的效能監控單元(PMU);

(8)用於多處理器除錯的交叉觸發介面(CTI);

(9)通用中斷控制器(GIC)CPU介面。

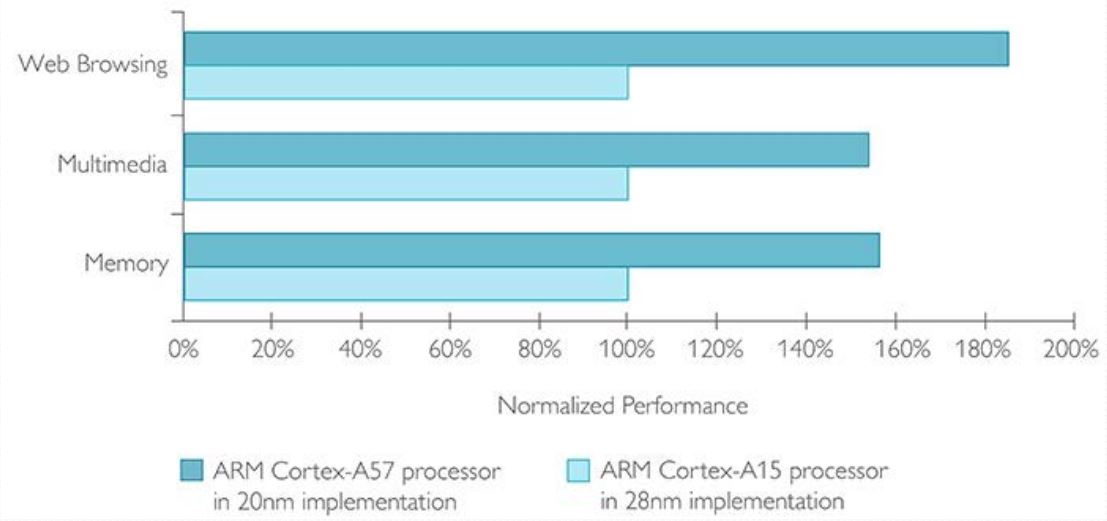

3、ARM Cortex-A57的效能

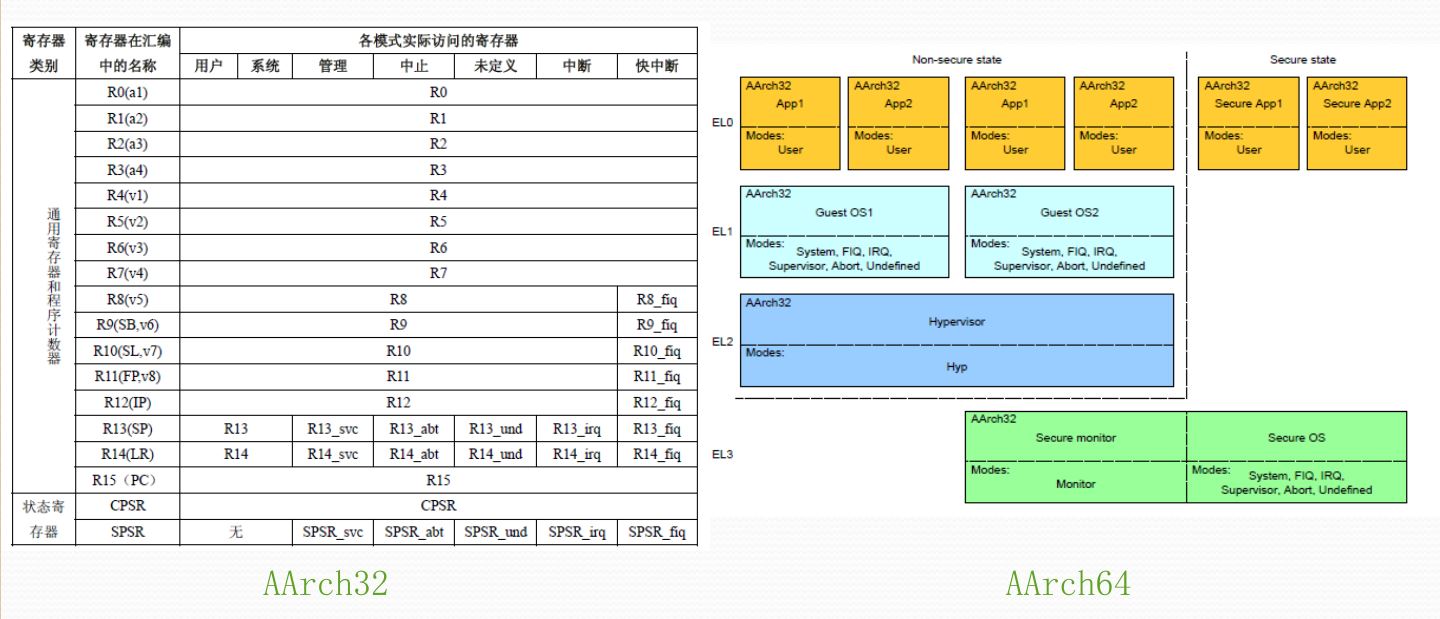

4、AArch32 VS AArch64

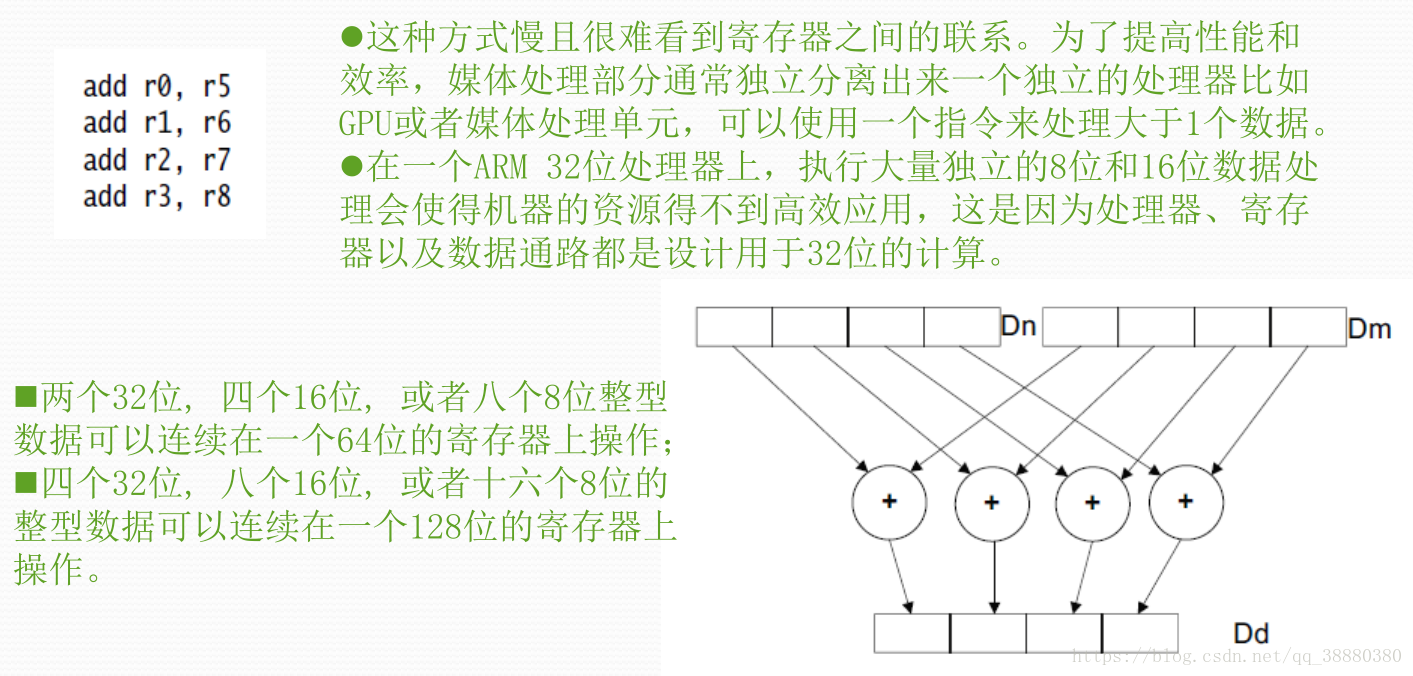

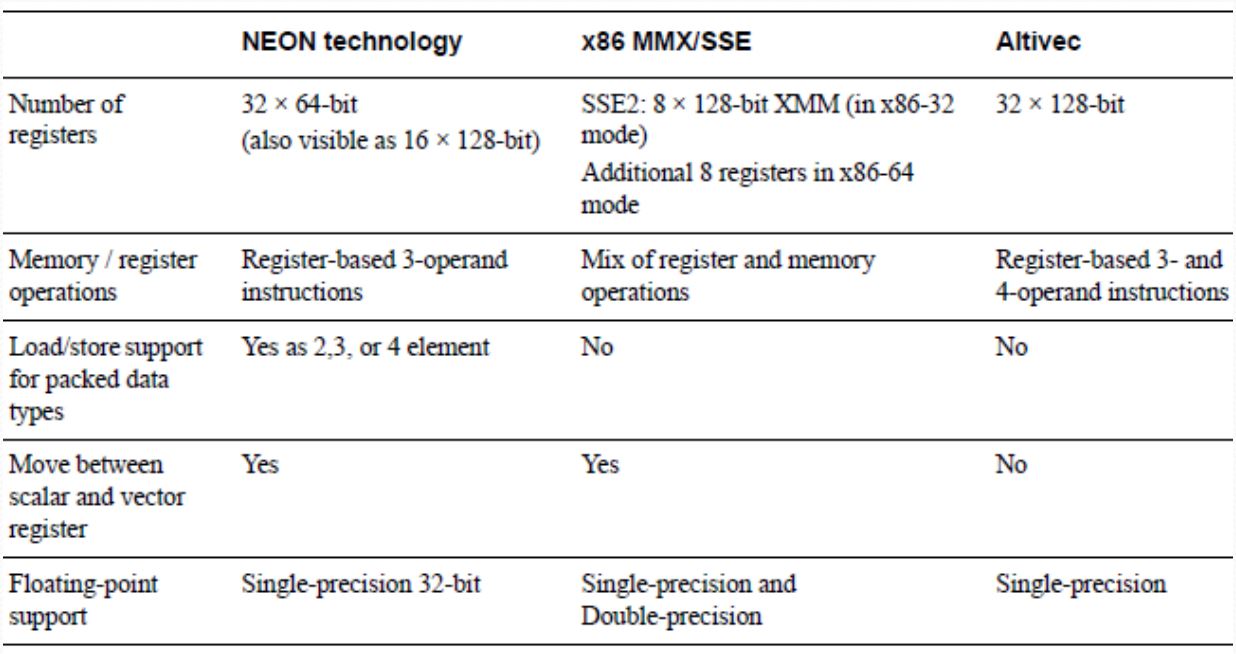

5、NEON架構解析

(1)架構分析

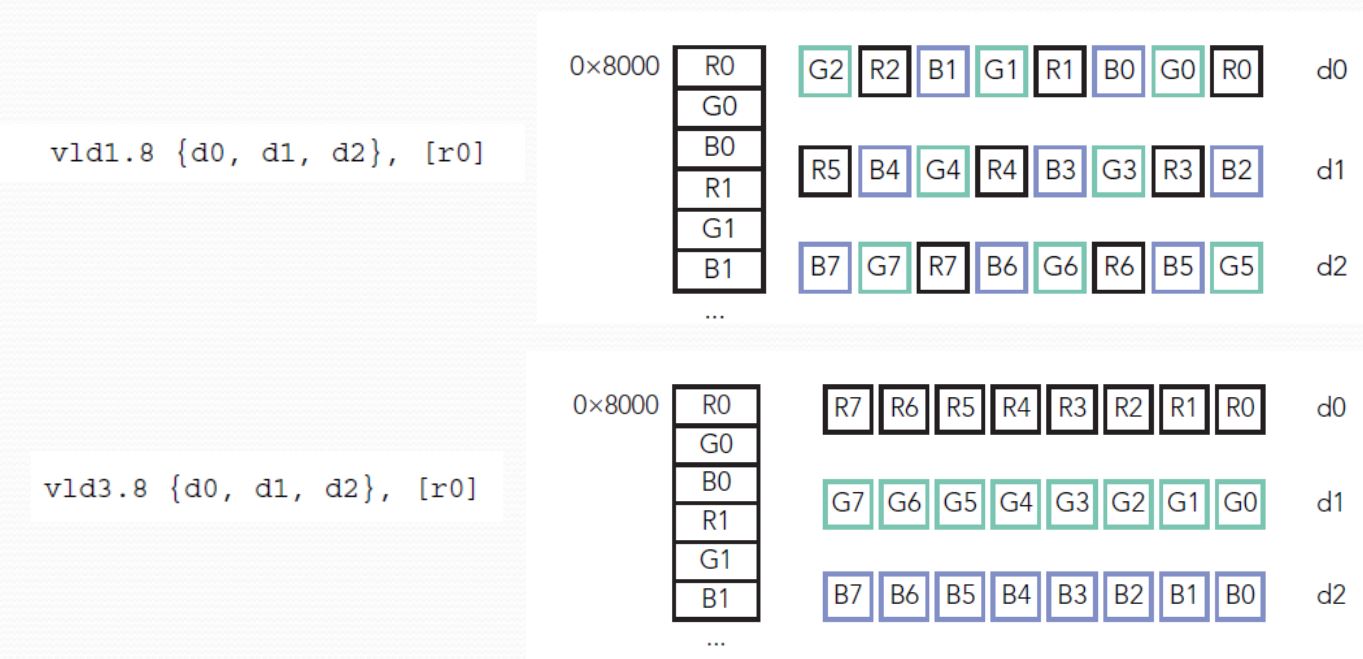

(2)NEON資料讀取模式

(3)NEON架構對比

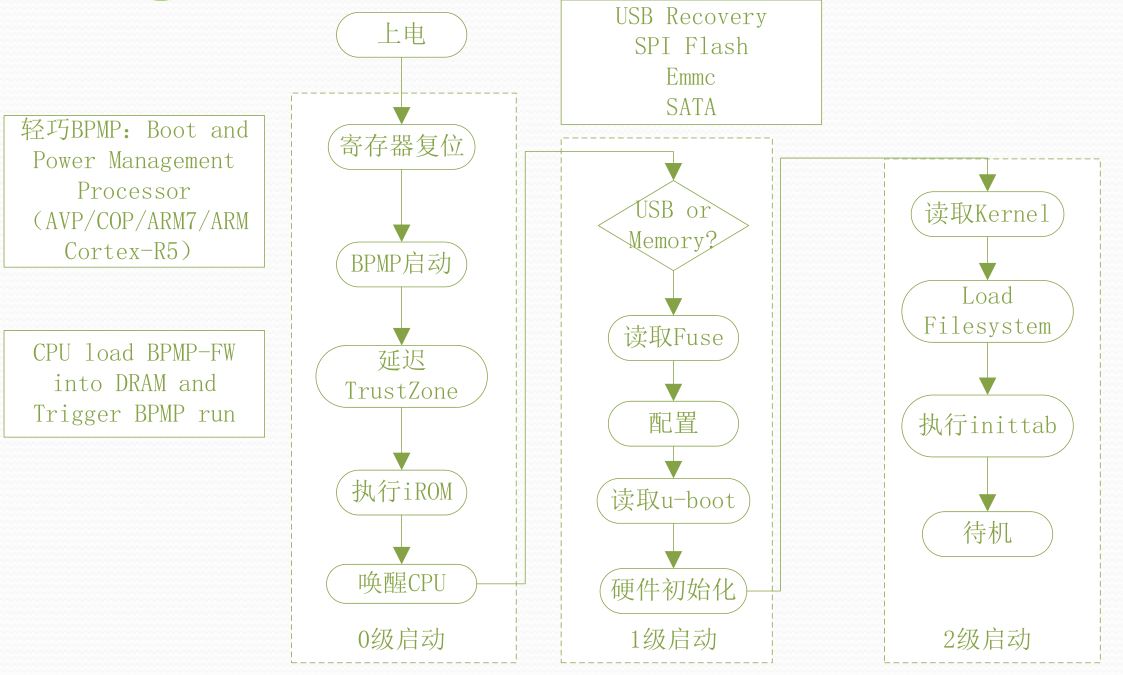

四、Tegra工作原理與軟體架構

1、Tegra 工作原理

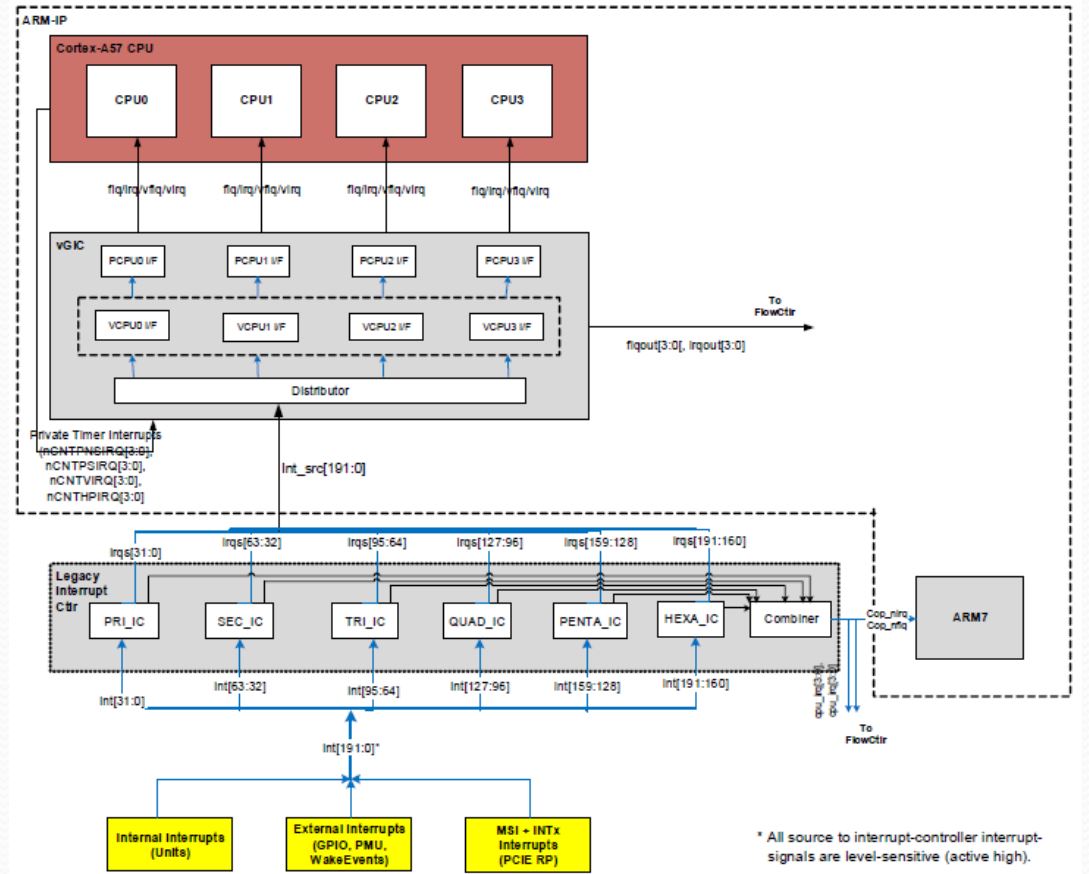

2、Tegra中斷控制

(1)一共有0-192號全域性中斷,由六個中斷控制器分別管理;

(2)TX1中斷控制器分為兩類:GIC400與LIC;

(3)GIC400是ARM Cortex-A57 的中斷控制器;

(4)LIC是屬於輕量級BPMP處理器的中斷控制器;

(5)任何處理器都可以傳送一個軟體中斷給其它一個或多個處理器(包括自身),但是IPI中斷志限於A57之間(包括自身);

(6)每個ARM處理器都有兩個引腳來接收IRQ和FIQ中斷,因為低電平觸發,因此命名nFIQ和nIRQ;

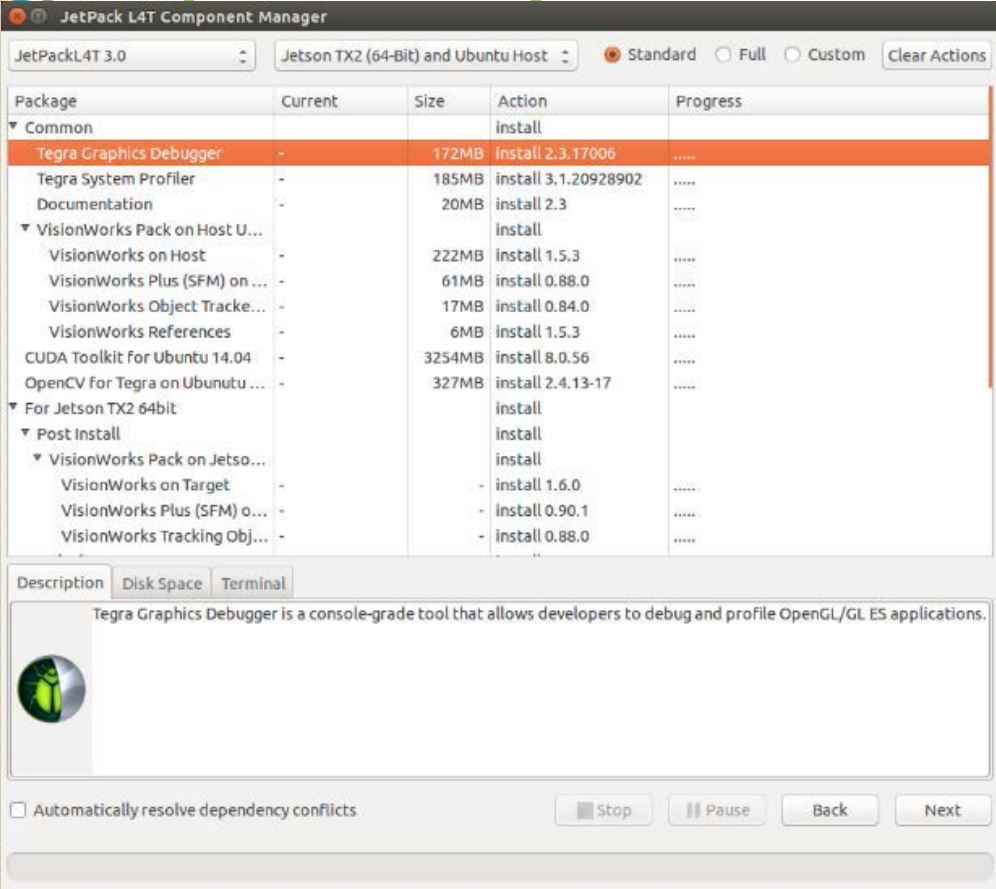

3、Component 軟體結構

(1)OS Images:JetPack包含來自Ubuntu的樣例檔案系統;

(2)Libraries:CUDA Toolkit(Linux下CUDA開發工具鏈)、TensorRT and cuDNN(高效能深度學習應用)、VisionWorks and Opencv(視覺計算應用);

(3)Developer Tools:Tegra Graphics Debugger(除錯OpenGL控制檯級別地 工程)、Tegra System Profiler(系統除錯跟蹤分析器,提高CPU效率)、PerfKit(提供訪問GPU效能統計)、Samples(NVIDIA GameWorks Vulkan 以及 OpenGL 範例)。

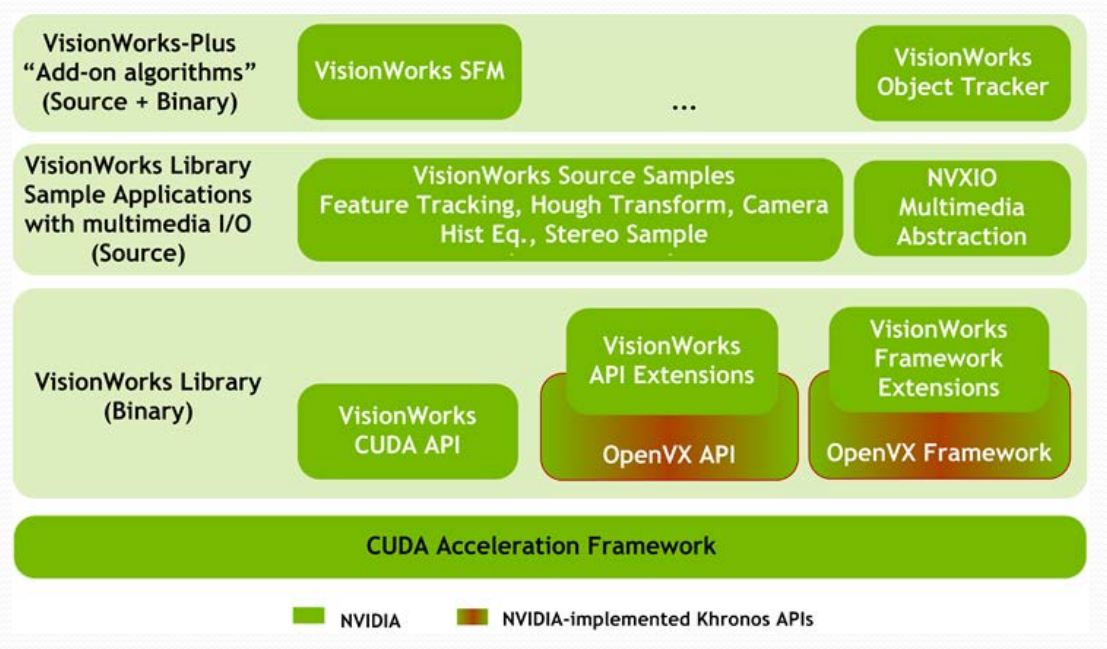

4、VisionWorks 軟體結構

五、Jetson 開發注意事項

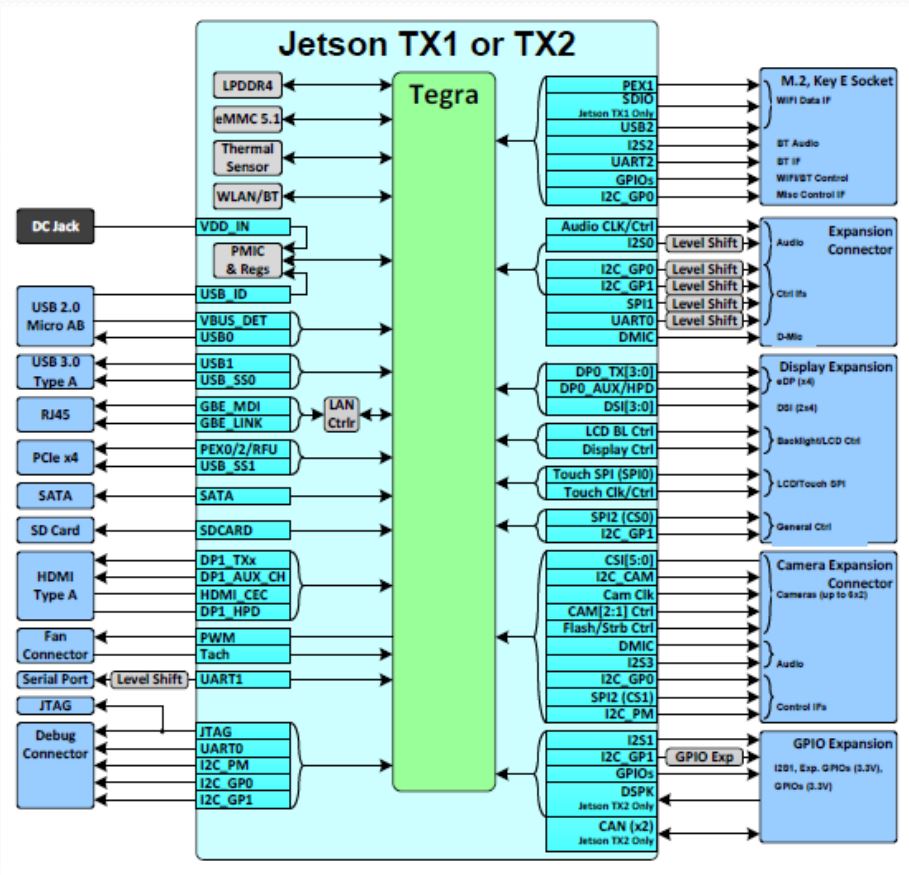

1、Jetson 功能概覽

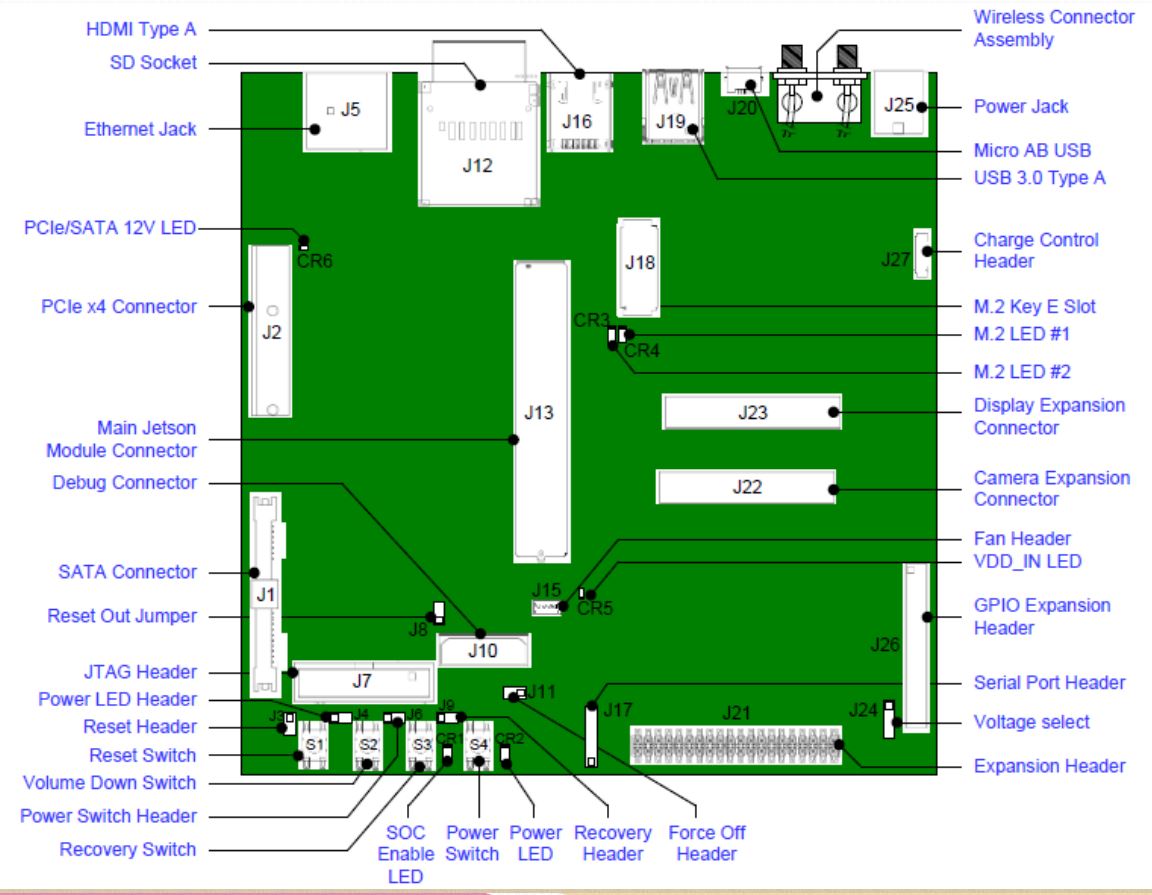

2、Jetson功能佈局

3、Jetson注意事項

(1)0-50℃溫度範圍內工作;

(2)不同使用者的eMMC、DRAM廠商型號可能不同;

(3)SATA不支援熱插拔;

(4)除了IIC_GPI是3.3V以外,其它的IIC介面都是1.8V介面;

(5)TX1生命期(EOL)至2021年1月(商業級);

(6)Jetson TX1只有四核A57,沒有A53;

(7)上電後風扇不轉,自動風扇調速;

(8)預設沒安裝系統,新的模組上電後無任何反應。

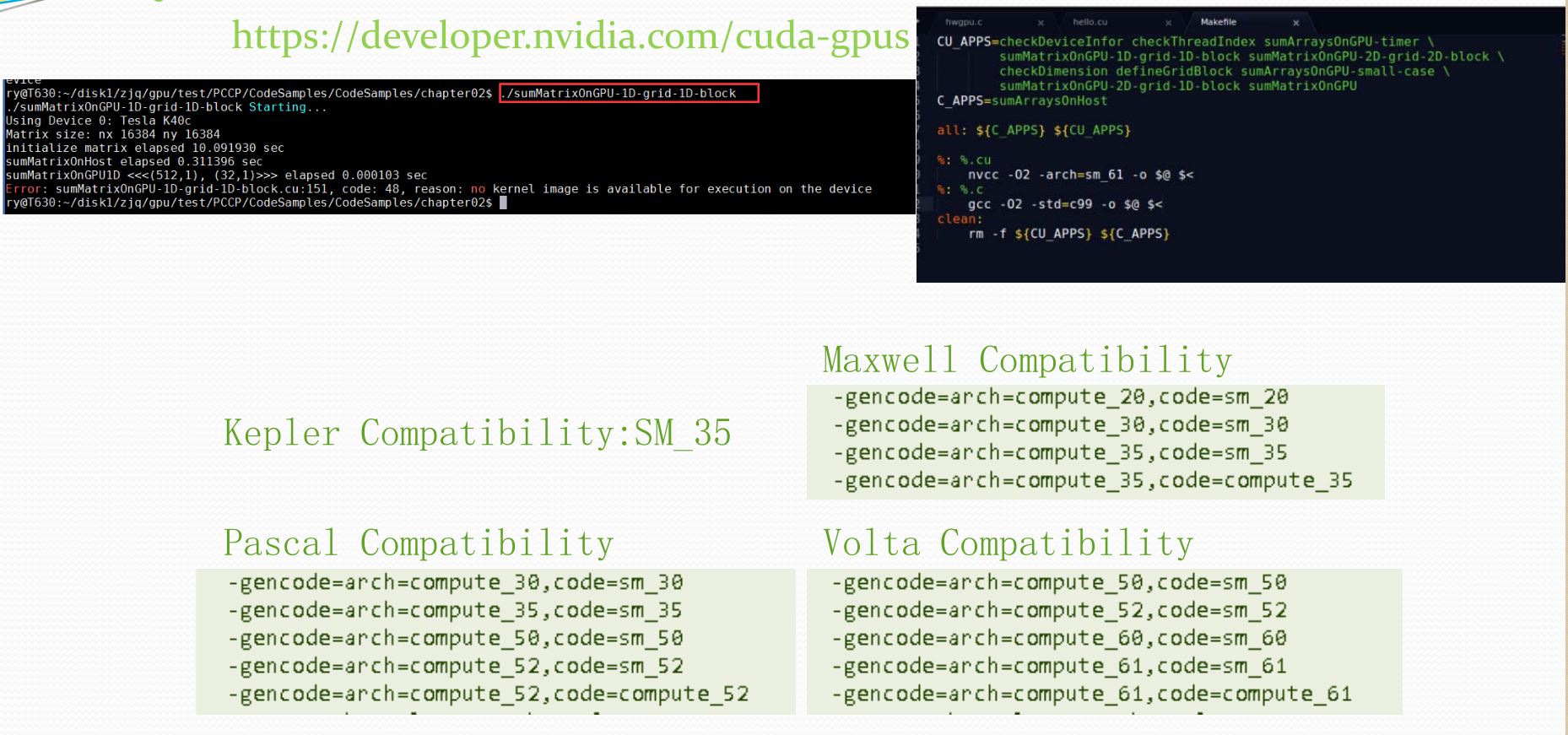

4、CUDA開發注意事項

5、Jetson 開發注意事項

致謝

1、《Jetson開發者入門之Tegra架構解析》

全文轉自:https://blog.csdn.net/qq_38880380/article/details/79667765