FPGA筆試必會知識點1--數位電路基本知識

組合邏輯與時序邏輯

組合邏輯電路:任意時刻電路輸出的邏輯狀態僅僅取決於當時輸入的邏輯狀態,而與電路過去的工作狀態無關。

時序邏輯電路:任意時刻電路輸出的邏輯狀態不僅取決於當時輸入的邏輯狀態,而與電路過去的工作狀態有關。

在電路的結構上,時序邏輯電路肯定包含有儲存電路,而且輸出一定與儲存電路的狀態有關。

COMS與TTL電平

常用邏輯電平:12V,5V,3.3V;TTL和CMOS不可以直接互連,由於TTL是在0.3-3.6V之間,而CMOS則是有在12V的有在5V的。CMOS輸出接到TTL是可以直接互連。TTL接到CMOS需要在輸出埠加一上拉電阻接到5V或者12V。

CMOS的高低電平分別為:Vih>=0.7VDD,Vil<=0.3VDD;Voh>=0.9VDD,Vol<=0.1VDD。

TTL的為:Vih>=2.0v,Vil<=0.8v;Voh>=2.4v,Vol<=0.4v。

用CMOS可直接驅動TTL。

TTL加上拉後可驅動CMOS。

時序邏輯電路的三大方程與設計

描述一個時序邏輯電路時,主要由驅動方程、狀態方程(由驅動方程代入時序器件的特性方程得到)、輸出方程這三大方程進行描述。

詳細過程參考《數位電子技術基本教程》P181—gary計數器的設計

在設計時序邏輯電路時可以採用以下流程:

- 找出電路的狀態轉換圖或者狀態轉換表;

- 從狀態轉換圖或者狀態轉換表中畫出次態與輸出的卡諾圖,並進行化簡;

- 由化簡的卡諾圖得出狀態方程,再由狀態方程得出驅動方程和輸出方程;

- 由驅動方程和輸出方程畫出電路結構圖;

- 檢查電路能否自啟動。

同步邏輯與非同步邏輯

同步邏輯:時鐘之間有固定的因果關係;

非同步邏輯:時鐘之間沒有固定的因果關係,電路中的觸發器的狀態不僅僅由時鐘決定;

同步電路與非同步電路

同步電路:電路中所有觸發器的時鐘輸入端都接至統一的時鐘訊號(並且同一觸發沿觸發),並且所有觸發器的輸出與統一的時鐘有效沿下保持同步輸出。

非同步電路:電路中所有觸發器的時鐘沒有統一的時鐘訊號,所有觸發器的輸出不與統一的時鐘有效沿下保持同步輸出。

同步設計的優點:

- 使用同步電路可以避免器件受溫度T,電壓V,工藝P的影響,避免毛刺/亞穩態,使設計更可靠,單板更穩定;

- 邏輯設計不依賴於每個邏輯器件的佈線延遲,有利於器件的移植;

- 同步電路可以很容易地組織流水線,提高晶片的執行速度,設計容易實現;

- 有利於靜態時序分析,驗證時序的效能;

非同步設計的缺點:

- 容易產生毛刺/亞穩態;

- 非同步邏輯時序的正確性依賴於每個邏輯器件的佈線延遲,不利於器件的移植;

- 不利於靜態時序分析,驗證時序效能;

同步復位與非同步復位

同步復位:復位訊號與時鐘訊號同時有效時進行復位動作;

優點:

- 保證100%的同步,綜合成同步時序電路;

- 同步復位僅在時鐘訊號有效沿時有效,可以消除毛刺

缺點:

- 在FPGA中,同步設計需要採用組合邏輯進行設計,增加邏輯資源;

- 需要進行復位訊號脈衝展寬,保證復位訊號時間足夠長,以保證所有觸發器都能有效復位;

- 必須需要時鐘訊號才能完成復位,當電路存在門控時鐘或使能時鐘時,可能出現復位訊號有效而時鐘訊號被禁止;

非同步復位:只要復位訊號有效就進行復位動作,與時鐘訊號無關;

優點:

- 復位動作與時鐘無關;

- 在FPGA內部有專用的GSR資源,使復位訊號的偏斜最小,無需組合邏輯,節省邏輯資源;

缺點:

- 當復位訊號撤除時,可能和時鐘訊號有效沿同時有效,容易造成觸發器出現亞穩態;

- 非同步復位對毛刺敏感,當復位訊號出現毛刺時,容易造成虛假復位;

- 進行STA分析時比較困難;

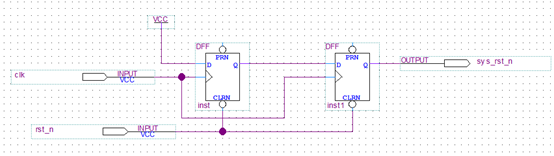

建議採用的復位電路:分散式非同步復位同步方法,將非同步復位同步電路放在每個模組的復位訊號輸入端。

復位毛刺的消除:採用等價與門,對復位訊號和經過延遲的復位訊號進行相與操作,完成毛刺的濾除。

競爭與冒險

組合邏輯電路的競爭冒險

競爭與冒險:組合電路中由於訊號到某一電路節點的時間不一致或者輸入訊號的電平往相反的方向變化叫競爭,由於競爭現像導致毛刺的產生稱為冒險。

競爭不一定導致冒險:當組合邏輯器件採用的工藝比較好,邏輯器件的速度快,由於競爭導致的毛刺現像很快就被消除掉。

時序邏輯電路的競爭冒險

由於時序邏輯電路主要由兩部分組成:組合電路和儲存電路,所以時序邏輯電路的競爭冒險也分為兩種:一種為組合邏輯電路的競爭冒險引起,其由於競爭冒險產生的輸出脈衝噪聲不僅影響整個電路的輸出,還影響儲存電路產生誤動作;另一種由儲存電路的觸發器的輸入訊號和時鐘訊號在狀態變化時配合不當(不滿足建立時間和保持時間)引起,可能引起電路產生誤動作。

競爭與冒險的消除

- 添加布爾式消去項(卡諾圖、公式進行化簡);

- 輸出端新增RC電容濾波;

- 使用使能/選通訊號;

- 採用gary碼或者獨熱碼;

亞穩態

亞穩態:觸發器無法在某個規定的時間內達到一個確認的狀態;

亞穩態的消除:

- 單訊號時採用兩級同步暫存器;

- 降低時鐘頻率;

- 用反應更快的觸發器;

- 用邊沿快速變化的時鐘訊號;

阻塞與非阻塞

參考《Verilog數字系統設計教程》

阻塞

邏輯模式:wire線型,由此在某一個模組中進行賦值操作,需要綜合器進行邏輯模式的化簡。如b=a;b的值在賦值語句執行完成之後就立刻改變。

賦值時先計算右邊部分的值,這時不允許其他的賦值語句的干擾,即其他賦值語句不進行賦值操作(區別於非阻塞的地方),只有完成將右邊的值賦到左邊,才開始下一條的賦值語句的執行。

非阻塞

邏輯模式:reg暫存器型,由此在某一個模組中進行賦值操作,採用暫存器對賦值進行寄存。

賦值時先計算右邊部分的值,這時允許其他的賦值語句的同時進行(區別於非阻塞的地方),所以整個模組的所有賦值語句同時計算右邊的值,然後又同時將計算出的值賦到左邊。

所以在某一模組中,上面語句所賦的值不能立刻就為下面的語句所使用。模組結束後,才完成賦值操作,所賦的值是上一次賦值所得到的。

阻塞與非阻塞的區別

常用編碼

Gray碼

Gray碼:任何兩個相鄰的程式碼只有一位的狀態不同。

優點:

- 任何兩個相鄰的程式碼只有一位的狀態不同,可以減少競爭冒險的發生;

- 翻轉次數減少,速度快,可以降低功耗;

缺點:

(1)佔用較多的組合邏輯;

獨熱碼

獨熱碼:有多少個狀態就有多少位元,而且只有一個位元為1,其他全為0的一種碼制。

優點:one-hot 編碼的最大優勢在於狀態比較時僅僅需要比較一個bit,一定程度上從而簡化了比較邏輯,減少了毛刺產生的概率。

缺點:佔用較多的觸發器(可以利用FPGA內部觸發器資源豐富的特點);

二進位制碼

二進位制碼:採用二進位制格式進行編碼的碼。

優點:

(1)採用組合邏輯進行設計,節省觸發器資源;

缺點:

- 容易造成競爭冒險的發生;

- 佔用組合邏輯,延遲大,速度慢;

Johnson碼

Johnson counter也叫扭環計數器,是把n位移位暫存器的序列(高位bit)輸出取反,反饋到序列的輸入端(低位bit),構成具有2n種狀態的計數器,相鄰位只有1bit的不同,可以用於實現跨時域的編碼操作,避免亞穩態的問題,速度快,缺點就是佔用觸發器。

000à001à011à111à110à100à000à……..

Moore型狀態機和mealy型狀態機

狀態機一般分為三種類型:

- Moore型狀態機:下一狀態/輸出只由當前狀態決定,即次態=f(現狀),輸出=f(現狀);

- Mealy型狀態機:下一狀態/輸出不但與當前狀態有關,還與當前輸入值有關,即次態=f(現狀,輸入),輸出=f(現狀,輸入);

-

混合型狀態機

Moore型狀態機的輸出訊號是直接由當前狀態暫存器譯碼得到,相比mealy要多等一個時鐘週期,而Mealy型狀態機則是以現時的輸入訊號結合即將變成次態的現態,編碼成輸出訊號。

鎖存器、觸發器、暫存器

鎖存器:電平敏感器件,電平觸發,組合邏輯器件;

觸發器:邊沿敏感器件,邊沿觸發,時序邏輯器件;

暫存器:儲存二值資訊程式碼,無論使用電平觸發的觸發器還是使用邊沿觸發的觸發器都可以組成暫存器。

可程式設計邏輯器件型別

PLA(可程式設計邏輯陣列)、

PAL(可程式設計陣列邏輯)、

GAL(通用邏輯陣列)、

CPLD(複雜可程式設計邏輯器件)、

FPGA(現場可程式設計邏輯器件);

PLD與ASIC

PLD優點:配置靈活,整合度高可滿足一般的數字系統設計,開發週期短,設計成本低;

缺點:相比ASIC體積大,功耗高,成本高;

ASIC優點:批量生產時相比PLD成本低,功耗低,可靠性高,效能高,成本低;

缺點:功能固定,後期無法修改,靈活性差,開發週期長,設計成本高;

SoC

片上系統,將微處理器、模擬IP核、數字IP核和儲存器整合在單一晶片上。

關鍵技術:匯流排架構技術、IP核可複用技術、軟硬體協同設計技術,SoC驗證技術、可測性技術、低功耗技術等。

儲存器

SRAM,FALSH, MEMORY,DRAM,SSRAM及SDRAM的區別?

SRAM:靜態隨機儲存器,存取速度快,但容量小,掉電後資料會丟失,不像DRAM 需要不停的REFRESH,製造成本較高,整合度低,通常用來作為快取(CACHE) 記憶體使用。

FLASH:快閃記憶體,存取速度慢,容量大,掉電後資料不會丟失。

NAND FLASH用於資料儲存,廣泛用於多媒體移動裝置;

NOR FLASH用於程式儲存。

DRAM:動態隨機儲存器,必須不斷的重新的加強(REFRESHED) 電位差量,否則電位差將降低至無法有足夠的能量表現每一個記憶單位處於何種狀態。價格比SRAM便宜,但訪問速度較慢,耗電量較大,常用作計算機的記憶體使用,整合度高。

SSRAM:即同步靜態隨機存取儲存器。對於SSRAM的所有訪問都在時鐘的上升/下降沿啟動。地址、資料輸入和其它控制訊號均於時鍾訊號相關。

SDRAM:即同步動態隨機存取儲存器。

數字IC設計流程

1、演算法設計。設計和優化晶片鍾所使用的演算法。這一階段一般使用高階程式語言(如C/C++),利用演算法級建模和模擬工具(如MATLAB,SPW)進行浮點和定點的模擬,進而對演算法進行評估和優化。

3、RTL設計(程式碼輸入)。使用HDL語言完成對設計實體的RTL級描述。這一階段使用VHDL和Verilog HDL語言的輸入工具編寫程式碼。

5、綜合。從RTL程式碼生成描述實際電路的門級網表文件。

7、佈局佈線。後端設計對綜合產生的門級網表進行佈局規劃(Floorplanning)、佈局(Placement)、佈線(Routing),生成生產用的版圖。

9、版圖後驗證。根據後端設計後取得的新的延時資訊,再次驗證設計是否能夠實現所有的功能和效能指標。

11、 晶片測試。對製造好的晶片進行測試,檢測生產中產生的缺陷和問題。