CMOS 影象感測器簡介(1):畫素結構

隨著工藝的發展,CMOS影象感測器的效能已經趕上或超越CCD,再加上CMOS影象感測器在工藝上能很大程度與傳統CMOS晶片相容,它已經成為相機的主流感測器型別。由於只能硬體的迅猛發展,很多應用場景都將碰到CMOS感測器,因此本文從基礎出發,介紹CMOS影象感測器的畫素結構。

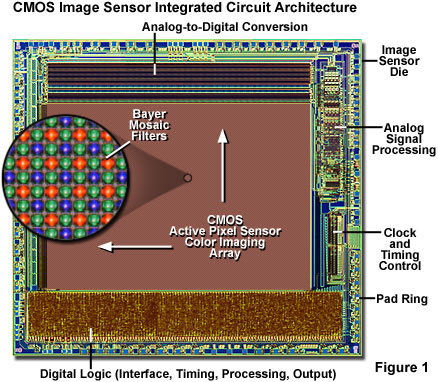

1.影象感測器整體架構

CMOS影象感測器本質是一塊晶片,主要包括:感光區陣列(Bayer陣列,或叫畫素陣列)、時序控制、模擬訊號處理以及模數轉換等模組(如圖1)。其中,各模組的作用分別為:

- 畫素陣列:完成光電轉換,將光子轉換為電子。

- 時序控制:控制電訊號的讀出、傳遞。

- 模擬訊號處理(ADC):對訊號去噪。(如用CDS去除reset noise、fpn等)

圖1.1 CMOS感測器示例

其中,畫素陣列佔整個晶片的面積最大,畫素陣列是由一個個畫素組成,它對應到我們看到每張圖片中的每個畫素。每個畫素包括感光區和讀出電路(後面小節會詳細討論),每個畫素的訊號經由模擬訊號處理後,交由ADC進行模數轉換後即可輸出到數字處理模組。畫素陣列的訊號讀出如下(參考圖1.2):

- 每個畫素在進行reset,進行曝光。

- 行掃描暫存器,一行一行的啟用畫素陣列中的行選址電晶體。

- 列掃描暫存器,對於每一行畫素,一個個的啟用畫素的列選址電晶體。

- 讀出訊號,並進行放大。

2.影象感測器畫素結構

CMOS感測器上的主要部件是畫素陣列,這是其與傳統晶片的主要區別。每個畫素的功能是將感受到的光轉換為電訊號,通過讀出電路轉為數字化訊號,從而完成現實場景數字化的過程。畫素陣列中的每個畫素結構是一樣的,如圖2.1是典型的前照式畫素結構,其主要結構包括:

- On-chip-lens:該結構可以理解為在感光元件上覆蓋的一層微透鏡陣列,它用來將光線聚集在畫素感光區的開口上。可以增加光電轉化效率,減少相鄰畫素之間的光訊號串擾。

- Color filter:該結構是一個濾光片,包括紅/綠/藍三種,分別只能透過紅色、綠色、藍色對應波長的光線。該濾光片結構的存在,使得每個畫素只能感應一種顏色,另外的兩種顏色分量需要通過相鄰畫素插值得到,即demosaic演算法。

- Metal wiring:可以為金屬排線,用於讀出感光區的訊號(其實就是畫素內部的讀出電路)。

- Photodiode:即光電訊號轉換器,其轉換出的電訊號會經過金屬排線讀出。

圖2.1 畫素結構

其中,Photodiode和Metal wiring對CMOS感測器的效能影響最大(比如光電轉換效率,讀出噪聲等),也是目前主流感測器廠商注重提高的工藝。為了方便敘述,下面將Photodiode和Metal wiring簡稱為Pixel(即包括每個畫素內的感光區域和讀出電路)。

2.1 Passive Pixel

最簡單的Pixel結構只有一個PN接面作為photodiode感光,以及一個與它相連的reset電晶體作為一個開關(如圖2.2)。它的工作方式如下:

- 在開始曝光之前,該畫素的行選擇地址會上電(圖中未畫出),從而RS會啟用,連通PN接面與column bus。同時列選擇器會上電,此時PN接面會被載入高反向電壓(例如3.3 V)。在Reset(即PN接面內電子空穴對達到平衡)完成後,RS將會被停止啟用,停止PN接面與column bus的連通。

- 在曝光時間內,PN接面內的矽在吸收光線後,會產生電子-空穴對。由於PN接面內電場的影響,電子-空穴對會分成兩個電荷載體,電子會流向PN接面的端,空穴會流向PN接面的p-substrate。因此,經過曝光後的的PN接面,其反向電壓會降低。

- 在曝光結束後,RS會被再次啟用,讀出電路會測量PN接面內的電壓,該電壓與原反向電壓之間的差,就是PN接面接受到的光訊號。(在主流sensor設計中,電壓差與光強成正比關係)

- 在讀出感光訊號後,會對PN接面進行再次reset,準備下次曝光。

圖2.2 畫素結構

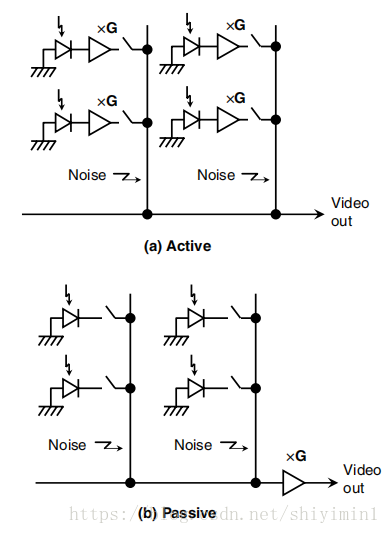

這種畫素結構,其讀出電路完全位於畫素外面,稱為Passive Pixel。Passive Pixel的讀出電路簡單,整個Pixel的面積可以大部分用於構造PN接面,所以其滿阱電容一般會高於其他結構。但是,由於其訊號的讀出電路位於Pixel外面,它受到電路噪聲的影響比Active Pixel(下一節會介紹)大。Passivel Pixel噪聲較大有2個主要原因:

- 相對讀出電路上的寄生電容,PN接面的電容相對較小。代表其訊號的電壓差相對較小,這導致其對電路噪聲很敏感。

- 如圖2.3(b),PN接面的訊號,先經過讀出電路,才進行放大。這種情況,注入到讀出訊號的噪聲會隨著訊號一起放大。

圖2.3 Active Pixel和Passive Pixel噪聲注入對比

2.2 Active Pixel

Active Pixel指的是在畫素內部有訊號讀出電路和放大電路的畫素結構。如圖2.3(a),訊號傳出Pixel之前,就已經讀出並放大,這減少了讀出訊號對噪聲的敏感性。隨著工藝的發展,基於Active Pixel的CMOS感測器在暗電流和噪聲表現上有很大提升,Active Pixel結構隨之成為了CMOS感測器的主流設計。

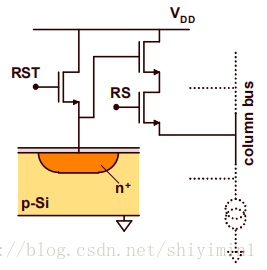

圖2.4展示了基於PN接面的Active Pixel結構,也成為3T畫素結構(每個畫素包含3個三極體)。在這種結構中,每個畫素包含一個PN接面作為感光元件,一個復位三極體RST,一個行選擇器RS,以及一個訊號放大器SF。其工作方式和Passive Pixel類似:

- 復位。給PN接面載入反向電壓,或者說啟用RST給PN接面進行復位。復位完成後,不再導通RST。

- 曝光。和在Passive Pixel中一樣,光子打到PN接面及矽基,被吸收後產生電子-空穴對。這些電子空穴對通過電場移動後,減小PN接面上的反向電壓。

- 讀出。在曝光完成後,RS會被啟用,PN接面中的訊號經過運放SF放大後,讀出到column bus。

- 迴圈。讀出訊號後,重新復位,曝光,讀出,不斷的輸出影象訊號。

圖2.4 PN接面畫素結構

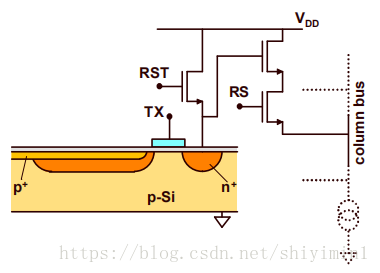

基於PN接面的Active Pixel流行與90年代中期,它解決了很多噪聲問題。但是由PN接面復位引入的kTC噪聲,並沒有得到解決。為了解決復位kTC噪聲,減小暗電流,引入了基於PPD結構(Pinned Photodiode Pixel)的畫素結構。PPD pixel包括一個PPD的感光區,以及4個電晶體,所以也稱為4T畫素結構(如圖2.5)。PPD的出現,是CMOS效能的巨大突破,它允許相關雙取樣(CDS)電路的引入,消除了復位引入的kTC噪聲,運放器引入的1/f噪聲和offset噪聲。

仔細對比圖2.4和2.5,發現示意圖右邊的結構基本一致。但他們的功能有明顯差異,對於PPD,右邊部分電路只是訊號讀出電路。讀出電路與光電轉換結構通過TX完全隔開,這樣可以將光感區的設計和讀出電路完全隔離開,有利於各種訊號處理電路的引入(如CDS,DDS等)。另外,PPD感光區的設計採用的是p-n-p結構,減小了暗電流。PPD畫素的工作方式如下: 1. 曝光。光照射產生的電子-空穴對會因PPD電場的存在而分開,電子移向n區,空穴移向p區。 2. 復位。在曝光結束時,啟用RST,將讀出區(區)復位到高電平。 3. 復位電平讀出。復位完成後,讀出復位電平,其中包含運放的offset噪聲,1/f噪聲以及復位引入的kTC噪聲,將讀出的訊號儲存在第一個電容中。 4. 電荷轉移。啟用TX,將電荷從感光區完全轉移到區用於讀出,這裡的機制類似於CCD中的電荷轉移。 5. 訊號電平讀出。接下來,將區的電壓訊號讀出到第二個電容。這裡的訊號包括:光電轉換產生的訊號,運放產生的offset,1/f噪聲以及復位引入的kTC噪聲 6. 訊號輸出。將儲存在兩個電容中的訊號相減(如採用CDS,即可消除Pixel中的主要噪聲),得到的訊號在經過模擬放大,然後經過ADC取樣,即可進行數字化訊號輸出。

PPD畫素結構有如下優點: - 讀出結構(區)的kTC噪聲完全被CDS消除。 - 運放器的offset和1/f噪聲,都會因CDS得到明顯改善。 - 感光結構因復位引起的kTC噪聲,由於PPD電荷的全轉移,變的不再存在。 - 光敏感度,它直接取決於耗盡區的寬度,由於PPD的耗盡區一直延伸到近介面,PPD的光感度更高。 - 由於p-n-p的雙結結構,PPD的電容更高,能產生更高的動態範圍。 - 由於介面由一層覆蓋,減小了暗電流。

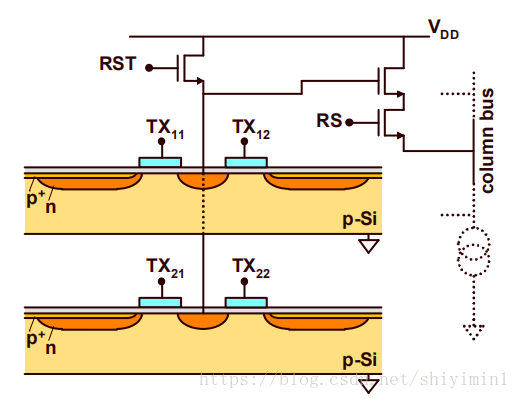

由於PPD畫素結構在暗電流和噪聲方面的優異表現,近年來市面上的CMOS感測器都是以PPD結構為主。但是,PPD結構有4個電晶體,有的設計甚至有5個,這大大降低了畫素的填充因子(即感光區佔整個像素面積的比值),這會影響感測器的光電轉換效率,進而影響感測器的噪聲表現。在PPD結構中,畫素的感光區和讀出電路由TX電晶體隔開,相鄰畫素減可以共用讀出電路(如圖2.6)。圖2.6所示的2x2畫素共享讀出電路,一共有7個電晶體,平均一個畫素1.75個電晶體。這樣可以大大減少每個畫素中讀出電路佔用的面積,可以提高填充因子,這樣可以使得像素面積更小(比如1微米)。然而,由於這2x2個畫素的結構不再一致,會導致固定模式噪聲的出現(FPN),這需要在後續影象處理中消除。

3.總結

本文主要介紹了以下三個方面:

- CMOS影象感測器的整體架構。闡明瞭其基本模組:畫素整列、讀出電路、模擬訊號處理以及模數轉換模組。

- CMOS影象感測器的PN接面畫素結構。這裡主要介紹了CMOS在發展初期的以中畫素結構,但是它存在高暗電流和噪聲的問題,在90年代中期始終無法與CCD在高階成像領域競爭。

- CMOS影象感測器的PPD畫素結構。介紹了PPD畫素中感光區域與讀出電路的分離,從而使得CDS能用於影象訊號的讀出,引發了CMOS影象感測器的變革。這大大減少了CMOS感測器的噪聲和暗電流,使得CMOS感測器趕上並超越CCD,成為相機感測器的主流。

- 介紹了PPD畫素結構共享讀出電路的方式。由於PPD讀出電路複雜,減小了畫素的感光區填充因子,引入了讀出電路共享方式。該技術能夠進一步減少畫素的面積,目前已知的有1微米大小的畫素。

文中主要介紹了畫素結構的基礎,後續會繼續更新一些CMOS感測器的知識。

參考文獻

[2] Junichi Nakamura etc. Image Sensors and Signal Processing for Digital Still Cameras. 2006. Taylor & Francis