DDR(四)ddr2 工作時序與原理

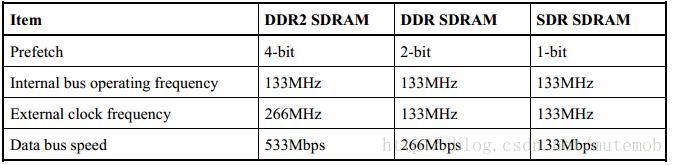

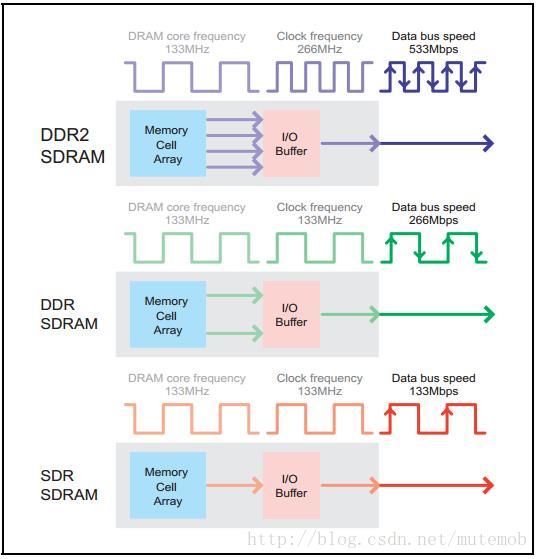

1.4-bit Prefetch

直接上一個表,看看DDR2的三個頻率的關係,下圖是內部時鐘均為133MHz的DDR2/DDR/SDRAM的比較,由圖可以看到,相比於DDR,DDR2由於是4-bit Prefetch,外部時鐘是內部匯流排時鐘的2倍,而DDR和SDRAM中,這兩個時鐘頻率相等

2. DDR-Ⅱ的新操作與新時序設計

2.1片外驅動調校(OCD,Off-Chip Driver)

DDR-Ⅱ記憶體在開機時也會有初始化過程,同時在 EMRS 中加入了新設定選項,由於大同小異,在此就不多說了。在 EMRS 階段,DDR-Ⅱ加入了可選的 OCD 功能。

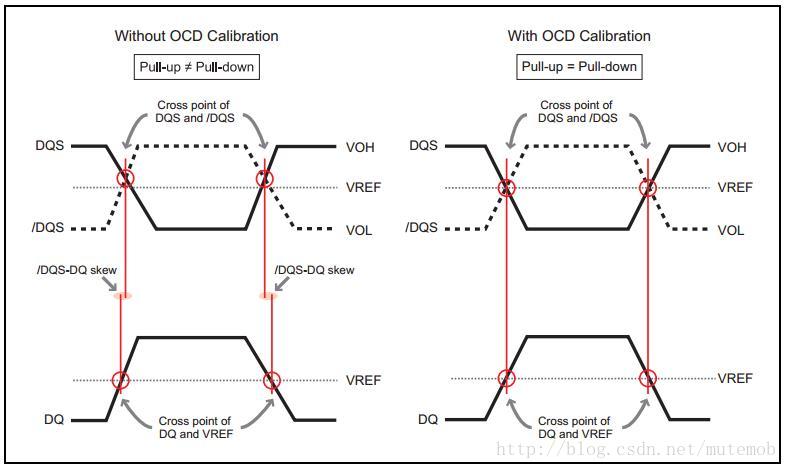

OCD 的主要用意在於調整 I/O 介面端的電壓,來補償上拉與下拉電阻值。目的是讓 DQS 與 DQ 資料訊號之間的偏差降低到最小。調校期間,分別測試 DQS 高電平/DQ 高電平,與 DQS 低電平/DQ 高電平時的同步情況,如果不滿足要求,則通過設定突發長度的地址線來傳送上拉/下拉電阻等級(加一檔或減一檔),直到測試合格才退出 OCD 操作。

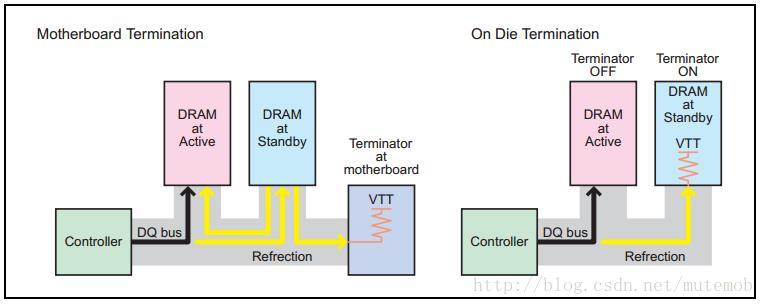

所謂的終結,就是讓訊號被電路的終端吸收掉,而不會在電路上形成反射,造成對後面訊號的影響。

在 DDR 時代,控制與資料訊號的終結在主機板上完成,每塊 DDR 主機板在 DIMM 槽的旁邊都會有一個終結電壓島的設計,它主要由一排終結電阻構成。長期以來,這個電壓島一直是 DDR 主機板設計上的一個難點。而 ODT 的出現,則將這個難點消滅了。ODT 將終結電阻從主機板上移植到了記憶體晶片內部,主機板上不在有終結電路。ODT 的功能與禁止由記憶體控制器控制,ODT 所終結的訊號包括 DQS、RDQS(為 8bit 位寬晶片增設的專用 DQS 讀取訊號,主要用來簡化一個模組中同時使用 4 與 8bit 位寬晶片時的控制設計)、DQ、DM 等。

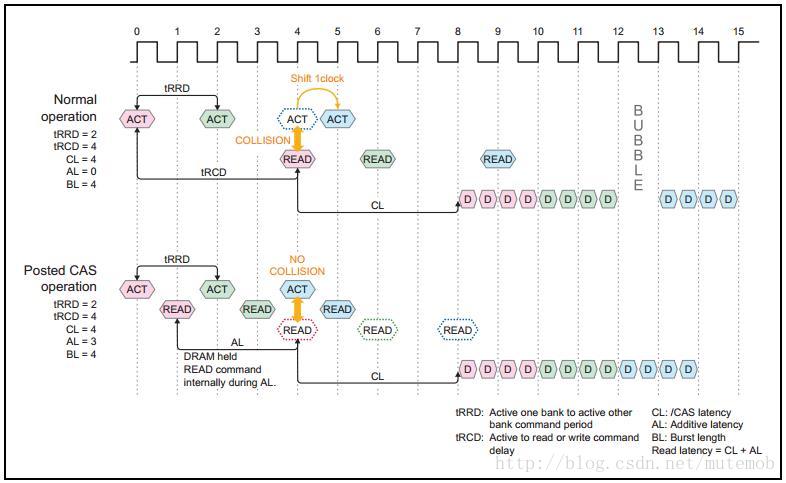

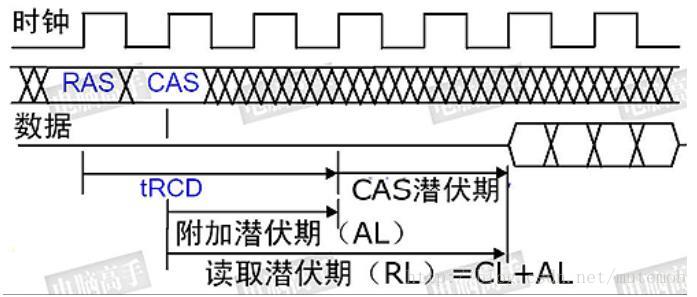

前置 CAS(Posted CAS)是為了解決 DDR 記憶體中指令衝突而設計的功能。它允許 CAS 訊號緊隨 RAS 傳送,相對於以往的 DDR 等於將 CAS 前置了。 這樣,地址線可以立刻空出來,便於後面的行有效命令發出,避免造成命令衝突而被迫延後的情況發生,但讀/寫操作並沒有因此而提前,仍有要保證有足夠的延遲/潛伏期,為此,DDR-Ⅱ引入了附加潛伏期的概念(AL,Additive Latency),與 CL 一樣,單位為時鐘週期數。AL+CL 被定義為讀取潛伏期(RL,Read Latency),相應的,DDR-Ⅱ還對寫入潛伏期(WL,Write Latency)制定了標準,WL是指從寫入命令發出到第一筆資料輸入的潛伏期,不要將它和 tDQSS 弄混了,後者是指 DQS 而不是資料。按規定,WL=RL-1,即 AL+CL-1。

至此,DDR2的來龍去脈全部分析完畢,現在可以開始開啟晶片手冊,開始分析原始碼了。