fpga學習之數碼管顯示

阿新 • • 發佈:2018-12-20

1、設計需求:

設計一個數碼管驅動電路,是數碼管能夠顯示任意六位數。

2、數碼管原理分析:

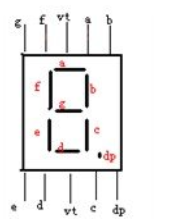

現在的數碼管基本都是八段式的,也就是說由八個發光二極體組成的。如圖一所示,這是單個數碼管的原理圖

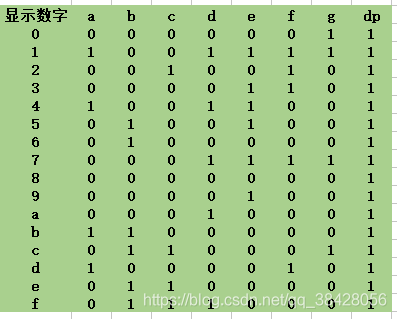

我們需要二極體顯示數字,只需要控制二極體的亮滅就行。以共陽極數碼管為例(給二極體低電平為點亮二極體),如圖二所示顯示數字與段選關係

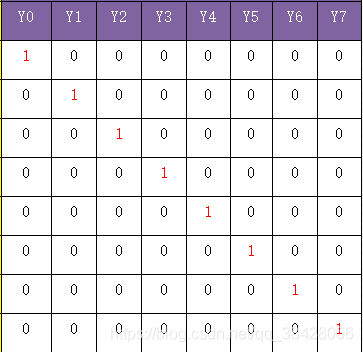

數碼管位選如圖三所示,Y0~Y7表示8位數碼管。1為數碼管有效

程式碼功能實現部分:

module seg_6(

Clk,

Rst_n,

En,

disp_data,

sel,

seg

);

input Clk; //50M

input Rst_n;

input En; //數碼管顯示使能,1使能,0關閉

input [23:0]disp_data;

output [5:0] sel;//數碼管位選(選擇當前要顯示的數碼管)

output reg [6:0] seg;//數碼管段選(當前要顯示的內容)

reg [14:0]divider_cnt;//25000-1

reg clk_1K;

reg [5:0]sel_r;

reg [3:0]data_tmp;//資料快取

// 分頻計數器計數模組

程式碼模擬部分

`timescale 1ns/1ns

`define clk_period 20

module seg_6_tb;

reg Clk; //50M

reg Rst_n;

reg En; //數碼管顯示使能,1使能,0關閉

reg [23:0]disp_data;

wire [5:0] sel;//數碼管位選(選擇當前要顯示的數碼管)

wire [6:0] seg;//數碼管段選(當前要顯示的內容)

seg_6 seg_6(

.Clk(Clk),

.Rst_n(Rst_n),

.En(En),

.disp_data(disp_data),

.sel(sel),

.seg(seg)

);

initial Clk = 1;

always#(`clk_period/2) Clk = ~Clk;

initial begin

Rst_n = 1'b0;

En = 1;

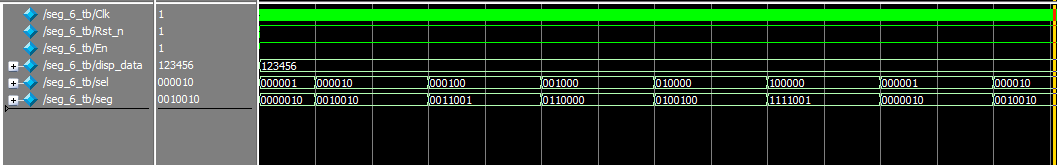

disp_data = 24'h123456;

#(`clk_period*20);

Rst_n = 1;

#(`clk_period*20);

#10000000;

disp_data = 24'h876543;

#10000000;

disp_data = 24'h89abcd;

#10000000;

$stop;

end

endmodule

模擬波形

大家在位選部分也可以使用狀態機來實現,歡迎大家來學習討論。