2.ARM晶片的時鐘體系

注:以下內容學習於韋東山老師arm裸機第一期視訊教程

一. 2440時鐘簡介

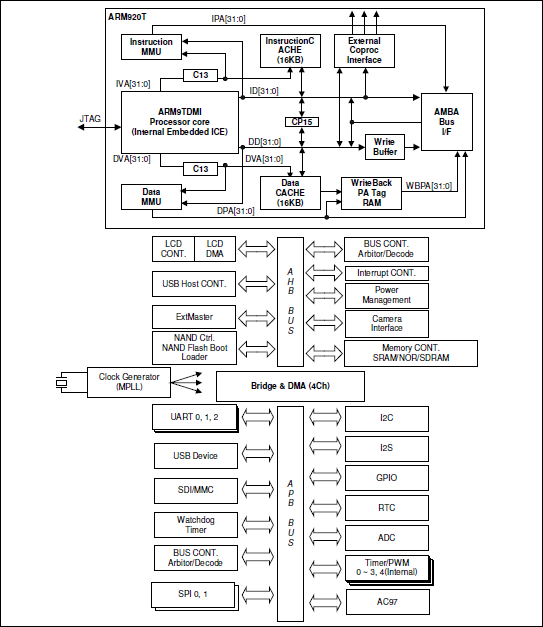

1.1 2440是一個SOC(system on chip)系統,不僅有很多CPU,還有很多外設,在2440晶片手冊有系統框架圖如下:

2440框架圖中,不僅有CPU,而且有很多外設,其中外設分為兩部分,一部分是AHB匯流排,一部分是APB匯流排

1.2 AHB匯流排

1.2.1 LCD控制器

1.2.2 USB控制器

1.2.3 NAND控制器

1.2.4 記憶體控制器

1.2.5 攝像頭介面

1.2.6 中斷控制器

1.2.7 電源管理等等

1.3 APB匯流排

1.3.1 UART

1.3.2 USB device

1.3.3 I2C

1.3.4 GPIO

1.3.5 RTC

1.3.6 ADC

1.3.7 定時器等等

1.4 因此引入了三個時鐘,FLCK,HCLK,PCLK

cpu工作與FCLK,最大工作頻率400MHZ

AHB匯流排工作於HCLK,最大工作頻率136MHZ

APB匯流排工作與PCLK,最大工作頻率68MHZ

二.時鐘的獲取

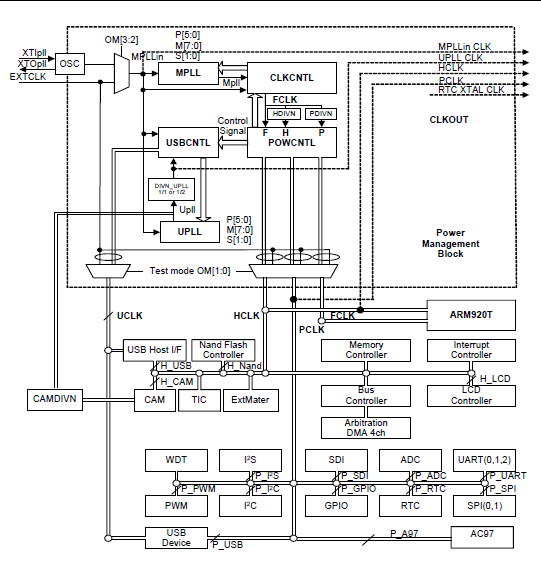

2.1 2440時鐘體系框圖如下

2.2 時鐘源的選擇

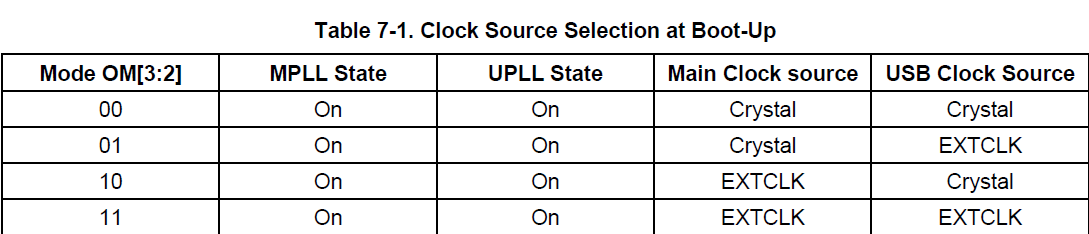

從圖中看出,時鐘源有兩個分別是外部晶振和引腳,通過OM[3:2]來選擇,模式選擇如下圖

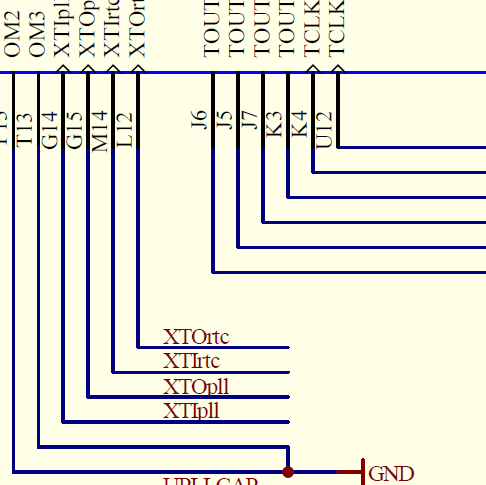

在2440的原理圖上,可以看到OM3,OM2都接到了GND上,因此會選擇使用外部晶振作為輸入

2.3 時鐘體系流程

12MHZ晶振通過MPLL鎖相環得到FLCK,CPU直接使用FCLK,FCLK通過PDIV分頻得到PCLK提供給APB總線上的裝置使用,

FCLK通過HDIV分頻得到HCLK提供給AHB總線上使用

12MHZ晶振也會經過UPLL鎖相環提供給USB使用

三.程式的編寫

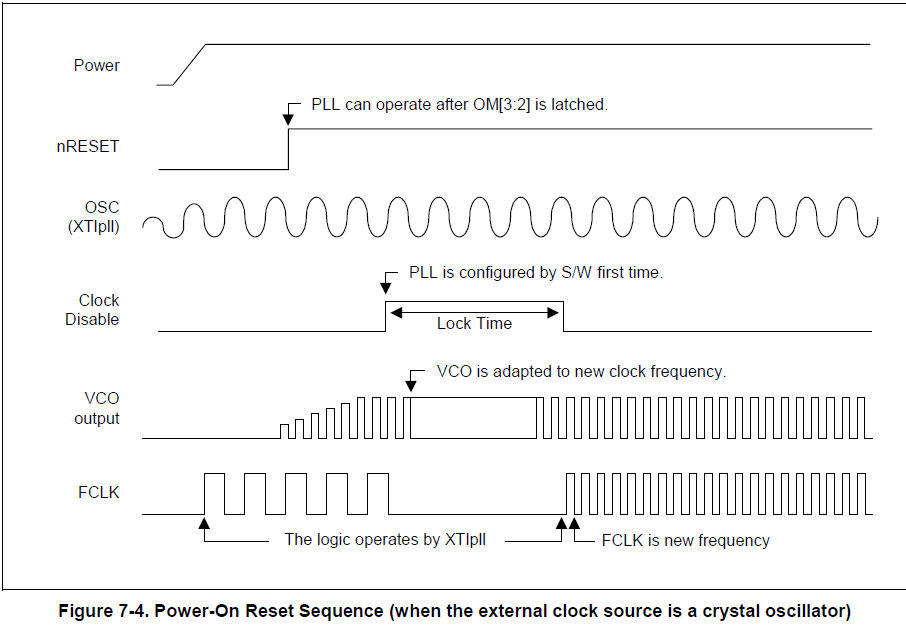

3.1 時序圖如下:

3.2 流程分析

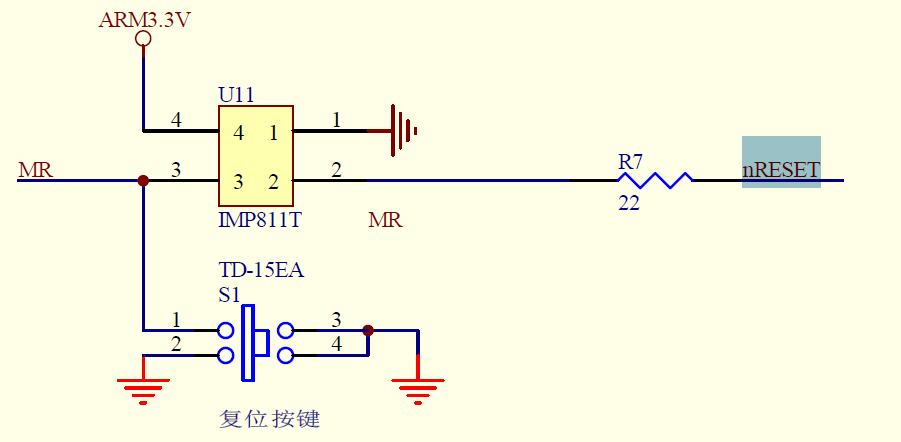

3.2.1 一上電,復位引腳會維持一段時間(等待電源穩定),通過復位晶片來維持,如下:

3.2.2 根據OM[3:2]的值FCLK等於晶振的12M

3.2.3 PLL鎖存OM[3:2]的值,同時CPU開始執行(復位引腳被拉高)

3.2.4 設定PLL

3.2.5 在CPU停止執行一段時間設定PLL

3.2.6 設定完成後FLCK等於PLL輸出的新的頻率

3.3 暫存器的設定(目的FCLK=400MZH, HCLK=100MZH, PCLK=50MHZ)

3.3.1 設定LOCKTIME暫存器,決定MPLL和UPLL的LOCKTIME

設定為預設值即可

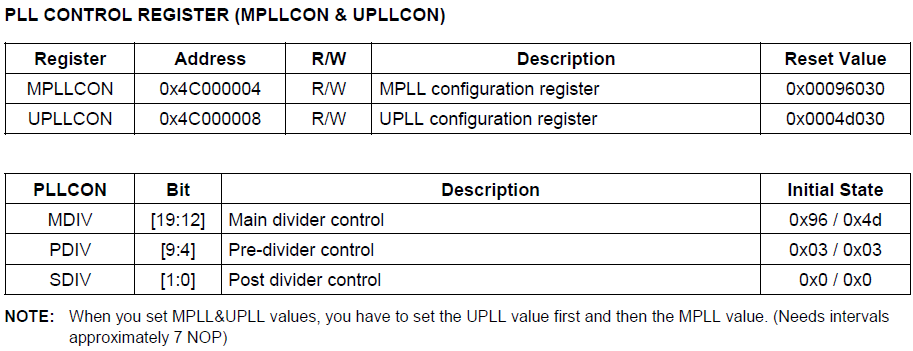

3.3.2 設定MPLLCON/UPLLCON暫存器,決定FCLKi,如下圖

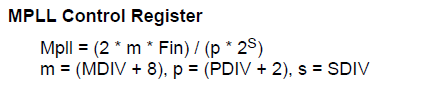

其中公式如下圖:

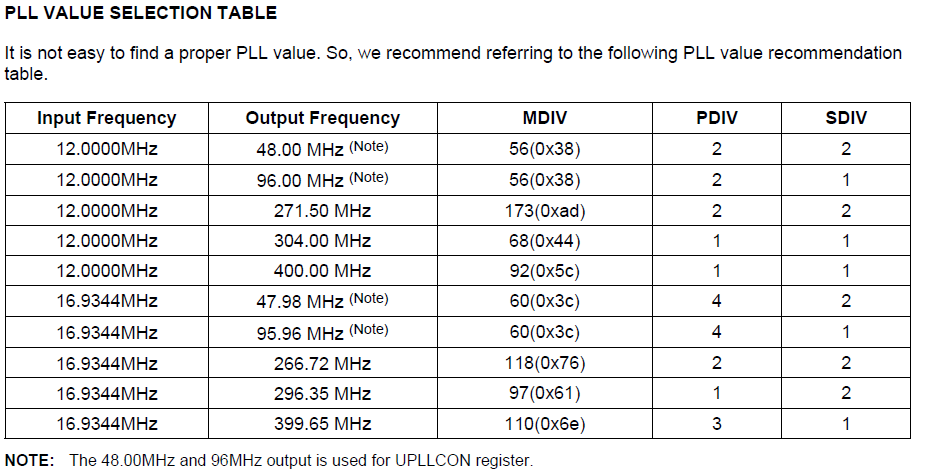

參考設定值如下,我們選擇MDIV=92, PDIV = 1, SDIV=1即可設定FCLK = 400MHZ:

MPLLCON = (92 << 12) | (1 << 4) | (1 << 0);

3.3.3 設定CLKCON暫存器(關掉用不到的裝置)

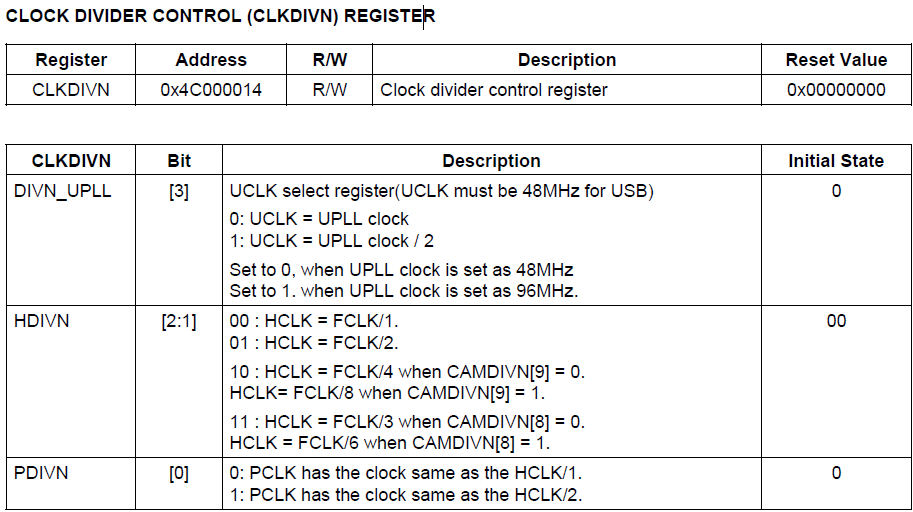

3.3.4 設定CLKDIVN暫存器,決定HCLK,PCLK,如下圖:

首先要設定bit[2:1]為10,這時HCLK=FCLK/4=100MHZ,但是需要CAMDIVN[9]=0(預設值就是0)

設定bit[0]為1,這時PCLK=HCLK/2=50MHZ

bit[3]取預設值

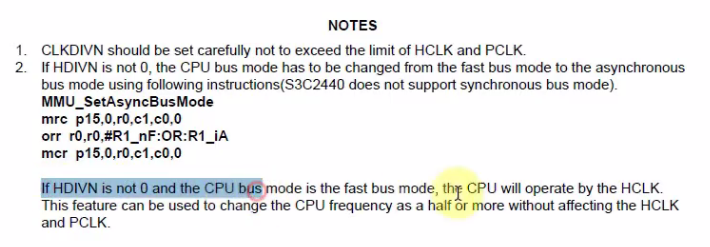

3.3.5 如果HDIVN不等於0,CPU必須設定為非同步模式,CPU會工作於HCLK,如下圖

.text

.global _start

_start:

/* 1.關閉看門狗 */

ldr r0, =0x53000000

ldr r1, =0

str r1, [r0]

/* 2.設定時鐘 */

/* 2.1 設定LOCKTIME(0x4C000000)=0xFFFFFFFF */

ldr r0, =0x4C000000

ldr r1, =0xFFFFFFFF

str r1, [r0]

/* 2.2 設定CLKDIVN(0x4C000014) = 0x5 FCLK : HCLK : PCLK = 400m : 100m : 50m*/

ldr r0, =0x4C000014

ldr r1, =0x5

str r1, [r0]

/* 2.3 設定CPU處於非同步模式 */

mrc p15,0,r0,c1,c0,0

orr r0,r0,#0xc0000000 /* #R1_nF:OR:R1_iA */

mcr p15,0,r0,c1,c0,0

/* 2.4 設定MPLLCON(0x4C000004)=(92<<12) | (1 << 4) | (1 << 0)

* m = MDIV + 8 = 100

* p = PDIV + 2 = 3

* s = SDIV = 1

* Mpll = (2 * m * Fin) / (p * 2 ^ s)

* = (2 * 100 * 12) / (3 * 2 ^ 1) = 400MHZ

*/

ldr r0, =0x4C000004

ldr r1, =(92<<12) | (1 << 4) | (1 << 0)

str r1, [r0]

/* 3.設定棧

* 自動分辨NOR啟動或者NAND啟動

* 向0地址寫入0,在讀出來,如果寫入則是NAND,否則是NOR

*/

ldr r0, =0

ldr r1, [r0] /* 讀出原來的值備份 */

str r0, [r0] /* 向0地址寫入0 */

ldr r2, [r0] /* 再次讀出來 */

cmp r1, r2

ldr sp, =0x40000000 + 4096 /* nor啟動 */

moveq sp, #4096 /* nand啟動 */

streq r1, [r0] /* 恢復原來的值 */

bl main

halt:

b halt

3.3.6 提高系統時鐘程式碼如下(FCLK=400MHZ,HCLK=100MHZ,PCLK=50MHZ):

---------------------

作者:qq_36521904

來源:CSDN

原文:https://blog.csdn.net/qq_36521904/article/details/80591417

版權宣告:本文為博主原創文章,轉載請附上博文連結!